IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... Gate Oxide Tunnelling Current (IG): Reduction of gate oxide thickness[3] results in an increase in the field across the oxide. The high electric field coupled with low oxide thickness results in tunnelling of electrons from substrate to gate and also from gate to substrate through the gate oxide, re ...

... Gate Oxide Tunnelling Current (IG): Reduction of gate oxide thickness[3] results in an increase in the field across the oxide. The high electric field coupled with low oxide thickness results in tunnelling of electrons from substrate to gate and also from gate to substrate through the gate oxide, re ...

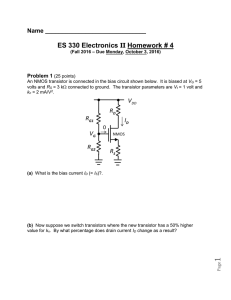

ECE 5411 CMOS Analog Integrated Circuit Design Sample Midterm 1 Name:

... (b) (5 points) Derive an exact expression for the output resistance of the cascode current source seen above. ...

... (b) (5 points) Derive an exact expression for the output resistance of the cascode current source seen above. ...

2015Su-CS61C-L09-sk-SDS

... N-type transistors pass weak 1’s (Vdd - Vth) N-type transistors pass strong 0’s (ground) Use N-type transistors only to pass 0’s (N for negative) Converse for P-type transistors: Pass weak 0s, strong 1s • Pass weak 0’s (Vth), strong 1’s (Vdd) • Use P-type transistors only to pass 1’s (P for positive ...

... N-type transistors pass weak 1’s (Vdd - Vth) N-type transistors pass strong 0’s (ground) Use N-type transistors only to pass 0’s (N for negative) Converse for P-type transistors: Pass weak 0s, strong 1s • Pass weak 0’s (Vth), strong 1’s (Vdd) • Use P-type transistors only to pass 1’s (P for positive ...

How can I reduce my standby power consumption?

... Common Causes There are a series of common causes for this behaviour, some more easily dealt with than others. Each one will be dealt with in turn, explaining the problem and offering a solution. Floating Inputs This is by far the most common cause of high power consumption. CMOS inputs consume very ...

... Common Causes There are a series of common causes for this behaviour, some more easily dealt with than others. Each one will be dealt with in turn, explaining the problem and offering a solution. Floating Inputs This is by far the most common cause of high power consumption. CMOS inputs consume very ...

Signaling with conserved quantities: two realizations in CMOS and

... halfwave rectified to π+ and π• π is not a clock – The frequency of π determines slew rates of signals – Hence it determines an upper bound on system timing but does not otherwise determine it. – The period may be shorter than logic delays, or it may be longer for extremely low dynamic power. – The ...

... halfwave rectified to π+ and π• π is not a clock – The frequency of π determines slew rates of signals – Hence it determines an upper bound on system timing but does not otherwise determine it. – The period may be shorter than logic delays, or it may be longer for extremely low dynamic power. – The ...

Lab Guide - inst.eecs.berkeley.edu - University of California, Berkeley

... b. What happens when you lower Vpp? c. What happens if you use a negative offset? d. What happens to the output if you make the input Vpp = 0.5V and you increase the offset = 0.5V. e. What happens if you lower the frequency of the function generator? f. What happens as you vary the resistance on the ...

... b. What happens when you lower Vpp? c. What happens if you use a negative offset? d. What happens to the output if you make the input Vpp = 0.5V and you increase the offset = 0.5V. e. What happens if you lower the frequency of the function generator? f. What happens as you vary the resistance on the ...

High-Speed Electronic Circuits for 100 Gb/s Transport Networks M. Möller

... the high-speed performance of a DAC in time domain, its ability to perform a full-scale voltage step within one sample period can be used. Tab. 1 provides rise/fall time and the related full-scale voltage swing, partly based on calculations or estimations in the absence of explicit numbers. Excellen ...

... the high-speed performance of a DAC in time domain, its ability to perform a full-scale voltage step within one sample period can be used. Tab. 1 provides rise/fall time and the related full-scale voltage swing, partly based on calculations or estimations in the absence of explicit numbers. Excellen ...

Slide 1

... • kT/q doesn’t scale, so lowering Vth increases leakage • Fixed Vth, Vdd power density doesn’t scale well ...

... • kT/q doesn’t scale, so lowering Vth increases leakage • Fixed Vth, Vdd power density doesn’t scale well ...

alon_E3S - Center for Energy Efficient Electronics Science

... • kT/q doesn’t scale, so lowering Vth increases leakage • Fixed Vth, Vdd power density doesn’t scale well ...

... • kT/q doesn’t scale, so lowering Vth increases leakage • Fixed Vth, Vdd power density doesn’t scale well ...

Robobugs

... components using conductive tracks, pads and other features etched from copper sheets laminated onto a non-conductive substrate. PCBs can be single sided (one copper layer), double sided (two copper layers) or multi-layer (outer and inner layers). Multi-layer PCBs allow for much higher component den ...

... components using conductive tracks, pads and other features etched from copper sheets laminated onto a non-conductive substrate. PCBs can be single sided (one copper layer), double sided (two copper layers) or multi-layer (outer and inner layers). Multi-layer PCBs allow for much higher component den ...

Study of Switching Characteristics

... When the concentration of electrons near the surface of the substrate under the gate is higher than the concentration of holes, an n region is created, connecting the source and the drain regions. The induced n-region thus forms the channel for current flow from drain to source. The channel is only ...

... When the concentration of electrons near the surface of the substrate under the gate is higher than the concentration of holes, an n region is created, connecting the source and the drain regions. The induced n-region thus forms the channel for current flow from drain to source. The channel is only ...

Mixed Logic Circuit Design

... low voltage speed and power dissipation No real motivation to develop mixed circuits with these other types of logic ...

... low voltage speed and power dissipation No real motivation to develop mixed circuits with these other types of logic ...

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.