FP7 FET-OPEN i-RISC Innovative Reliable Chip Design from Low

... ∗ Sub-threshold and near-threshold regimes ∗ Setup ∗ Process variations (threshold voltage & oxide thickness) ∗ Supply voltage variations (+/- 30 mV) ∗ Different temperatures ...

... ∗ Sub-threshold and near-threshold regimes ∗ Setup ∗ Process variations (threshold voltage & oxide thickness) ∗ Supply voltage variations (+/- 30 mV) ∗ Different temperatures ...

... reduction as these devices posses “green–switch” properties like zero leakage current, infinite sub-threshold slope and temperature resilient behavior and are hence ideal candidates for ultra low-power (ULP) chips that can run of scavenged energy from light, acoustic vibrations or ambient RF signals ...

Unit I

... structures. Triggering these thyristor like devices leads to a shorting of VDD & VSS lines, usually resulting in a destruction of the chip. 10. What are the remedies to prevent Latch-up? The remedies for the latch-up problem include: (i) an increase in substrate doping levels with a consequent drop ...

... structures. Triggering these thyristor like devices leads to a shorting of VDD & VSS lines, usually resulting in a destruction of the chip. 10. What are the remedies to prevent Latch-up? The remedies for the latch-up problem include: (i) an increase in substrate doping levels with a consequent drop ...

ECGR 2255 Lab Write-Ups

... found in Chapter 6 of the ELEC 2210 textbook, Microelectronics Circuit Design by R.C. Jaeger, 3rd Edition (Sections 6.1, 6.2 on pp. 277 – 280). Further details specific to CMOS are found in Section 7.2 (p. 355) and TTL is discussed in Section 9.11 (p. 477) Two relevant diagrams regarding the VTC are ...

... found in Chapter 6 of the ELEC 2210 textbook, Microelectronics Circuit Design by R.C. Jaeger, 3rd Edition (Sections 6.1, 6.2 on pp. 277 – 280). Further details specific to CMOS are found in Section 7.2 (p. 355) and TTL is discussed in Section 9.11 (p. 477) Two relevant diagrams regarding the VTC are ...

Ultra-low power subthreshold current

... many high-speed and high-performance applications [1]. The differential topology of CML circuits provides high immunity to supply noise and crosstalk, while reduced voltage swing at the output helps to operate the circuit in very high frequencies with low noise generation [1, 2]. These properties ma ...

... many high-speed and high-performance applications [1]. The differential topology of CML circuits provides high immunity to supply noise and crosstalk, while reduced voltage swing at the output helps to operate the circuit in very high frequencies with low noise generation [1, 2]. These properties ma ...

Presentation

... When the output voltage is set to approximately the bandgap voltage of silicon, the voltage across R2 will compensate the temperature coefficient of VBE, and the output voltage will have a low TC. ...

... When the output voltage is set to approximately the bandgap voltage of silicon, the voltage across R2 will compensate the temperature coefficient of VBE, and the output voltage will have a low TC. ...

A p-channel MOSFET with a heavily-doped p

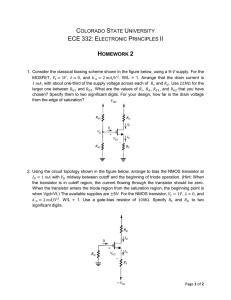

... (a) What is the role of the NMOS transistor when it is in the on state (when the input voltage is greater than its threshold voltage VTN, e.g. when VIN = VDD)? In steady state, what is the drain-to-source voltage difference, VDS, when the transistor is ON? (b) What is the role of the NMOS transistor ...

... (a) What is the role of the NMOS transistor when it is in the on state (when the input voltage is greater than its threshold voltage VTN, e.g. when VIN = VDD)? In steady state, what is the drain-to-source voltage difference, VDS, when the transistor is ON? (b) What is the role of the NMOS transistor ...

PPT

... • Solid-state switches; either permit or block current flow • A control input causes state change ...

... • Solid-state switches; either permit or block current flow • A control input causes state change ...

ppt

... – What processors can do fast and what they can’t do fast (avoid slow things if you want your code to run fast!) – Background for more in depth hw studies for your interest – There is just so much you can do with standard processors: you may need to design own custom hw for extra performance ...

... – What processors can do fast and what they can’t do fast (avoid slow things if you want your code to run fast!) – Background for more in depth hw studies for your interest – There is just so much you can do with standard processors: you may need to design own custom hw for extra performance ...

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.