* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

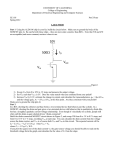

Download TOPOLOGIES AND MODELINGS OF NOVEL BIPOLAR GATE DRIVER TECHNIQUES FOR NEXT-GENERATION

Electric power system wikipedia , lookup

Three-phase electric power wikipedia , lookup

Stepper motor wikipedia , lookup

Loudspeaker enclosure wikipedia , lookup

Electrical ballast wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

History of electric power transmission wikipedia , lookup

Power engineering wikipedia , lookup

Power inverter wikipedia , lookup

Two-port network wikipedia , lookup

Stray voltage wikipedia , lookup

Surge protector wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Voltage regulator wikipedia , lookup

Electrical substation wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Current source wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Mains electricity wikipedia , lookup

Distribution management system wikipedia , lookup

Opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Current mirror wikipedia , lookup