* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Sign Extended Adder - Department of Electronics

Georg Cantor's first set theory article wikipedia , lookup

Infinitesimal wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Large numbers wikipedia , lookup

Real number wikipedia , lookup

Positional notation wikipedia , lookup

Location arithmetic wikipedia , lookup

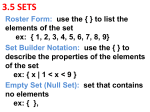

CARLETON UNIVERSITY Department of Electronics ELEC 2607 Switching Circuits Jan 30, 2008 Laboratory 2.0 A 3-Bit Binary Sign-Extended Adder/Subtracter Overview • A binary adder sums two binary numbers for example X = 101 and Y= 100 => Sum =1001 • The adder, you will build, will find the sum or difference of two 3-bit two’s-complement binary numbers represented here by, X = x2x1x0 and Y= y2y1y0 ,and show the result on four output lines. • Since some adder applications only do not allow the output sum to expand into an extra bit, it also signals an overflow when the sum is too large or small to be correctly represented with 3 bits. FIGURE 1 A summary and block diagram of the lab circuit. The details are explained later. Two’s Complement Numbers x2 3 DATA BITS 3-bit numbers +3 +2 +1 0 -1 -2 -3 -4 4-bit numbers +7 +6 +5 +4 +3 +2 +1 0 -1 -2 -3 -4 -5 -6 -7 -8 0111 0110 0101 0100 0011 0010 0001 0000 1111 1110 1101 1100 1011 1010 1001 1000 LEAST SIGNIFICANT BITS y0 y1 y2 3 DATA BITS 011 010 001 000 111 110 101 100 x0 x1 “1” SUB(H) ADD(L) “0” SWITCH 3-BIT, TWO’S COMPLEMENT ADDER/subtracter 3-bit sum OVF 2+2 is too big for a 3-bit 2’s complement numbers Negative numbers always have a leading 1. 3-bit Overflow s3 s2 s1 s0 4-bit sum Examples Y (+1) (+2) (+3) (-1) (+3) (-3) (-1) ( 0) ( 0) + + + + + + - (-1) (+2) (-4) (-4) (+3) (-2) (-4) (-4) ( 0) y2 0 0 0 1 0 1 1 0 0 y1 0 1 1 1 1 0 1 0 0 X y0 1 0 1 1 1 1 1 0 0 + + + + + + - x2 1 0 1 1 0 1 1 1 0 x1 1 1 0 0 1 1 0 0 0 S x0 1 0 0 0 1 0 0 0 0 3-bit s3 s2 s1 s0 0 0 0 1 0 1 0 0 0 0 1 1 0 1 0 0 1 0 0 0 1 1 1 1 1 0 0 0 0 1 1 0 1 1 0 0 OVF 0 1 0 1 1 1 0 1 0 Overflow happens when 3 bits will not correctly hold the sum, with 3 bit numbers, 4 bits will always hold the correct sum. To change 3-bit 2’s complement numbers into 4-bit 2’s complement: For positive numbers insert a leading 0. Thus (+3) 011 becomes 0011 For negative numbers insert a leading 1. Thus (-3) 101 becomes 1101 J.Knight, Jan 30, ’08 ELEC 2607 Switching Circuits Lab2-1 Carleton University Background FIGURE 2: 3-bit binary numbers Binary Numbers In decimal numbers, the digits are given a weight according to there position, thus: 325 is 3×100 + 2×10 + 5×1 +3 +2 +1 0 +7 +6 +5 +4 or 3×102 + 2×101 + 5×100 In binary numbers, the bits are given a weight according to there position, thus: 1101 is 13 = 1×8 + 1×4 + 0×2 + 1×1 8 + 4 + 0 + 1 or 1×23 + 1×22 + 0×21 + 1×20 In decimal 011 010 001 000 111 110 101 100 Negative numbers could be done in many ways, but the one most used in computer arithmetic is called two’s complement Two’s complement numbers are weighted like binary numbers except the first bit is given a negative weight.. 1101 is -3 = 1×(−8) + 1×4 + 0×2 + 1×1 or 1×(−23) + 1×22 + 0×21 + 1×20 - 8 + 4 + 0 + 1 In decimal Two’s Complement Numbers • These are a convenient method of representing negative numbers. • They look just like positive binary integers. They are two’s compliment only in the way you interpret them. • The same hardware can add both positive and negative numbers. Addition is done exactly the same way as for positive binary numbers. • A few gates will convert an adder into a subtracter. • Negative numbers all start with “1”, i.e. the most significant bit is “1”. • There is one more negative number than positive number. (There is -4, but no +4 for 3-bit numbers) Sign Extension (Adding leading Bits to Two’s Complement Numbers) FIGURE 3: Some two’s complement numbers 4-bit numbers 3-bit numbers +3 +2 +1 0 -1 -2 -3 -4 011 010 001 000 111 110 101 100 Negative numbers have a leading 1. +7 +6 +5 +4 +3 +2 +1 0 -1 -2 -3 -4 -5 -6 -7 -8 0111 0110 0101 0100 0011 0010 0001 0000 1111 1110 1101 1100 1011 1010 1001 1000 Placing leading zeros in front of a positive binary number causes no change. However doing this to a negative two’s complement number changes the leading bit from 1 to 0, making the number positive.. 110 is the same as 0110 in a positive binary system 06 6 = decimal values But 110 is not the same as 0110 in a two’s complement system. 06 ≠ -2 . decimal values To change a N bit two’s complement number into a N+1 bit one: - If the leading bit is 0, add another leading 0 - If the leading bit is 1, add another leading 1 Example: changing a 3-bit negative number (-3 decimal) into a 4, 5, 6 and 7-bit number... 101 = 1101 = 11101 = 111101 = 1111101 3-bit 4-bit 5-bit 6-bit 7-bit Lab2-2 ELEC 2607 Switching Circuits J.Knight, Jan 30, 2008 . Example: of why adding a leading “1” transforms a 3-bit negative number into a 4-bit one... 101 is 1×(−4) + 0×2 + 1×1 with another leading one 1101 is 1×(−8) + 1×4 + 0×2 + 1×1 -3 = -4 + 0 + 1 decimal values -3 = -8 + 4 + 0 + 1 Addition Of Binary Numbers, Including Two’s Complement Numbers To add two binary numbers, add them bit-by-bit transfering the carries left to the next column. In positive integer binary adds, the off-end carry is part of the number. Thus adding two three-bit numbers may give a four-bit number, as shown in the box on the left of Fig. 4. (3+6=9) With two’s complement numbers the final off-end carry is always ignored so the result of adding two 3-bit numbers is always a 3-bit number. This lab will only do two’s complement adds. FIGURE 4 Two’s complement binary addition example. Positive integer binary addition (+3) + (+6) 0 1 1 1 1 1 0 (+9) 1 2’s complement addition 1 1 0 0 1 1 1 1 0 + 0 0 1 With 2’s complement numbers, ignore the off-end carry. Here the off-end carry is part of the answer (+3) (- 2) 0 1 1 1 1 0 + (+1) 1 1 0 0 1 1 1 Carry 1 0 0 0 1 The addition is the same for positive or two’s complement numbers, except: For positive numbers include the off-end carry as part of the sum. For two’s complement addition ignore the off-end carry, and read the result as two’s complement. - If the remaining 3 bits of the number starts with a “0” it is a positive two’s complement number. - If the remaining 3 bits of the number starts with a “1” it is a negative two’s complement number. - Unless the answer overflows. Overflow in Two’s Complement Addition FIGURE 5: Overflow: When adding 3-bit numbers, 3-bits may not be enough to hold the sum. 2’s complement addition 2’s complement addition 0 + (+3) (+2) 0 0 1 1 (+5) 1 0 is too large for 3-bit two’s complement. We say it overflows. + 0 1 0 0 0 1 1 1 0 1 0 1 (- 3) + (- 3) (- 2) (- 5) 1 1 0 1 1 0 overflows 3-bit two’s complement 1 + 1 0 0 1 1 0 1 0 1 0 1 1 (+3) ignore the off-end carry. Ignore the off-end carry. For 3-bit two’s complement numbers, the sum must be between -4 and +3 or addition will overflow. Sign Extension Will Cure Overflow The leading bit tells the sign of the number. To use sign extension, concatenate a new sign (leading) bit of the same value as the previous sign bit, thus:1 110 is sign extended to 1110 and 010 is sign extended to 0010. 1. One can sign extend as far as desired, thus 110 as an 8 bit 2’s complement number is 11111110. J.Knight,Jan 30, ’08 ELEC 2607 Switching Circuits Lab2-3 Carleton University FIGURE 6 Curing Overflow with sign extension 2’s complement addition Sign extension (with sign extension) 0 + (+3) (+2) 0 0 1 1 1 0 0 1 0 0 0 0 0 1 1 1 0 (+5) 0 0 1 0 1 + (+5) +5 fits into a 4-bit 2’s complement number Ignore the off-end carry. if any 2’s complement addition Sign extension (with sign extension) + (- 3) (- 2) 1 1 0 1 1 0 (- 5) 1 0 0 1 1 1 1 0 1 1 0 (- 5) 1 1 0 1 1 1 + +5 fits into a 4-bit 2’s complement number Ignore the off-end carry. If the numbers are sign extended by one bit before adding, the results can never overflow. However the numbers becomes one bit longer, and take more storage.2 Checking an Addition for Overflow • Add the numbers as 3-bit numbers • Then do sign extension and add them as 4-bit numbers. • If the 3 and 4-bit answers have the same sign, there was no overflow and the 3-bit answer was correct. • If they have different signs, there was an overflow, and one must use the 4-bit answer and/or send the user an overflow warning. FIGURE 7 Checking for overflow With sign extension 2’s complement addition + (+3) (+2) 0 0 1 1 0 1 0 + (+5) (- 3) 0 3-bit number overflows because the leading 1 is part of the number and cannot be the sign. 1 0 0 0 1 1 1 0 1 0 1 Ignore. + + 1 1 0 1 0 0 1 1 1 1 1 0 (+5) 1 0 0 0 0 0 1 1 1 0 (+5) 0 0 1 0 1 + 4-bit two’s compliment has a 4th bit to give Ignore. the correct sign 3-bit sign These are different. Signs are different. There is overflow without sign extension 2’s complement addition (- 3) (- 2) (+3) (+2) Sign extension 0 0 1 1 0 + (- 5) 3-bit two’s compliment number overflows because the leading bit is not the correct sign. (- 3) 1 With sign extension 0 0 1 1 0 1 1 0 0 1 1 Ignore. 3-bit sign + Sign extension 1 0 0 1 1 1 1 0 1 1 0 (- 5) 1 1 0 1 1 1 (- 3) (- 2) 1 1 0 1 1 1 1 0 (- 5) 4-bit two’s compliment has a 4th bit to give the correct sign 4-bit sign + These are different Ignore. 4-bit sign Signs are different. There is overflow without sign extension FIGURE 8 Checking for overflow using the last two bits of the sign extended add. With sign extension 2’s complement addition 1 + (-3) (-1) 1 1 0 1 1 1 (- 4) 3-bit number overflows + (- 4) 1 Ignore. 1 1 1 1 0 1 1 1 1 0 0 + (-3) (-1) 1 1 0 1 1 1 1 1 (-4) Sign extension 1 1 1 1 1 1 1 0 1 1 1 (-4) 1 1 1 0 0 1 + 4-bit two’s compliment has a 4th bit to give Ignore. the correct sign Signs are the same. No overflow. Sign extension not needed These are the same No overflow. 4-bit sign 2. Some filter circuits add a hundred or more numbers. If each addition requires a one bit increase, one might start with an 8-bit number and end with a 108-bit number! Lab2-4 ELEC 2607 Switching Circuits J.Knight, Jan 30, 2008 Sign extension is not always the answer. Computers store 16 bit integers, and most adds do not overflow. Computers do not store sums as 17 bits. They can store them using 32 bits, but only if necessary. Often one would like to send out a warning signal that the 16 bit addition overflowed and tell the computer to store this sum with 32 bits. To Tell If a Sum Overflowed 3 Bits (Or N Bits in General) Add the numbers with sign extension. Then compare the leftmost two sum bits: If they are equal all is OK. Remember to ignore off-end carry If they are not equal send out an overflow warning. Examples FIGURE 9 Examples of two’s complement addition, with and without sign extension and overflow checking. 2’s complement addition 3-bit addition 3-bit sum + (+3) (-4) (- 1) 3-bit addition With sign extension 0 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 1 1 1 1 1 Correct 3-bit sum 3-bit sum + (- 5) No overflow of 3--bit sum. + (-2) (-2) (- 4) Correct 4-bit sum 1 1 0 1 1 1 1 0 0 1 1 1 0 1 1 Overflow of 3-bit sum. Correct 4-bit sum 4-bit addition 4-bit sum With sign extension 1 1 0 1 1 0 1 1 1 0 1 1 1 0 1 0 0 1 1 0 0 Correct 3-bit sum With sign extension 1 0 1 1 1 0 Wrong 3-bit sum 3-bit addition 3-bit sum (-3) (-2) + No Overflow. Correct 4-bit sum With sign extension (-3) 1 1 0 1 (-2) 1 1 1 0 1 1 1 0 1 1 1 1 1 0 (- 5) 1 0 1 1 1 1 0 1 1 Correct 4-bit sum No Overflow. Correct 5-bit sum 2.1 Calculation of the Compliment. To Take The Two’s Complement Of A Binary Number 1. Invert each bit. 2. add 1 3. ignore any carry. 4-bit numbers 3-bit numbers +3 +2 +1 0 -1 -2 -3 -4 011 010 001 000 111 110 101 100 Example: Take the 2’s complement of +1 (001 in binary). Take 001, invert bits 110 add one 1 Negative numbers 111 (111 is ‘-1’ in 2’s complement) always have a leading 1. • Find the 3-bit two’s complement representation of +3, -2, -1, -4. using the method above. (You will be asked to do this in the prelab for 5-bit numbers.) +7 +6 +5 +4 +3 +2 +1 0 -1 -2 -3 -4 -5 -6 -7 -8 0111 0110 0101 0100 0011 0010 0001 0000 1111 1110 1101 1100 1011 1010 1001 1000 Two’s Complement Numbers • Explain what is special about the 3-bit two’s complement of -4?3 Hint: When you add 1, try sign extending before you add 3. Hint: When you add 1, try sign extending before you add. Then check for overflow. J.Knight,Jan 30, ’08 ELEC 2607 Switching Circuits Lab2-5 Carleton University 2.1.1 The Adder Circuit FIGURE 10 The Half Adder, an Adder for Two Single-Bit Numbers xi yi Until we get into detailed logic, after Step 3.4 , “ +” will mean “plus”, not “OR”. HALF ADDER This circuit can add 0+0, 0+1, 1+0, and 1+1. It gives a single-bit sum output si and a single-bit carry output ci+1 ci+1 The Full-Adder, an Adder for Three Single-Bit Numbers si FIGURE 11 xi yi The half-adder is not enough for adding binary numbers. One must be able to add three input bits. The third bit, ci is for a carry input. ci FULL ADDER An Iterative Adder Circuit for Multibit Numbers ci+1 si One can make a multibit adder by combining full adders in an iterative circuit, also called bit-sliced circuits. These are circuits which can be made from identical sections coupled together. FIGURE 12 A 3-bit adder made from three full-adders, an example of an iterative or bit-sliced circuit... x2 y2 FULL ADDER Not part of sum with 2’s complement numbers c3 x1 y1 c2 FULL ADDER s2 x0 y0 c1 FULL ADDER s1 c0 C0=0 for addition s0 The carry output of one full-adder is sent to the next full-adder. In the above picture, “c3” is ignored in two’s complement addition. “c0” is always zero since there is no carry input Adding Multibit Two’s Complement Numbers The advantage of two’s complement numbers is, that negative numbers are added exactly the same way positive numbers. Thus the positive integer adder circuit in Fig. 12 could be used for adding two’s complement integers. However, unlike 3-bit positive integers, adding 3-bit two’s complement integers cannot give a 4-bit number. The carry out c3, is never part of the sum. Remember In two’s compliment the off-end carry is never part of the sum! A Two’s Complement subtracter • To calculate Y - X, one adds Y to the 2’s complement of X. Let X = xnxn-1 ...x10x0 • To get the 2’s compliment, inverts each of the bits of X, to get xnxn-1 ...x1x0 and add “1”. In summary, Y - X = Y + xnxn-1 ...x1x0 + 1 A convenient way to add the “1”, is to use “c0” input. FIGURE 13 A 2’s complement subtracter. For a 3-bit number like X = x2x1x0, inverting each bit gives= x2x1x0 x2 y2 c3 FULL ADDER ELEC 2607 Switching Circuits c2 x0 x1 y1 x2 s2 Lab2-6 x1 FULL ADDER s1 x0 y0 c1 1 c0 FULL ADDER s0 J.Knight, Jan 30, 2008 A Combination Adder-Subtractor One can make a circuit that both adds and subtracts by: (1) Having the inverters switch in and out of the circuit by external subtract/add control. (2) Making the initial carry in, c0 = 0 for addition and c0 = 1 for subtraction. FIGURE 14 Making an adder into a combination add-subtract unit. “1” SUB(H) x2 x1 INVERT CNTRL INVERT CNTRL Sub(H)/Add(L) ADD(L) Control Switch “0” z2 y2 The switch inverts xi when “1” and does not invert when “0”. When it is “1”, it also injects a “1” into “c0”. c3 y1 c2 FULL ADDER INVERT CNTRL z0 y0 z1 c1 FULL ADDER s2 x0 c0 FULL ADDER s1 s0 A Controlled Inverter. To build a combination adder/subtracter, one needs a way to invert or not invert on command FIGURE 15 A controlled inverter circuit.. Sub(H)/Add(L) Xi Zi 0 1 0 1 1 0 0 1 1 1 0 0 Xi gate Sub(H)/Add(L) Zi = Xi IF Sub(H)/Add(L) = 0 Xi IF Sub(H)/Add(L) = 1 The signal name Sub(H)/Add(L) means subtract when the signal is high (1) and add when it is low (0). The gate in the box, inverts “xi” when the control signal Sub(H)/Add(L) is “1”, and passes “xi” with no change when Sub(H)/Add(L) is “0”. This is a fairly common logic gate. Can you give this gate’s name? The Sign Extended Adder The sign extended adder repeats the addition of the most significant bits with a different input carry. Does one need a complete full adder for this last circuit. Does the last full adder need a carry out? FIGURE 16 A sign-extended adder. “1” SUB(H) ADD(L) “0” x2 x1 INVERT CNTRL INVERT CNTRL Sub(H)/Add(L) SWITCH z2 y2 FULL ADDER ? s3 J.Knight,Jan 30, ’08 c3 FULL ADDER y1 c2 s2 ELEC 2607 Switching Circuits x0 INVERT CNTRL FULL ADDER s1 z0 y0 z1 c1 FULL ADDER c0 s0 Lab2-7 Carleton University FIGURE 17 A sign-extended adder with an overflow check to tell if only 3 bits are needed. “1” x2 x1 Sub(H)/Add(L) SUB(H) ADD(L) “0” INVERT CNTRL SWITCH z2 y2 Check if 3-bits is enough to hold result ? NOT EQUAL s3 c3 INVERT CNTRL y1 c2 FULL ADDER s2 INVERT CNTRL z0 y0 z1 FULL ADDER x0 c1 FULL ADDER s1 c0 s0 3-Bit_OVF From Fig. 8 (p. 4) one knows that if s3 = s2 there is no overflow in the 3-bit sum. if s3 ≠ s2 overflowed 3-bits. Thus one can add an overflow check by using a NOT EQUAL gate. What kind of a gate can check for inequality? FIGURE 18 An inequality detection circuit. Lab2-8 Ovf s2 s3 s ≠ s 2 3 1 1 0 0 0 1 0 1 1 0 0 1 s2 s3 ELEC 2607 Switching Circuits gate Ovf J.Knight, Jan 30, 2008 Prelab (This must be prepared prior to the scheduled lab session. You must show calculations, since some unscrupulous individuals sometimes sabotage their education by copying raw answers. It will be checked near the start of the lab. It will also be an appendix for your final report.) 3.0 Convert the binary number 1000 to decimal in a system having only positive numbers. Do the same for a system of 2’s complement number? 3.1 Make a table of 5-bit two’s-complement numbers showing them opposite their decimal values. You may put in a row of dots “. . .” to save writing, but show the top 3 numbers, the bottom 3 numbers, and at least +2, +1, 0, -1 and -2. 3.2 Show how to calculate 4-bit two’s complement of numbers by inverting and adding 1. Use +7 , -1 and -8 as examples. Decide if there is a 4-bit two’s complement of -4. 3.3 Do the following (a through d) arithmetic problems as a 3-bit binary sign-extended adder/subtracter would do them. Show how the carries propagate and how the overflow for 3-bits is calculated as is illustrated in Fig. 19 for the 3 bit subtraction of X - Y = (-3) - (+2). (b) (-1) + (-1), (a) (+2) + (+2), (c) (-2) + (-1), (d) (-3) - (-3), (e) (-3) - (+3). FIGURE 19 Doing a 2’s complement sign-extended subtract. Sign Extension - (- 3) (+2) 1 0 1 0 0 1 1 0 + 1 0 1 1 1 1 1 0 0 Subtract here means invert all bits here (-5) Then the subtraction can be done as addition Provided an extra 1 is added to the least significant bit. 3.4 1 0 1 Carry 1 1 1 1 1≠0 Initial 1 carry in, as part of 2’s complement calculation 1≠0 Not Equal Means Overflow Complete the truth table for a generic full adder. The three inputs are xi, yi, and ci. The two outputs are sum and carry, that is si and ci+1 Partial Truth Table for a Generic Full Adder Expression for Expression for ci+1 si yi xi ci ci+1 si 0 0 0 0 1 -- 0 0 1 1 0 -- 0 1 0 1 1 -- 0 0 0 1 1 -- 0 1 1 0 0 -- yixici yixici ---- ---- 1 1 1 1 1 yixici yixici 3.5 FIGURE 20 xi yi ci FULL ADDER yixici yixici ci+1 si -- Obtain the equations for the generic full adder from the truth table.4 4. One can learn many things, that may be useful here, from the lecture notes Basic Logic Gates and Formulas athttp://www.doe.carleton.ca/%7Ejknight/97.267/2607_07W/indexNotes07.html (there may be a later release) J.Knight,Jan 30, ’08 ELEC 2607 Switching Circuits Lab2-9 Carleton University 3.6 Simplify the equations. Hint 1: (This may or may not help you) (a⊕b)c + ab = (ab + ab)c + ab = abc + abc + abc + abc + ab = ac + bc + ab Expand xor xc+x = x (Simplification) xb + xb = x, use twice 3.7 Take the simplified equations you just derived for the full-adder subcircuit and draw a schematic from them. 3.8 What logic gate can function as a controlled inverter? What gate can test two bits for equality? 3.9 Design a generic “invert control” unit that inverts the “xi” input when subtract is selected. 3.10 Design the circuit that detects overflow. 3.11 Draw a block diagram for the complete 3-bit adder/subtracter. Use blocks, or gates if the block is only one gate, for the standard subcircuits you designed in subsections 3.6, 3.9 and 3.10. The figure below gives an idea of what is wanted,. However several necessary things are left out. FIGURE 21 Partial block diagram of the adder/subtracter. x2 SubIf_1 x1 x0 input y2 3-BIT OVERFLOW DETECT OVF 3.12 3.13 c3 y1 FULL ADDER 2 c2 s2 y0 FULL ADDER 1 c1 FULL ADDER 0 s1 s0 c0 LEAST SIGNIFC BIT You should have at least three types of blocks: full-adders, invert-control, and overflow detect. Draw a schematic of each type of block, with the gates drawn the way they will appear in the lab. This lab will be done with a computer simulation, so you will have as many gates of each type as you need. Can one of the additions be done by a simpler circuit than a full adder? If so, use it. 2.2 In the Laboratory The lower-level schematic This circuit will be implemented by drawing circuits on the computer screen the Top-Level Schematic, the Adder Symbol and the Full Adder Symbol are already drawn. You will draw the lower level schematic for the Adder somewhat like the schematic on the right in Fig. 22. You will also draw the Full Adder. The simulation After the schematic is correctly entered, you will need to simulate the circuit. The simulations will come out as wave forms which are hard to read without detailed study. In labaratory reports, you should anotate a representative sample of the 128 cases. See Fig. 23 Lab2-10 ELEC 2607 Switching Circuits J.Knight, Jan 30, 2008 FIGURE 22 The hierarchy of schematics and symbols used in the lab. . Leads in the schematic are connected to leads of the same name on the symbol, as shown for C0 and S0. Top-Level Schematic The wires(nets) C0,X0,Y0,X1 ... are seen by the simulator. C0 X0 X1 X2 C0 ADDER X1 X2 X0 X1 X2 Y0 Y1 Y2 S0 S1 S2 S3 OVF X0 X1 X2 X0 X1 X2 X3 OVF Y0 Y1 Y2 C0 X0 Y0 X1 C0 S0 S1 S2 S3 OVF ADDER Use C0 for SUB(H)/ADD(L) X0 Y1 Y2 X2 X2 Net (wire) names on this schematic are the same as on the symbol. They don’t have to be. Value of X in decimal -4 -2 -3 -1 0 1 2 3 -4-3 -2 -1 0 1 2 3 -4 -3-2 -1 0 1 2 3 -4 -3 -2 -1 0 X0 C1 S1 OVF S2 S3 Lower-level schematic of what is inside the the adder symbol. (Note this circuit is not a real adder) Adder symbol used in top-level schematic Schematic of circuit using the adder and nothing else FULL S0 ADD FIGURE 23 How to annotate simulation waveforms so the TA can understand them. X1 Value of X in decimal -1 1 1 2 3 Annotate you waveforms at various interesting spots. Here some values that give a 0 for 2’s complement and 8 for positive numbers are noted. Also some that give an overflow are highlighted. The notation show what the numbers are in decimal. That way someone reading your report can check your results more easily. X2 Y0 Y1 Value of Y in decimal Y2 Write the notes on by hand. It is hard to print them, and they stand out more. S0 Sample annotations here are in blue. S1 S2 Value of S in decimal -3 -2 -1 0 2 3 4 5 -2 -1 0 1 3 4 5 6 -1 -2 S3 J.Knight,Jan 30, ’08 1+3=4, OVF For pos integers (7)+1 = 8 for 2‘‘s comp -1 + 1 =0 -1+1=-0, OVF There is no +4 in 3-bit 2’s comp. hence overflow ELEC 2607 Switching Circuits Lab2-11 Carleton University Lab2-12 ELEC 2607 Switching Circuits J.Knight, Jan 30, 2008