Low Distortion Differential ADC Driver AD8138

... performance ADCs, preserving the low frequency and dc information. The common-mode level of the differential output is adjustable by a voltage on the VOCM pin, easily level-shifting the input signals for driving single-supply ADCs. Fast overload recovery preserves sampling accuracy. The AD8138 disto ...

... performance ADCs, preserving the low frequency and dc information. The common-mode level of the differential output is adjustable by a voltage on the VOCM pin, easily level-shifting the input signals for driving single-supply ADCs. Fast overload recovery preserves sampling accuracy. The AD8138 disto ...

Manual T800

... 2.10 J P17: Bypass Low Pass Filter (Rev 4 or higher ) Some trunking controllers have digital encoding schemes that require the low pass filter in the tone input section to be bypassed. JP17 allows this. Normally JP17 is open circuit. Placing a link across it will bypass the low pass filter. In conju ...

... 2.10 J P17: Bypass Low Pass Filter (Rev 4 or higher ) Some trunking controllers have digital encoding schemes that require the low pass filter in the tone input section to be bypassed. JP17 allows this. Normally JP17 is open circuit. Placing a link across it will bypass the low pass filter. In conju ...

COMMUNICATIONS

... network, an overshoot occurs which may be of considerable magnitude. A number of these overshoots have been calculated graphically for a typical transition. The pre-emphasis network used was not the idealized one whose output continues to rise at 6 db per octave from the turn-over frequency to infin ...

... network, an overshoot occurs which may be of considerable magnitude. A number of these overshoots have been calculated graphically for a typical transition. The pre-emphasis network used was not the idealized one whose output continues to rise at 6 db per octave from the turn-over frequency to infin ...

chapter 1 operational amplifier

... 1.2 Ideal Op-Amp Infinite Input Impedance Input impedance is measured across the input ...

... 1.2 Ideal Op-Amp Infinite Input Impedance Input impedance is measured across the input ...

HMC706LC3C 数据资料DataSheet下载

... to support data transmission rates of up to 13 Gbps, and clock frequencies as high as 13 GHz. During normal operation, RZ data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negative-edge triggered applications. All input signals to the HMC706L ...

... to support data transmission rates of up to 13 Gbps, and clock frequencies as high as 13 GHz. During normal operation, RZ data is transferred to the outputs on the positive edge of the clock. Reversing the clock inputs allows for negative-edge triggered applications. All input signals to the HMC706L ...

AMS5105 数据手册DataSheet 下载

... Dropout Voltage: The input-output voltage differential at which the circuit stops to regulate against further reduction in input voltage. Measured when the output voltage has dropped 100mV from the nominal voltage obtained at 1V input, dropout voltage is dependent upon load current and junction temp ...

... Dropout Voltage: The input-output voltage differential at which the circuit stops to regulate against further reduction in input voltage. Measured when the output voltage has dropped 100mV from the nominal voltage obtained at 1V input, dropout voltage is dependent upon load current and junction temp ...

Signal Integrity

... terminated transmission line, whatever signal is applied at the output will occur at the input after the propagation time of the transmission line. The impedance of the transmission line can be calculated with the following formula: L ...

... terminated transmission line, whatever signal is applied at the output will occur at the input after the propagation time of the transmission line. The impedance of the transmission line can be calculated with the following formula: L ...

a 380 MHz, 25 mA, Triple 2:1 Multiplexers AD8183/AD8185

... 380 MHz, along with slew rate of 1000 V/µs. With better than –90 dB of channel-to-channel crosstalk and isolation at 10 MHz, they are useful in many high-speed applications. The differential gain and differential phase errors of 0.01% and 0.02° respectively, along with 0.1 dB flatness to 90 MHz make ...

... 380 MHz, along with slew rate of 1000 V/µs. With better than –90 dB of channel-to-channel crosstalk and isolation at 10 MHz, they are useful in many high-speed applications. The differential gain and differential phase errors of 0.01% and 0.02° respectively, along with 0.1 dB flatness to 90 MHz make ...

USB Voltage and Current Output Devices

... D/A LOAD signal from an external source. When the SYNCLD pin receives the trigger signal, the analog outputs are updated simultaneously. In master mode, the internal D/A LOAD signal is sent to the SYNCLD pin. You can then synchronize with a second device of the same type and simultaneously update th ...

... D/A LOAD signal from an external source. When the SYNCLD pin receives the trigger signal, the analog outputs are updated simultaneously. In master mode, the internal D/A LOAD signal is sent to the SYNCLD pin. You can then synchronize with a second device of the same type and simultaneously update th ...

MAX4649 - Maxim Integrated

... Note 1: Signals on NO, NC, COM, or IN exceeding V+ or V- are clamped by internal diodes. Limit forward-diode current to maximum current rating. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operat ...

... Note 1: Signals on NO, NC, COM, or IN exceeding V+ or V- are clamped by internal diodes. Limit forward-diode current to maximum current rating. Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operat ...

Current-Mode Control Stability Analysis For DC

... implementations exploit a fixed-slope compensation ramp amplitude, the ideal slope-compensation level is proportional to output voltage. Note that excessive slope compensation increases m c, decreases Q, and reduces the current-loop gain and bandwidth. This portends additional phase lag in the volta ...

... implementations exploit a fixed-slope compensation ramp amplitude, the ideal slope-compensation level is proportional to output voltage. Note that excessive slope compensation increases m c, decreases Q, and reduces the current-loop gain and bandwidth. This portends additional phase lag in the volta ...

MAX16841 Controller IC for Dimmable Offline LED Lamps EVALUATION KIT AVAILABLE General Description

... conditions. The peak-limit comparator has a threshold of 2.2V. For the active PFC, the device uses a proprietary current-control scheme where the averaged switch current on a cycle-by-cycle basis is set to a programmed DC value. This maximizes the efficiency of the converter by operating in continuo ...

... conditions. The peak-limit comparator has a threshold of 2.2V. For the active PFC, the device uses a proprietary current-control scheme where the averaged switch current on a cycle-by-cycle basis is set to a programmed DC value. This maximizes the efficiency of the converter by operating in continuo ...

Senior project - Clark Haynie Walters

... The disturbance from the microphone was fed into the first TL071 op amp set up for positive gain to allow for easier manipulation of the wave. This was then fed into the second TL071 setup as a voltage follower with the purpose of preventing loading on the filter circuit. The third TL071 was design ...

... The disturbance from the microphone was fed into the first TL071 op amp set up for positive gain to allow for easier manipulation of the wave. This was then fed into the second TL071 setup as a voltage follower with the purpose of preventing loading on the filter circuit. The third TL071 was design ...

AIC2857F

... The system has one zero of importance, due to the The selection of output capacitor depends on the required output voltage ripple. The output voltage ...

... The system has one zero of importance, due to the The selection of output capacitor depends on the required output voltage ripple. The output voltage ...

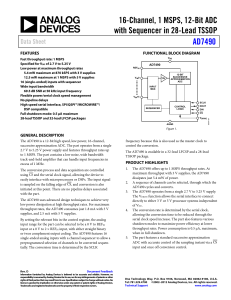

AD7490 16-Channel, 1 MSPS, 12-Bit ADC with Sequencer in 28

... Guaranteed by characterization. All input signals are specified with tR = tF = 5 ns (10% to 90% of VDD) and timed from a voltage level of 1.6 V (see Figure 2). The 3 V operating range spans from 2.7 V to 3.6 V. The 5 V operating range spans from 4.75 V to 5.25 V. The mark/space ratio for the SCLK in ...

... Guaranteed by characterization. All input signals are specified with tR = tF = 5 ns (10% to 90% of VDD) and timed from a voltage level of 1.6 V (see Figure 2). The 3 V operating range spans from 2.7 V to 3.6 V. The 5 V operating range spans from 4.75 V to 5.25 V. The mark/space ratio for the SCLK in ...

AD7840 数据手册DataSheet 下载

... in conjunction with WR to load parallel data to the input latch. For applications where CS is permanently low, an R, C is required for correct power-up (see LDAC input). If this input is tied to VSS, it defines the AD7840 for serial mode operation. Write/Frame Synchronization Input. In the parallel ...

... in conjunction with WR to load parallel data to the input latch. For applications where CS is permanently low, an R, C is required for correct power-up (see LDAC input). If this input is tied to VSS, it defines the AD7840 for serial mode operation. Write/Frame Synchronization Input. In the parallel ...

lecture12

... Finding the Initial Condition To find x(t0+), the current or voltage just after the switch, we use the following essential fact: Capacitor voltage is continuous; it cannot jump when a switch occurs. So we can find the capacitor voltage VC(t0+) by finding VC(t0-), the voltage before switching. We ca ...

... Finding the Initial Condition To find x(t0+), the current or voltage just after the switch, we use the following essential fact: Capacitor voltage is continuous; it cannot jump when a switch occurs. So we can find the capacitor voltage VC(t0+) by finding VC(t0-), the voltage before switching. We ca ...

INSTRUCTION MANUAL FOR VOLTAGE REGULATOR Model: APR

... If the exciter field voltage exceeds 100 ±5 Vdc, the regulator automatically removes the field current after a time delay. The time delay is inversely proportional to the magnitude of the detected overvoltage condition. At approximately 135 ±5 Vdc, the field voltage is removed instantaneously. Refer ...

... If the exciter field voltage exceeds 100 ±5 Vdc, the regulator automatically removes the field current after a time delay. The time delay is inversely proportional to the magnitude of the detected overvoltage condition. At approximately 135 ±5 Vdc, the field voltage is removed instantaneously. Refer ...

Analog-to-digital converter

An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity's amplitude.The conversion involves quantization of the input, so it necessarily introduces a small amount of error. Furthermore, instead of continuously performing the conversion, an ADC does the conversion periodically, sampling the input. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal.An ADC is defined by its bandwidth (the range of frequencies it can measure) and its signal to noise ratio (how accurately it can measure a signal relative to the noise it introduces). The actual bandwidth of an ADC is characterized primarily by its sampling rate, and to a lesser extent by how it handles errors such as aliasing. The dynamic range of an ADC is influenced by many factors, including the resolution (the number of output levels it can quantize a signal to), linearity and accuracy (how well the quantization levels match the true analog signal) and jitter (small timing errors that introduce additional noise). The dynamic range of an ADC is often summarized in terms of its effective number of bits (ENOB), the number of bits of each measure it returns that are on average not noise. An ideal ADC has an ENOB equal to its resolution. ADCs are chosen to match the bandwidth and required signal to noise ratio of the signal to be quantized. If an ADC operates at a sampling rate greater than twice the bandwidth of the signal, then perfect reconstruction is possible given an ideal ADC and neglecting quantization error. The presence of quantization error limits the dynamic range of even an ideal ADC, however, if the dynamic range of the ADC exceeds that of the input signal, its effects may be neglected resulting in an essentially perfect digital representation of the input signal.An ADC may also provide an isolated measurement such as an electronic device that converts an input analog voltage or current to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs. The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.The inverse operation is performed by a digital-to-analog converter (DAC).