UNIT-3 (1) - WordPress.com

... trigger pulse and to go through a full cycle, two triggering pulses, one for each stage are required. Its more common name or term of “flip-flop” relates to the actual operation of the device, as it “flips” into one logic state, remains there and then changes or “flops” back into its first original ...

... trigger pulse and to go through a full cycle, two triggering pulses, one for each stage are required. Its more common name or term of “flip-flop” relates to the actual operation of the device, as it “flips” into one logic state, remains there and then changes or “flops” back into its first original ...

Data Sheet - Time Electronics

... Automatic stepping of the output is also available, both up and down with programmable dwell times. Continuous up/down ramping can also be performed, with user programmable ramp rates and dwell time (top and bottom). In source mode the range can be user programmed to any value between 0mA and 50mA, ...

... Automatic stepping of the output is also available, both up and down with programmable dwell times. Continuous up/down ramping can also be performed, with user programmable ramp rates and dwell time (top and bottom). In source mode the range can be user programmed to any value between 0mA and 50mA, ...

TLV571 数据资料 dataSheet 下载

... consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than REFP and is at zero when the input signal is equal to or lower than REFM. sampling/conversion All sampling, conversion, and data output in the device are start ...

... consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than REFP and is at zero when the input signal is equal to or lower than REFM. sampling/conversion All sampling, conversion, and data output in the device are start ...

RC-410

... By using RC-410, two stepping motors can be controlled simultaneously. Stall detection of stepping motors is available by connecting stall detection sensor to RC-410 When using RD-1 series driver, a low step pulse (pulses in deceleration period) needs to be set up in advance. RD-3 series driver h ...

... By using RC-410, two stepping motors can be controlled simultaneously. Stall detection of stepping motors is available by connecting stall detection sensor to RC-410 When using RD-1 series driver, a low step pulse (pulses in deceleration period) needs to be set up in advance. RD-3 series driver h ...

AN028: Building an Auto-Ranging DMM with the ICL7103A

... right occurs. Basically, this means the ICL7103A/ICL8052A will convert small inputs (VIN ≤ 18.00mV) and signals greater than 200V in a 4 1/2 digit mode. This is accomplished with AND gates #2B and #3B and OR gate #3. The integrator and comparator time constants are controlled by OR gate #4. Short ti ...

... right occurs. Basically, this means the ICL7103A/ICL8052A will convert small inputs (VIN ≤ 18.00mV) and signals greater than 200V in a 4 1/2 digit mode. This is accomplished with AND gates #2B and #3B and OR gate #3. The integrator and comparator time constants are controlled by OR gate #4. Short ti ...

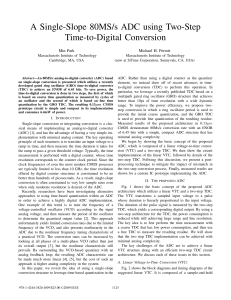

A Single-Slope 80 MS/s ADC Using Two-Step Time to

... conversion by counting transitions of a ring oscillator which is enabled only during the measurement interval. The raw resolution of this TDC corresponds to an inverter delay, but the structure interestingly achieves first order noise shaping of its quantization noise [7]. A further improvement in r ...

... conversion by counting transitions of a ring oscillator which is enabled only during the measurement interval. The raw resolution of this TDC corresponds to an inverter delay, but the structure interestingly achieves first order noise shaping of its quantization noise [7]. A further improvement in r ...

Loop Bandwidth and Clock Data Recovery (CDR) in

... Ideally, the input signal to a PLL is a perfect sine wave and the output will pull in and match that output perfectly. However, in any real word signal there is going to be noise in frequency, amplitude, and phase. The PLL has to be able to maintain a lock in the presence of noise but it must not be ...

... Ideally, the input signal to a PLL is a perfect sine wave and the output will pull in and match that output perfectly. However, in any real word signal there is going to be noise in frequency, amplitude, and phase. The PLL has to be able to maintain a lock in the presence of noise but it must not be ...

Unit 6. Analog-to-Digital Conversion

... ADC: A Three-Step Process •On the previous slide, the box labeled ADC actually represents three steps: 1. Anti-aliasing Filter ...

... ADC: A Three-Step Process •On the previous slide, the box labeled ADC actually represents three steps: 1. Anti-aliasing Filter ...

a 200 MHz Clock Generator PLL ADF4001

... Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input. Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control ...

... Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input. Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control ...

Product sheet (PDF/389 kB)

... The module is provided with an integrated realtime data recorder for the high-precision recording of up to 16 measuring channels during protective tripping or synchronization. Error events are recorded continuously and stored permanently with a high resolution time entry. The internal time base of t ...

... The module is provided with an integrated realtime data recorder for the high-precision recording of up to 16 measuring channels during protective tripping or synchronization. Error events are recorded continuously and stored permanently with a high resolution time entry. The internal time base of t ...

Practical Sample and Hold Circuit

... Example: An 8-bit digital system is used to convert an analog signal to digital signal for a data acquisition system. The voltage range for the conversion is 0-10 V. Find the resolution of the system and the value of the least significant bit n=8 ...

... Example: An 8-bit digital system is used to convert an analog signal to digital signal for a data acquisition system. The voltage range for the conversion is 0-10 V. Find the resolution of the system and the value of the least significant bit n=8 ...

- Lotus Live Projects

... generate the necessary wave forms to control the frequency of the inverter through proper design of the switching pulse. Spwm or sinusoidal pulse width modulation is widely used in power electronics to digitize the power so that a sequence of voltage pulses can be generated by the on and off of the ...

... generate the necessary wave forms to control the frequency of the inverter through proper design of the switching pulse. Spwm or sinusoidal pulse width modulation is widely used in power electronics to digitize the power so that a sequence of voltage pulses can be generated by the on and off of the ...

Low Power Design of Integrated Systems Assoc. Prof. Dimitrios

... Techniques • Architecture-driven voltage reduction: The key idea is to speed up the circuit in order to be able reduces voltage while meeting throughput rate constraints. Voltage reduction can be achieved by introducing parallelism in hardware or inserting flip-flops • Switching activity minimizatio ...

... Techniques • Architecture-driven voltage reduction: The key idea is to speed up the circuit in order to be able reduces voltage while meeting throughput rate constraints. Voltage reduction can be achieved by introducing parallelism in hardware or inserting flip-flops • Switching activity minimizatio ...

... manufactured by Kulite Semiconductor Products, Inc. Although these semiconductor strain gauge transducers are widely used, they can suffer from a number of drawbacks, such as being easily damaged by slight overloads applied to the force beam, causing the transducer to be non-functional, or have a ve ...

An Asynchronous Delta-Sigma Converter Implementation

... with 0.2 V amplitude. As the sine wave amplitude increases, the SNR increases with a slope of 1dB/1dB to reach the peak of 51 dB at around −2.5 dBFS, and then quickly drops to 0 dB. The SNR drop is due to the increased nonlinearities caused by the larger amplitude signal input and the frequency alia ...

... with 0.2 V amplitude. As the sine wave amplitude increases, the SNR increases with a slope of 1dB/1dB to reach the peak of 51 dB at around −2.5 dBFS, and then quickly drops to 0 dB. The SNR drop is due to the increased nonlinearities caused by the larger amplitude signal input and the frequency alia ...

ppt

... cos2*pi*5t + (1/3)cos2*pi*15t + (1/5)cos2*pi*25t + (1/7)cos2*pi*35t) In this example the 15 and 35 Hz signals have suffered a phase shift (which can be caused as a result of different propagation speeds) with respect to the 5 and 25 Hz signals. The pulse shape changes significantly. ...

... cos2*pi*5t + (1/3)cos2*pi*15t + (1/5)cos2*pi*25t + (1/7)cos2*pi*35t) In this example the 15 and 35 Hz signals have suffered a phase shift (which can be caused as a result of different propagation speeds) with respect to the 5 and 25 Hz signals. The pulse shape changes significantly. ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.