DesignReview1

... variation. We currently know that the project we are working on has the goal of reducing the energy and area spent on a device, while ideally operating at the same speed or faster than the current model. The question now becomes how we can convert our knowledge into something feasible. We will also ...

... variation. We currently know that the project we are working on has the goal of reducing the energy and area spent on a device, while ideally operating at the same speed or faster than the current model. The question now becomes how we can convert our knowledge into something feasible. We will also ...

QUESTION BANK

... deflections plates. But the two beams are deflected horizontally by the common set of horizontal plates. 59.What is the principle of sampling oscilloscope?.(May/June 2010) Using sampling procedure, high frequency signal is converted to the low frequency signal. Thus instead of monitoring the input s ...

... deflections plates. But the two beams are deflected horizontally by the common set of horizontal plates. 59.What is the principle of sampling oscilloscope?.(May/June 2010) Using sampling procedure, high frequency signal is converted to the low frequency signal. Thus instead of monitoring the input s ...

Position, Velocity, and Acceleration Sensors

... Note in Figure PVA-6 that Channel A "lags" behind Channel B by 1/4 of a cycle (or 90 “electrical” degrees) if the disk is rotated in the clockwise direction. If the direction of rotation is reversed, then Channel B would "lag" behind Channel A. By determining which channel “lag” the other, the direc ...

... Note in Figure PVA-6 that Channel A "lags" behind Channel B by 1/4 of a cycle (or 90 “electrical” degrees) if the disk is rotated in the clockwise direction. If the direction of rotation is reversed, then Channel B would "lag" behind Channel A. By determining which channel “lag” the other, the direc ...

Slides - Indico

... Advantage is that less external components are required as all modulation can be done inside a DSP or an FPGA and a more linear response can be obtained. Disadvantage is the noise introduced by direct digital synthesis of the IF waveform. The phase noise is introduced by: •1/f Clock jitter, and as a ...

... Advantage is that less external components are required as all modulation can be done inside a DSP or an FPGA and a more linear response can be obtained. Disadvantage is the noise introduced by direct digital synthesis of the IF waveform. The phase noise is introduced by: •1/f Clock jitter, and as a ...

A 1.55 GHz to 2.45 GHz Center Frequency Continuous

... technology (B7HF200) from Infineon and occupies a chip area of 2.2 mm2. A chip photograph is shown in Fig. 5. The measurement setup consists of a Rohde&Schwarz SMF100A for the generation of the clock signal, a SMU-200 for sinusoidal and modulated RF input signals and the spectrum analyzer FSQ-8. Mea ...

... technology (B7HF200) from Infineon and occupies a chip area of 2.2 mm2. A chip photograph is shown in Fig. 5. The measurement setup consists of a Rohde&Schwarz SMF100A for the generation of the clock signal, a SMU-200 for sinusoidal and modulated RF input signals and the spectrum analyzer FSQ-8. Mea ...

A Spiking-Neuron Collective Analog Adder with Scalable Precision

... (preamplifier + high gain OTA) topology [1], except for the fact that the first stage has an additional branch for the negative input terminal. The use of this additional branch prevents charge sharing between capacitors after switching: Depending on the phase, the negative input terminal is connect ...

... (preamplifier + high gain OTA) topology [1], except for the fact that the first stage has an additional branch for the negative input terminal. The use of this additional branch prevents charge sharing between capacitors after switching: Depending on the phase, the negative input terminal is connect ...

Lab 2 Applications of the 555 Timer

... This section was very similar to the circuit built with the 555 timer-based oscillator however, with a 2N3906 transistor added to the circuit which permits the continuous charge of capacitor C2=100nF. A circuit was constructed according to figure 3 below. Using the same multimeter, the 3.3kΩ resisto ...

... This section was very similar to the circuit built with the 555 timer-based oscillator however, with a 2N3906 transistor added to the circuit which permits the continuous charge of capacitor C2=100nF. A circuit was constructed according to figure 3 below. Using the same multimeter, the 3.3kΩ resisto ...

GENERAL DESCRIPTION FEATURES

... correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on.) Illogical time and date entries result in undefined operation. Bit 7 of Register 0 is the clock halt (CH) bit. When this bit is set to 1, the oscillator is disabled. Whe ...

... correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on.) Illogical time and date entries result in undefined operation. Bit 7 of Register 0 is the clock halt (CH) bit. When this bit is set to 1, the oscillator is disabled. Whe ...

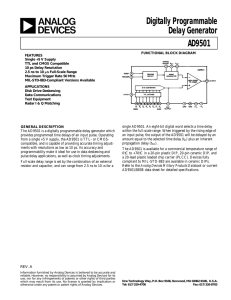

AD9501 Digitally Programmable Delay Generator

... wider pulses are required, a delay can be inserted between OUTPUT and RESET. If preferred, an external pulse can be used as a reset input to control the timing of the falling edge (and consequently, the width) of the delayed output. Multiple Signal Path Deskewing ...

... wider pulses are required, a delay can be inserted between OUTPUT and RESET. If preferred, an external pulse can be used as a reset input to control the timing of the falling edge (and consequently, the width) of the delayed output. Multiple Signal Path Deskewing ...

$doc.title

... The VCO outputs are taken from noncritical, highly buffered portions of the loop to minimize loading. The 3:1 frequency range of the circuit guarantees 2-to-3-GHz operation across process, temperature, and power supply variations. The main tuning input is prefiltered by two 100-MHz poles to reduce s ...

... The VCO outputs are taken from noncritical, highly buffered portions of the loop to minimize loading. The 3:1 frequency range of the circuit guarantees 2-to-3-GHz operation across process, temperature, and power supply variations. The main tuning input is prefiltered by two 100-MHz poles to reduce s ...

In this lesson we will Study the control of several different kinds of

... The timing diagram for one cycle (not full rotation) is given Such a pattern can be generated in several ways Utilize 4 digital output lines from the microprocessor Base the signal timing on an internal timer Utilize 2 digital output lines from the microprocessor and an external decoder That will ma ...

... The timing diagram for one cycle (not full rotation) is given Such a pattern can be generated in several ways Utilize 4 digital output lines from the microprocessor Base the signal timing on an internal timer Utilize 2 digital output lines from the microprocessor and an external decoder That will ma ...

EE3306_68HC11_Lab4 - Electrical and Computer Engineering

... The 68HC11 A/D system is an 8 bit successive approximation converter with an input multiplexer. The A/D converter requires two reference voltages, VRL and VRH , and on the Axiom board, they are connected to 0V and +5V, respectively. A conversion requires 32-E clock cycles to complete. Before you can ...

... The 68HC11 A/D system is an 8 bit successive approximation converter with an input multiplexer. The A/D converter requires two reference voltages, VRL and VRH , and on the Axiom board, they are connected to 0V and +5V, respectively. A conversion requires 32-E clock cycles to complete. Before you can ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.