* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download An Asynchronous Delta-Sigma Converter Implementation

Stray voltage wikipedia , lookup

Audio power wikipedia , lookup

Spectral density wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Ground loop (electricity) wikipedia , lookup

Voltage optimisation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Dynamic range compression wikipedia , lookup

Alternating current wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Oscilloscope types wikipedia , lookup

Television standards conversion wikipedia , lookup

Mains electricity wikipedia , lookup

Power inverter wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Power electronics wikipedia , lookup

Schmitt trigger wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Buck converter wikipedia , lookup

Integrating ADC wikipedia , lookup

An Asynchronous Delta-Sigma Converter

Implementation

Dazhi Wei, Student Member IEEE, Vaibhav Garg, Student Member IEEE and John G. Harris, Member IEEE

Department of Electrical and Computer Engineering, University of Florida,Gainesville

Email: {dazhiwei, vaibhavg, jgharris} @ufl.edu

Abstract— In this paper an architecture, signal reconstruction

algorithm and first-ever implementation of an asynchronous

delta-sigma converter are presented. The signal reconstruction

algorithm can mathematically perfectly reconstruct the original

signal only using timing events. A prototype circuit designed and

fabricated in a standard 0.5 µm CMOS process with a 5V power

supply is presented. The tests show that an 8-bit resolution with

6kHz signal bandwidth and only 715 µm power consumption is

possible.

I. I NTRODUCTION

There is great interest in reducing the power and/or increasing the speed of delta-sigma analog-to-digital converters

(ADCs). Continuous-time delta-sigma modulation is one avenue to increase converter speed by using a continuous-time

integrator but keeping the clocked quantizer [1]. Alternatively

Allier et al have designed a new class of asynchronous ADCs

based on level crossing sampling and time quantization [2]

but do not present a reconstruction algorithm to convert non

uniformly sampled sequences to uniformly sampled sequences.

Asynchronous delta-sigma converters which means converters

without clocks of any kind [3], [4] on the other hand,

have promise for ultra-low power consumption because of the

extreme simplicity of the required analog circuitry without any

oversampling requirements.

x(t )

y (ti )

Vdd

gm

dt

C ³

0

Vrl

Vrh

Integrator

Schmidt trigger

a

-a

high

low

1-bit DAC

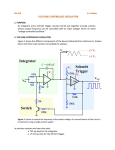

Fig. 1.

Architecture of the asynchronous delta-sigma converter

Figure 1 shows the architecture of a typical asynchronous

delta-sigma converter based on the scheme proposed by Lazar

and Toth [4].This architecture does not use a clock to sample

the analog signal, and no quantization operation is involved

during the data conversion. The difference between the input

signal x(t) and the fedback analog value corresponding to

the Schmitt trigger output y(ti ) is continuously integrated.

The Schmitt trigger output y(ti ) switches from low to high

if the integrator output rises above the high reference voltage

Vrh , switches from high to low if the integrator output drops

below the low reference voltage Vrl , and otherwise remains

unchanged. If there are no nonidealities during the data

conversion, the information in the analog signal is losslessly

encoded in the transition timings ti of the Schmitt trigger

output. The asynchronous converter described here requires

no oversampling in principle, however a small amount of

oversampling increases the signal to noise ratio (SNR) in

practice.

II. S IGNAL R ECONSTRUCTION A LGORITHM

The Schmitt trigger output is discrete in amplitude and

continuous in time and necessitates time quantization to obtain

digital output. Moreover, since most current digital systems

can only process uniformly sampled data, the nonuniform

nature of the Schmitt trigger output requires another signal

processing block to convert to a uniformly sampled sequence

for subsequent digital processing. The overall ADC performance is not only dependent on the accuracy of the encoding

circuit, but also on the efficiency of the signal reconstruction

block. We have implemented a variation of the reconstruction

algorithm proposed by Lazar and Toth [4] which has roots

in mathematical frame theory [5]. We have also applied our

algorithm to reconstruct signals from a variety of hardware

spiking neuron models [6]. We assume the input signal x(t) is

bandlimited to [−Ωs , Ωs ], and therefore can be expressed as

a sum of weighted Sinc functions:

sin(Ωs (t − sj ))

(1)

wj

x(t) =

Ωs (t − sj )

j

if the maximum interval between adjacent sj is less than the

Nyquist period π/Ωs . Here wj is the scalar weight of the Sinc

function at time sj .

The encoding operation of the converter can be summarized

as

ti+2

x(t)dt = (−1)i a(2ti+1 − ti+2 − ti )

(2)

ti

We can substitute Equation 1 into Equation 2, and obtain a

system of linear equations

wj cij = (−1)i a(2ti+1 − ti+2 − ti )

(3)

j

where coefficients

cij =

ti+2

ti

sin(Ωs (t − sj ))

dt

Ωs (t − sj )

(4)

Vdd

Vb1

M9

M5

M11

M10

M10

M3

M0

M4

M7

M2

M1

Vb0

Vin+

M3

M12

M14

Vref

Vin

Vout

VCM a

Vdd

Vb1

M8

Vin-

Schmitt trigger

output

Vb2

M6

M4

M5

DAC

output

M0

M2

Vb

M11

M1

M12

C

M13

M14

M8

M6

M7

Gnd

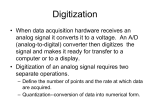

Fig. 2.

Fig. 3.

are constants depending only on the transition timings ti , and

sj = (tj + tj+2 )/2 . Finally we solve Equation 3 to obtain the

weights wj , and then use Equation 1 to reconstruct the signal

x(t). From Equation 3 we can see that the reconstructed signal

is only dependent on the DAC output a and the Schmitt trigger

output transition timings ti and is immune to process variation

or other device parameters such as Gm , C, and (Vrh − Vrl ).

The sufficient condition to meet the bandwidth requirement

in Equation 1 is that the maximum interval between adjacent

timings sj and sj+1 , or equivalently between adjacent transition timings ti and ti+1 , is less than π/Ωs . We can show that

the condition for all signals which requires that the magnitude

of signal x(t) be bounded by

C(Vrh − Vrl )Ωs

πGm

M13

Gnd

Circuit Implementation of Integrator

|x(t)| ≤ a −

M9

(5)

III. CIRCUIT IMPLEMENTATION

A. Integrator

The integrator shown in Figure 2 is implemented with a

transconductance amplifier Gm [7] with a capacitive load C.

Two PMOS transistors M5 and M6 working in the triode

region provide a conductance with a wide linear region. Since

transistors M1 and M2 have smaller W/L ratios compared to

the load transistors M3 and M4 and the corresponding voltage

gain gm1/gm3 is less than one, the linear input region of

the integrator is further increased. A larger linear input region

is critical since it means larger allowable signal power with

decreased high-order harmonic distortions introduced in the

signal band. However this decrease in harmonic distortion is

at the cost of more input referred noise. Therefore transistor

sizes must be chosen carefully to make the tradeoff between

linearity and

The transconductance can be written as

noise.

µn (W/L)1

Gm = 4β5 2IβB1

µp (W/L)3 , and can be tuned via the bias

7

current IB1 after fabrication.

B. Schmitt Trigger

The circuit implementations of a novel Schmitt trigger and

the 1-bit DAC are shown in Figure 3. The Schmitt trigger is

M15

VCM a

Circuit of the Schmitt trigger (M0-13) and the 1-bit DAC (M14-15)

very simple and does not require any resistors. The second differential input pair (M0-3) is introduced to a transconductance

amplifier (M4-13) to form the positive feedback that provides

hysteresis. The inverter (M12-13) is needed to increase the

loop gain and to produce the digital output. It turns out Ib1 has

to be larger than Ib2 for proper operation. The Schmitt trigger

works as follows. Assuming initially the output Vout is low and

the input Vin is much lower than the reference Vref , transistors

M1 and M5 are off and transistors M2 and M4 are on. Current

Ib1 flows through M4 and the current Ib2 through M2 and thus

Ib1 + Ib2 flows through M6 while no current flows through

transistors M1, M5 and M7, and the output Vout is kept low.

If Vin decreases it will not change the current flow and thus not

affect this state. If Vin increases, current begins to switch from

M4 to M5, and thus current through M6 increases and current

through M7 decreases. Once the currents through M6 and M7

are both equal to (Ib1 + Ib2 )/2, an increase in Vin will cause

more current to flow through M7 than M6, and thus cause

the output Vout to increase. Meanwhile the increase of Vout

will also switch more current from M2 to M1, which further

causes more current to flow through M7 than M6. A positive

feedback mechanism is activated and Vout is exponentially

increased from low to high. Similar analysis can be applied

to the case of switching Vout from high to low. It turns out

that the high and low reference voltages are the input voltages

which cause the current through M4 to equal (Ib1 − Ib2 )/2

and (Ib1 + Ib2 )/2 respectively. For above-threshold square-law

operation we can obtain the reference voltage swing vrh − vrl

as

√

√

2( Ib1 + Ib2 − Ib1 − Ib2 )

(6)

Vrh − Vrl =

µCox (W/L)4

which can be tuned via bias currents after fabrication. We can

also derive the transconductance of the Schmitt trigger at the

switching points as

gm

=

2

1/gm4 + 1/gm6

1

(Ib1 −Ib2 )µCox (W/L)4

2 − I2

2 Ib1

b2

√

2

+√

√

√

µCox (W/L)4

(7)

Ib1 + Ib2 + Ib1 − Ib2

The 1-bit DAC is just a simple inverter with sources connected to appropriate analog voltages VCM + a and VCM − a.

VCM is the common mode voltage and a is half of the full

scale analog voltage, which are determined by the input linear

region of the integrator.

=

60

1

(Ib1 +Ib2 )µCox (W/L)4

50

40

SNR (dB)

=

30

20

10

C. Non Idealities and Tradeoffs

The signal reconstruction algorithm discussed in section II

assumed that the integrator is ideal. However in practice the

amplifier has finite output resistance which results in a leaky

integrator and we must consider its effect in the reconstruction.

Assuming the output resistance of the amplifier is R, the

integration operation is described by

Vo

Vo

dVo

= Gm Vi −

= Gm (Vi −

)

(8)

dt

R

ADC

where ADC = Gm R is the DC voltage gain of the transconductance amplifier and Vo and Vi are output and input voltages

respectively. The last term in Eq. 8 represents the non ideality

and we need to give guidelines on how to minimize its

effect on the output. Mathematically we can achieve perfect

reconstruction for the converter with the leaky integrator if

all the parameters a, R, and C and transition timings ti are

known using

ti+1 −ti+2

ti −ti+1

wj cij = (−1)i aRC(e RC

− e RC )

(9)

C

j

where cofficients

ti+1

sin(Ωs (t − sj )) t−ti+1

e RC dt+

cij =

Ωs (t − sj )

t

i

ti+2

sin(Ωs (t − sj )) t−ti+2

e RC dt

Ωs (t − sj )

ti+1

(10)

are constants depending only on the transition timings ti , and

sj = (tj + tj+2 )/2. However in practice the output resistance

R is usually a signal and process dependent term ro = 1/λI

and exhibits some nonlinearity and unpredictability, moreover,

the algorithm is sensitive to the estimated value of the output

resistance, therefore it is difficult to have satisfactory reconstruction using Eq. 9 and 10. However we may consider the

leaky term −Vo /ADC in Eq. 8 as input referred noise whose

variance degrades the reconstruction performance. So, from

Eq. 8 we see that higher output voltage swing(V0 ) and lower

DC gain(ADC ) would increase noise power and therefore

degrade performance. By adjusting the DC gain and output

voltage swing we can estimate the desired noise power and

hence the signal to noise ratio.

The Schmitt trigger is a critical component to perform

the sampling operation of the converter. A larger reference

voltage swing vrh − vrl is usually preferable since essentially

the performance is determined by the value of vrh − vrl

divided by reference variations caused by nonidealities such as

0

-60

-50

-40

-30

-20

-10

Sine wave amplitude (dBFS)

0

Fig. 4. Plot of the SNR vs. sine wave amplitude of the asynchronous deltasigma converter chip(the sine wave frequency is 1 kHz, the converter signal

bandwidth is 6 kHz, and 0 dBFS refers to 0.2 V full scale amplitude)

input referred noise. Larger transconductance, or equivalently

larger unity gain bandwidth with constant load capacitance, is

also preferable because the regeneration speed of the positive

feedback is faster [8] and thus the output requires less delay

to reach logical states. Actually it is the variance of the delay

that affects the reconstruction performance since the mean of

the delay can be cancelled in the algorithm. The variance of

the delay arises from its dependence on the slew rate of the

input voltage of the Schmitt trigger. The variance of the delay

is smaller for larger unity gain bandwidth which results in

better performance. It is clear from Eq 6 and 7 that a tradeoff

must be made between the reference voltage swing and the

transconductance to choose proper transistor W/L ratio for

given bias currents. Also from Eq 8 less reference voltage

swing, vrh − vrl i.e. Vo , is helpful to reduce the noise power

due to the leaky integrator, which is yet another tradeoff.

IV. CHIP TEST RESULTS

The chip was fabricated using AMI 0.5 µm CMOS Technology using MOSIS. The core die area is 27600 µm2 . For

the integrator, the capacitance is 10 pF, and the bias currents

Ib0 and Ib1 are 5 µA and 4 µA respectively, the common

mode input voltage is 2.6 V and the common mode output

voltage is 1.8 V. For the Schmitt trigger, the reference voltage

Vref is 1.8 V, the bias currents Ib1 and Ib2 are 36 µA and

26 µA, and the corresponding (vrh − vrl ) = 0.5 V. For

the 1-bit DAC, logic high and logic low correspond to 2.7

V and 2.3 V, which means a = 0.2 V. The input voltage

sine wave is x(t) = 2.5V + A sin(2πf t). A logic analyzer is

used to capture transition timings of the chip output, and then

the signal is reconstructed in Matlab to a uniformly sampled

sequence using the algorithm discussed in Section II. We have

implemented two tests to characterize the chip performance

based on the IEEE standard 1241 for ADC test [9].

a) 4-parameter sine wave fitting test: Figure 4 shows the

measured SNR vs. the amplitude of the sine wave with 1 kHz

frequency, where the signal bandwidth of the converter is 6

kHz (Ωs = 12000π rad/sec), and 0 dBFS refers to a sine wave

Differential Nonlinearity (LSB)

SNR (dB)

50

45

40

35

30 2

10

3

10

Sine wave frequency (Hz)

10

4

Fig. 5. Plot of the SNR vs. sine wave frequency of the asynchronous deltasigma converter chip(the sine wave amplitude is -2.5 dBFS)

with 0.2 V amplitude. As the sine wave amplitude increases,

the SNR increases with a slope of 1dB/1dB to reach the peak

of 51 dB at around −2.5 dBFS, and then quickly drops to

0 dB. The SNR drop is due to the increased nonlinearities

caused by the larger amplitude signal input and the frequency

aliasing caused when the maximum interval between adjacent

transition timings grows larger than the Nyquist period π/Ωs .

We conclude that the chip can achieve 51 dB SNR (more

than 8-bit resolution). The power consumption of the chip

excluding pads and buffers is around 715 uW. In order to show

that the performance is consistent for different frequencies, we

also provide a plot of the SNR vs. the frequency of the sine

wave with a −2.5 dBFS amplitude in Figure 5. The SNR is

above 50 dB for frequencies up to 6 kHz bandwidth.

b) Sine wave histogram test: Sine wave histogram testing

is also performed to measure the differential nonlinearity

(DNL) and integral nonlinearity (INL).The input signal to the

chip is a sine wave with a 1 kHz frequency and a −2.5dBFS

amplitude. The sampling frequency of the reconstructed signal

is not harmonically related to the sine wave frequency as

required by the IEEE standard 1241. With the assumption of

8 bit resolution, the nonlinearities are calculated and plotted

in Figure 6. We can see both DNL and INL are less than 1

LSB, which verifies that the chip achieves an 8-bit resolution.

V. C ONCLUSION

We have shown how to implement an asynchronous deltasigma converter for analog to digital conversion. The schmitt

trigger presented here is a completely novel idea.To the best of

our knowledge, this implementation is the first asynchronous

delta-sigma converter chip to have been successfully built for

analog to digital conversion. We believe this architecture has

promise for low power consumption because of the extreme

simplicity of the required analog circuitry and no need for high

oversampling. The circuit design can be improved to lower

power requirements and increase usable input linear region

for AC signal.

Integral Nonlinearity (LSB)

55

1

0.5

0

-0.5

-1

0

50

100

150

200

250

0

50

100

150

Output Code

200

250

1

0.5

0

-0.5

-1

Fig. 6. Plots of the DNL and INL from the sine wave histogram test of the

asynchronous delta-sigma converter chip

The overall ADC performance is determined by the accuracy of the sample time and will take advantage of the

faster circuitry provided by the VLSI process scaling. Since

the nonuniform sample sequence is discrete in amplitude and

robust to transmission noise, the sample sequence can be transmitted out of the converter front end and the reconstruction

algorithm can be run remotely in locations where power and

circuit size are not a big issue. These characteristics determine

that the asynchronous delta-sigma converter will likely be

suitable for power limited applications such as remote sensing

and implanted biomedical devices.

R EFERENCES

[1] J. Cherry and W. Snelgrove, Continuous-time Delta-Sigma Modulators

for High-speed A/D Conversion: Theory, Practice, and Fundamental

performance Limits., Kluwer Academic Publishers, Boston, 1999.

[2] E. Allier, G. Sicard, L. Fesquet, and M. Renaudin, “A new class of

asynchronous A/D converters based on time quantization,” in Proceedings of the Ninth International Symposium on Asynchronous Circuits

and Systems, Vancouver, May 2003, pp. 196-205.

[3] E. Roza, “Analog-to-digital conversion vis duty-cycle modulation,”

IEEE Transactions on Circuits and Systems II: Analog and Digital

Signal Processing, vol. 44, no. 11, pp. 907-914, November 1997.

[4] A. Lazar and L. Toth, “Time encoding and perfect recovery of

bandlimited signals,” in IEEE International Conference on Acoustics,

Speech, and Signal Processing, April 2003, vol. 6, pp. 709-712.

[5] H. Feichtinger and K. Gröchenig, “Theory and practice of irregular

sampling,” in Wavelets: Mathematics and Applications, J. Benedetto and

M. Frazier, Eds., Boca Raton, FL, 1994, pp. 305-363.

[6] D. Wei and J. Harris, “Signal reconstruction from spiking neuron models,” in Proceedings of the 2004 International Symposium on Circuits

and Systems, vol. 5, Vancouver, May 2004, pp. 353-356.

[7] A. Lopez-Mietin, A. Carlosena, and J. Ramirez-Angulo, “Versatile cmos

and bicmos linear transconductor circuits,” vol. 2, August 1999, pp.

1024-1027.

[8] T. Kacprzak and A. Albicki, “Analysis of metastable operation in RS

CMOS flip-flops,” IEEE Journal of Solid-State Circuits, vol. SC22, no. 1,

pp. 57-64, February 1987.

[9] IEEE Standard for Terminology and Test Methods for Analog-to-Digital

Converters. New York: IEEE, December 2000.

[10] J. Márkus, “ADC test data evaluation program for matlab,”

http://www.mit.bme.hu/projects/adctest, May 2004.

[11] J. Doernberg, H. Lee, and D. Hodges, “Full-speed testing of A/D

converters,” IEEE Journal of Solid-State Circuits, vol. SC19, no. 6, pp.

820-827, December 1984.