Method of making semiconductor memory device

... resistivity, with the drain of the MISFET Q1, the source of the MISFET Q3 and the gate electrode of the MIS of one bit will be described with reference to FIG. 6. 20 FET Q2, all of which are shown in FIG. 5. In other In FIG. 6, a section surrounded by a rectangle words, the second poly-Si layer 147 ...

... resistivity, with the drain of the MISFET Q1, the source of the MISFET Q3 and the gate electrode of the MIS of one bit will be described with reference to FIG. 6. 20 FET Q2, all of which are shown in FIG. 5. In other In FIG. 6, a section surrounded by a rectangle words, the second poly-Si layer 147 ...

ELEC 516 VLSI System Design and Design Automation Fall

... • To achieve high very high density memories, area is of premier importance. • If compared to FF & latches, the memory cells trades performance and reliability for reduced area. • Memory design relies on the peripheral circuitry to recover both speed and electrical integrity. • A good designer can m ...

... • To achieve high very high density memories, area is of premier importance. • If compared to FF & latches, the memory cells trades performance and reliability for reduced area. • Memory design relies on the peripheral circuitry to recover both speed and electrical integrity. • A good designer can m ...

pptx

... (1) Draw a state diagram (e.g. Moore Machine) (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs ...

... (1) Draw a state diagram (e.g. Moore Machine) (2) Write output and next-state tables (3) Encode states, inputs, and outputs as bits (4) Determine logic equations for next state and outputs ...

Phase II report - cs.Virginia

... thermal sensors, IO pads). The LEF file is generated by Cadence Abstract Generator. The first part of this file describes technology related information such as metal/via width and pitch. It also includes via generation rules to be used by routing interconnects in Encounter. In the LEF file for our ...

... thermal sensors, IO pads). The LEF file is generated by Cadence Abstract Generator. The first part of this file describes technology related information such as metal/via width and pitch. It also includes via generation rules to be used by routing interconnects in Encounter. In the LEF file for our ...

SRC/NSF/A*STAR Forum on 2020 Semiconductor Memory

... level‐two memory for many product generations. Like the SRAM, the DRAM is a volatile memory element that must continuously be refreshed due to charge leakage from the storage capacitor. As feature sizes continue to be scaled, the degraded cell transistor consumes more leakage current requiring ...

... level‐two memory for many product generations. Like the SRAM, the DRAM is a volatile memory element that must continuously be refreshed due to charge leakage from the storage capacitor. As feature sizes continue to be scaled, the degraded cell transistor consumes more leakage current requiring ...

F-RAM Technology Brief - Cypress Semiconductor

... Ferroelectric Property The ferroelectric property is a phenomena observed in a class of materials such as Lead Zirconate Titanate (PZT). PZT has perovskite crystal structure shown in Figure 1. The cation in the center has two equal and stable low-energy states. These states determine the position of ...

... Ferroelectric Property The ferroelectric property is a phenomena observed in a class of materials such as Lead Zirconate Titanate (PZT). PZT has perovskite crystal structure shown in Figure 1. The cation in the center has two equal and stable low-energy states. These states determine the position of ...

ppt - Computer Science Division - University of California, Berkeley

... – Origin of the term “Dump Core” – Rumor that IBM consulted Life Saver company ...

... – Origin of the term “Dump Core” – Rumor that IBM consulted Life Saver company ...

Lecture1 Introduction - University of California, Berkeley

... – RAS cycle fetched rows of data from cell array blocks (long access time, around 100ns) – Subsequent CAS cycles quickly access data from row buffers if within an address page (page is around 256 Bytes) ...

... – RAS cycle fetched rows of data from cell array blocks (long access time, around 100ns) – Subsequent CAS cycles quickly access data from row buffers if within an address page (page is around 256 Bytes) ...

Computer Organization And Architecture Srm

... parallel with CPU, thus improving the performance • Invention of the transistor which was faster, smaller and required considerably less power to operate ...

... parallel with CPU, thus improving the performance • Invention of the transistor which was faster, smaller and required considerably less power to operate ...

Computers

... The main memory is made up of logic gates The main memory is organised in terms of cells and ...

... The main memory is made up of logic gates The main memory is organised in terms of cells and ...

Dynamic Random Access Memories (DRAMs)

... Memory ─ A collection of storage cells together with the necessary circuits to transfer information to and from them. Directly or indirectly connected to the CPU via a memory bus Comprises of two buses: an address bus and a data bus The CPU firstly sends a number through an address bus, a number cal ...

... Memory ─ A collection of storage cells together with the necessary circuits to transfer information to and from them. Directly or indirectly connected to the CPU via a memory bus Comprises of two buses: an address bus and a data bus The CPU firstly sends a number through an address bus, a number cal ...

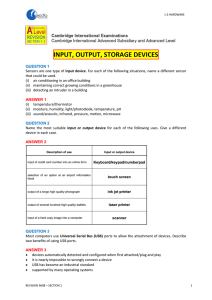

INPUT, OUTPUT, STORAGE DEVICES - GCE-AL

... Before a program can be ran it must first be loaded into RAM which allows the CPU to access the program. QUESTION 2 Briefly describe the term ‘ROM’. ANSWER 2 ROM holds the instructions for starting up the computer. This type of memory can only be read and cannot be altered (delete or written). It is ...

... Before a program can be ran it must first be loaded into RAM which allows the CPU to access the program. QUESTION 2 Briefly describe the term ‘ROM’. ANSWER 2 ROM holds the instructions for starting up the computer. This type of memory can only be read and cannot be altered (delete or written). It is ...

Understanding DRAM Operation

... Write Enable (WE) The write enable signal is used to choose a read operation or a write operation. A low voltage level signifies that a write operation is desired; a high voltage level is used to choose a read operation. The operation to be performed is usually determined by the voltage level on WE ...

... Write Enable (WE) The write enable signal is used to choose a read operation or a write operation. A low voltage level signifies that a write operation is desired; a high voltage level is used to choose a read operation. The operation to be performed is usually determined by the voltage level on WE ...

Low voltage, scalable nanocrystal FLASH memory

... Flash chips are made on silicon wafers using a process that takes 6-12 weeks and hundreds of manufacturing steps. The process requires multiple uses of photolithography, etch, diffusion, thin film deposition, planarization, and ion implantation. The width of the Control/Floating Gates will avera ...

... Flash chips are made on silicon wafers using a process that takes 6-12 weeks and hundreds of manufacturing steps. The process requires multiple uses of photolithography, etch, diffusion, thin film deposition, planarization, and ion implantation. The width of the Control/Floating Gates will avera ...

Ovonic unified memory.doc

... Almost 25% of the world wide chip markets are memory devices, each type used for their specific advantages: the high speed of an SRAM, the high integration density of a DRAM, or the nonvolatile capability of a FLASH memory device.The industry is searching for a holy grail of future memory technologi ...

... Almost 25% of the world wide chip markets are memory devices, each type used for their specific advantages: the high speed of an SRAM, the high integration density of a DRAM, or the nonvolatile capability of a FLASH memory device.The industry is searching for a holy grail of future memory technologi ...

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

... systems designers have become more creative in their use of cache memory, inter leaving, burst mode and other high-speed methods for accessing memory. The old systems sporting just an on-chip instruction cache, a moderate amount of DRAM and a hard drive have given way to sophisticated designs using ...

... systems designers have become more creative in their use of cache memory, inter leaving, burst mode and other high-speed methods for accessing memory. The old systems sporting just an on-chip instruction cache, a moderate amount of DRAM and a hard drive have given way to sophisticated designs using ...

A Typical Die Photo A Closer Look at that Die Photo A Multicore Die

... • Large storage arrays cannot be implemented “digitally” • Muxing and wire routing become impractical ...

... • Large storage arrays cannot be implemented “digitally” • Muxing and wire routing become impractical ...

OUM Ovonic Unified Memory

... memory (OUM), is based on rapid reversible phase change effect in materials under the influence of electric current pulses. The OUM uses the reversible structural phase-change in thin-film material (e.g., chalcogenides) as the data storage mechanism. The small volume of active media acts as a progra ...

... memory (OUM), is based on rapid reversible phase change effect in materials under the influence of electric current pulses. The OUM uses the reversible structural phase-change in thin-film material (e.g., chalcogenides) as the data storage mechanism. The small volume of active media acts as a progra ...

week11

... Can be read from but not written to, by a processor in an embedded system Traditionally written to, “programmed”, before inserting to embedded system ...

... Can be read from but not written to, by a processor in an embedded system Traditionally written to, “programmed”, before inserting to embedded system ...

Chapter 1 Introduction 1.1 Overview of Nonvolatile Memory

... bios, and DVD player. NAND type flash memory [1.2] h as been targeted at data storage market, which is an emerging application such as PDA, memory cards, MP3 audio players, digital cameras, and USB flash personal disc. These products all are based on flash memory that is nonvolatile and can keep sto ...

... bios, and DVD player. NAND type flash memory [1.2] h as been targeted at data storage market, which is an emerging application such as PDA, memory cards, MP3 audio players, digital cameras, and USB flash personal disc. These products all are based on flash memory that is nonvolatile and can keep sto ...

Future Memory Devices

... the magnetic polarization does not leak away with time like charge does, so information is stored even when the power is turned off switching the magnetic polarization between the two states does not involve actual movement of electrons or atoms and thus has no known wear-out mechanism ...

... the magnetic polarization does not leak away with time like charge does, so information is stored even when the power is turned off switching the magnetic polarization between the two states does not involve actual movement of electrons or atoms and thus has no known wear-out mechanism ...

DDR Memories Comparison and overview

... input receiver is a differential stage requiring a reference bias midpoint, VREF. Therefore, it requires an input voltage termination capable of sourcing as well as sinking current. This last feature differentiates the DDR VTT from other terminations present on the computer motherboard. The terminat ...

... input receiver is a differential stage requiring a reference bias midpoint, VREF. Therefore, it requires an input voltage termination capable of sourcing as well as sinking current. This last feature differentiates the DDR VTT from other terminations present on the computer motherboard. The terminat ...

Introducing LRDIMM – A New Class of Memory Modules

... the memory buffer on each LRDIMM located between the memory controller and the DRAM, rather than having all DRAM on all RDIMMs on a given memory channel connected directly to the memory controller. This allows for power-saving termination options for DRAM located on non-target LRDIMMs that are not p ...

... the memory buffer on each LRDIMM located between the memory controller and the DRAM, rather than having all DRAM on all RDIMMs on a given memory channel connected directly to the memory controller. This allows for power-saving termination options for DRAM located on non-target LRDIMMs that are not p ...

AN1879 Application note How to use M41ST87 tamper detect and RAM clear Introduction

... the TEB and CLREXT bits in the tamper registers. To clear/corrupt the external memory, VCC of the SRAM can be taken to ground. However, certain SRAMs require a significant amount of time for the memory to be corrupted if VCC is simply grounded. To corrupt the memory in a reasonable amount of time, o ...

... the TEB and CLREXT bits in the tamper registers. To clear/corrupt the external memory, VCC of the SRAM can be taken to ground. However, certain SRAMs require a significant amount of time for the memory to be corrupted if VCC is simply grounded. To corrupt the memory in a reasonable amount of time, o ...

Design and Testing of Semiconductor Memories

... System selects memory with /CS=L System waits a minimum time equal to internal setup time of new addresses (tAS) System enables writing with /WE=L System waits for minimum time to disable o/p driver (twz) System inputs data and waits minimum time (tDW) for data to be written in core, then turns off ...

... System selects memory with /CS=L System waits a minimum time equal to internal setup time of new addresses (tAS) System enables writing with /WE=L System waits for minimum time to disable o/p driver (twz) System inputs data and waits minimum time (tDW) for data to be written in core, then turns off ...

Random-access memory

Random-access memory (RAM /ræm/) is a form of computer data storage. A random-access memory device allows data items to be accessed (read or written) in almost the same amount of time irrespective of the physical location of data inside the memory. In contrast, with other direct-access data storage media such as hard disks, CD-RWs, DVD-RWs and the older drum memory, the time required to read and write data items varies significantly depending on their physical locations on the recording medium, due to mechanical limitations such as media rotation speeds and arm movement delays.Today, random-access memory takes the form of integrated circuits. RAM is normally associated with volatile types of memory (such as DRAM memory modules), where stored information is lost if power is removed, although many efforts have been made to develop non-volatile RAM chips. Other types of non-volatile memory exist that allow random access for read operations, but either do not allow write operations or have limitations on them. These include most types of ROM and a type of flash memory called NOR-Flash.Integrated-circuit RAM chips came into the market in the late 1960s, with the first commercially available DRAM chip, the Intel 1103, introduced in October 1970.