Memory technology evolution

... and explores the different dynamic random access memory (DRAM) technologies. Processors use system memory to store the operating system, applications, and data they use and manipulate. As a result, speed and bandwidth of the system memory controls application performance. Over the years, the need fo ...

... and explores the different dynamic random access memory (DRAM) technologies. Processors use system memory to store the operating system, applications, and data they use and manipulate. As a result, speed and bandwidth of the system memory controls application performance. Over the years, the need fo ...

Memory Design

... DRAM requires a sense amplifier for each bit line, due to charge redistribution read-out. DRAM memory cells ll are single-ended i l d d in i contrast to SRAM cells. The read-out of the 1T DRAM cell is destructive; read and refresh f h operations ti are necessary for f correctt operation. ti Unl ...

... DRAM requires a sense amplifier for each bit line, due to charge redistribution read-out. DRAM memory cells ll are single-ended i l d d in i contrast to SRAM cells. The read-out of the 1T DRAM cell is destructive; read and refresh f h operations ti are necessary for f correctt operation. ti Unl ...

Towards Complexity-Effective Intelligent Prefetchers

... Memory capacity requirements are increasing at a very fast rate. Management of high currents is crucial for effective deployment of new technologies. This thesis hypothesizes that architecture/OS policies for data placement can help manage some of the problems posed by high currents. Enabling Big Me ...

... Memory capacity requirements are increasing at a very fast rate. Management of high currents is crucial for effective deployment of new technologies. This thesis hypothesizes that architecture/OS policies for data placement can help manage some of the problems posed by high currents. Enabling Big Me ...

Equipment for measuring cosmic-ray effects on DRAM Per-Axel Jonsson

... development, even though it is the biggest source of errors in the memories. When the design is made it is expensive and therefore often not possible to change the type of memory used to achieve better cosmic-ray effects properties. This is why it is important for electronic designers to become awar ...

... development, even though it is the biggest source of errors in the memories. When the design is made it is expensive and therefore often not possible to change the type of memory used to achieve better cosmic-ray effects properties. This is why it is important for electronic designers to become awar ...

M262 Putting Computers Systems to Work

... survived competition from semiconductor memories, which have the clear advantages of simple construction with no moving parts to wear out or get damaged by mechanical shock, together with fast access times. In fact, magnetic disks have made remarkable leaps in capacity and ...

... survived competition from semiconductor memories, which have the clear advantages of simple construction with no moving parts to wear out or get damaged by mechanical shock, together with fast access times. In fact, magnetic disks have made remarkable leaps in capacity and ...

Chapter 4 Slides

... •Additional time may be required for transients to die out on signal lines or to regenerate data if they are read destructively •Concerned with the system bus, not the processor ...

... •Additional time may be required for transients to die out on signal lines or to regenerate data if they are read destructively •Concerned with the system bus, not the processor ...

ppt - University of California, Berkeley

... – RAS cycle fetched rows of data from cell array blocks (long access time, around 100ns) – Subsequent CAS cycles quickly access data from row buffers if within an address page (page is around 256 Bytes) ...

... – RAS cycle fetched rows of data from cell array blocks (long access time, around 100ns) – Subsequent CAS cycles quickly access data from row buffers if within an address page (page is around 256 Bytes) ...

Addressing Memory Characterization Capacity and

... work well for the advanced current-based models, including effective current source model (ECSM) and composite current source (CCS), which are commonly used for timing, power, and noise at 40nm and below. ...

... work well for the advanced current-based models, including effective current source model (ECSM) and composite current source (CCS), which are commonly used for timing, power, and noise at 40nm and below. ...

Emerging Research Logic Devices1 PIDS ITWG Emerging New

... Tyler Lowrey, Energy Conversion Devices, Inc., http://www.ovonic.com ...

... Tyler Lowrey, Energy Conversion Devices, Inc., http://www.ovonic.com ...

I i )BER 1974 © Copr. 1949-1998 Hewlett-Packard Co.

... vendors of these components while they were still in development. This allowed design of the minicom puter family to proceed while vendors were still building up their capabilities to produce reliable parts in volume. Modular design of the minicomputer family was another major design goal (see Fig. ...

... vendors of these components while they were still in development. This allowed design of the minicom puter family to proceed while vendors were still building up their capabilities to produce reliable parts in volume. Modular design of the minicomputer family was another major design goal (see Fig. ...

High-Performance, Lower-Power Memory Interfaces (Whitepaper)

... are likely to continue to do so for the short term. However, the market is expected to gradually ramp up to DDR4 starting in 2014. The first DDR4s are most likely to be seen in server applications, leveraging the lower I/O voltage (1.2V) and power savings DDR4 offers, but at higher data rates than D ...

... are likely to continue to do so for the short term. However, the market is expected to gradually ramp up to DDR4 starting in 2014. The first DDR4s are most likely to be seen in server applications, leveraging the lower I/O voltage (1.2V) and power savings DDR4 offers, but at higher data rates than D ...

CAO - E

... primarily von Neumann in design, but elements of the Harvard architecture are commonly seen as well. Being digital devices, all CPUs deal with discrete states and therefore require some kind of switching elements to differentiate between and change these states. Prior to commercial acceptance of the ...

... primarily von Neumann in design, but elements of the Harvard architecture are commonly seen as well. Being digital devices, all CPUs deal with discrete states and therefore require some kind of switching elements to differentiate between and change these states. Prior to commercial acceptance of the ...

EE 2310 Lecture #21 -- Memory Management in Modern Computers

... • Electromechanical data storage is normally not random-access like SRAM or DRAM. • This means that data cannot normally be accessed in arbitrary order, but must be loaded or stored according to rules, which generally have to do with positioning a recording mechanism over the correct location in an ...

... • Electromechanical data storage is normally not random-access like SRAM or DRAM. • This means that data cannot normally be accessed in arbitrary order, but must be loaded or stored according to rules, which generally have to do with positioning a recording mechanism over the correct location in an ...

Chapter # 4

... Registers usually come in 4-, 8-, or 16-bit sizes • Anything bigger takes too many I/O pins • A 1K-bit register requires over 2000 pins Asynchronous • Uses D-latches enabled by the write signal ...

... Registers usually come in 4-, 8-, or 16-bit sizes • Anything bigger takes too many I/O pins • A 1K-bit register requires over 2000 pins Asynchronous • Uses D-latches enabled by the write signal ...

Introduction to Field Programmable Gate Arrays

... •More transistors in a package larger designs •Shorter Interconnects less RC delays better chip performance •Power Decrease shorter wires reduce power consumption by producing less capacitance (also less inductance) •Bandwith large number of vertial vias between layers allow construction of ...

... •More transistors in a package larger designs •Shorter Interconnects less RC delays better chip performance •Power Decrease shorter wires reduce power consumption by producing less capacitance (also less inductance) •Bandwith large number of vertial vias between layers allow construction of ...

CX4301574577

... and hand held communication devices. SRAMs are widely used for mobile applications as both on chip and offchip memories, because of their ease of use and low standby leakage. The main objective of this paper is evaluating performance in terms of Power consumption, delay and SNM of existing 6T CMOS S ...

... and hand held communication devices. SRAMs are widely used for mobile applications as both on chip and offchip memories, because of their ease of use and low standby leakage. The main objective of this paper is evaluating performance in terms of Power consumption, delay and SNM of existing 6T CMOS S ...

M262 Putting Computers Systems to Work

... same known state, that representing a data 1 • Writing to the cells (programming the memory): setting some of the cells to the other state, that which represents a data 0. • Since the remaining cells are already in the state representing a data 1, there is no need to do anything to them ...

... same known state, that representing a data 1 • Writing to the cells (programming the memory): setting some of the cells to the other state, that which represents a data 0. • Since the remaining cells are already in the state representing a data 1, there is no need to do anything to them ...

ProjectPaper

... A high speed cache is typically used to temporarily store data that will likely be used again soon, or in between two levels of memory that would otherwise be much slower. PICo requested a high speed memory that can be used in their new mobile communications technology. The cache will only be used w ...

... A high speed cache is typically used to temporarily store data that will likely be used again soon, or in between two levels of memory that would otherwise be much slower. PICo requested a high speed memory that can be used in their new mobile communications technology. The cache will only be used w ...

Low-Power Sequential Access Memory Design

... (SAM) design where address sequencing logic and decoders are replaced with row sequencers to achieve high speed and low power. Most of the control signals are generated using efficient sequencer cells that communicate primarily with neighboring rows only, minimizing the power dissipation of wordline ...

... (SAM) design where address sequencing logic and decoders are replaced with row sequencers to achieve high speed and low power. Most of the control signals are generated using efficient sequencer cells that communicate primarily with neighboring rows only, minimizing the power dissipation of wordline ...

pptx

... Each cell stores one bit, and requires 4 – 8 transistors (6 is typical) Read: • pre-charge B and B to Vsupply/2 • pull word line high • cell pulls B or B low, sense amp detects voltage difference Write: • pull word line high • drive B and B to flip cell ...

... Each cell stores one bit, and requires 4 – 8 transistors (6 is typical) Read: • pre-charge B and B to Vsupply/2 • pull word line high • cell pulls B or B low, sense amp detects voltage difference Write: • pull word line high • drive B and B to flip cell ...

A Compact Coincident

... line causes a small rotation even though it is not large enough to cause the core element to switch. However, by rotating the sense winding by a slight angle it is possible to cancel delta noise completely irrespective of the digit distribution in the memory. This is achieved by positioning the sens ...

... line causes a small rotation even though it is not large enough to cause the core element to switch. However, by rotating the sense winding by a slight angle it is possible to cancel delta noise completely irrespective of the digit distribution in the memory. This is achieved by positioning the sens ...

Crucial® Ballistix® Tactical Series Memory Product Flyer

... heat spreader for improved thermal design and heat dissipation, the Ballistix Tactical series is designed to keep pace with power systems. ...

... heat spreader for improved thermal design and heat dissipation, the Ballistix Tactical series is designed to keep pace with power systems. ...

pptx

... Each cell stores one bit, and requires 4 – 8 transistors (6 is typical) Read: • pre-charge B and B to Vsupply/2 • pull word line high • cell pulls B or B low, sense amp detects voltage difference Write: • pull word line high • drive B and B to flip cell ...

... Each cell stores one bit, and requires 4 – 8 transistors (6 is typical) Read: • pre-charge B and B to Vsupply/2 • pull word line high • cell pulls B or B low, sense amp detects voltage difference Write: • pull word line high • drive B and B to flip cell ...

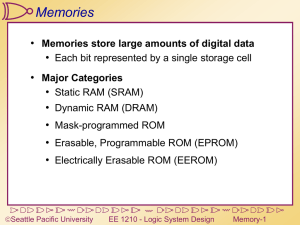

Random-access memory

Random-access memory (RAM /ræm/) is a form of computer data storage. A random-access memory device allows data items to be accessed (read or written) in almost the same amount of time irrespective of the physical location of data inside the memory. In contrast, with other direct-access data storage media such as hard disks, CD-RWs, DVD-RWs and the older drum memory, the time required to read and write data items varies significantly depending on their physical locations on the recording medium, due to mechanical limitations such as media rotation speeds and arm movement delays.Today, random-access memory takes the form of integrated circuits. RAM is normally associated with volatile types of memory (such as DRAM memory modules), where stored information is lost if power is removed, although many efforts have been made to develop non-volatile RAM chips. Other types of non-volatile memory exist that allow random access for read operations, but either do not allow write operations or have limitations on them. These include most types of ROM and a type of flash memory called NOR-Flash.Integrated-circuit RAM chips came into the market in the late 1960s, with the first commercially available DRAM chip, the Intel 1103, introduced in October 1970.