CO-UNIT-V-Chandrashekar-MA

... displacing some block that is currently inactive. www.bookspar.com | Website for students | VTU NOTES ...

... displacing some block that is currently inactive. www.bookspar.com | Website for students | VTU NOTES ...

Operating Instructions

... should be on, As long as the Power is on after you plug the card in the ISA slot on the main board. Or else the crystal oscillation circuit is broken, and there is no OSC signal. As long as the main board is on power after you plug the card in either PCI slot or ISA slot, the LED is on. or else ther ...

... should be on, As long as the Power is on after you plug the card in the ISA slot on the main board. Or else the crystal oscillation circuit is broken, and there is no OSC signal. As long as the main board is on power after you plug the card in either PCI slot or ISA slot, the LED is on. or else ther ...

Radiant Overview - Radiant Technologies, Inc.

... Sensor. Bent 90 degrees, it generates exactly 7nC of charge, precisely the amount required to saturate one of Radiant’s Type AB 20/80 PZT or Type AD 3/20/80 PNZT thin film capacitors. ...

... Sensor. Bent 90 degrees, it generates exactly 7nC of charge, precisely the amount required to saturate one of Radiant’s Type AB 20/80 PZT or Type AD 3/20/80 PNZT thin film capacitors. ...

DH01420402045

... scaling of CMOS technology has significant impacts on SRAM cell – random fluctuation of electrical characteristics and substantial leakage current. The random fluctuation of electrical property causes the SRAM cell to have huge mismatch in transistor threshold voltage. Consequently, the static noise ...

... scaling of CMOS technology has significant impacts on SRAM cell – random fluctuation of electrical characteristics and substantial leakage current. The random fluctuation of electrical property causes the SRAM cell to have huge mismatch in transistor threshold voltage. Consequently, the static noise ...

ROM, EPROM, and EEPROM Technology

... OTP (One Time Programmable) EPROM In most applications, EPROMs are programmed one time and will never have to be erased. To reduce the cost for these applications, EPROMs may be manufactured in opaque plastic packages since the standard ceramic package of an EPROM is expensive. EPROMs that are progr ...

... OTP (One Time Programmable) EPROM In most applications, EPROMs are programmed one time and will never have to be erased. To reduce the cost for these applications, EPROMs may be manufactured in opaque plastic packages since the standard ceramic package of an EPROM is expensive. EPROMs that are progr ...

ADUC812 EVALUATION BOARD REFERENCE GUIDE

... General Purpose prototype areas are provided at the top and the bottom or the evaluation board for adding external components as required in the users application. As can be seen from the layout AVDD, AGND, DVDD and DGND tracks are provided in this prototype area. External Data Memory Interface: The ...

... General Purpose prototype areas are provided at the top and the bottom or the evaluation board for adding external components as required in the users application. As can be seen from the layout AVDD, AGND, DVDD and DGND tracks are provided in this prototype area. External Data Memory Interface: The ...

BL(1)

... Keeping cell size minimized is critical for large caches Minimum sized pull down fets (M1 and M3) – Requires minimum width and longer than minimum channel length pass transistors (M5 and M6) to ensure proper CR ...

... Keeping cell size minimized is critical for large caches Minimum sized pull down fets (M1 and M3) – Requires minimum width and longer than minimum channel length pass transistors (M5 and M6) to ensure proper CR ...

Memory and Array Circuits - Circuits and Systems

... 1T DRAM requires a sense amplifier for each bit line, due to charge redistribution read-out. DRAM memory cells are single ended in contrast to SRAM cells. The read-out of the 1T DRAM cell is destructive; read and refresh operations are necessary for correct operation. Unlike 3T cell, 1T cell require ...

... 1T DRAM requires a sense amplifier for each bit line, due to charge redistribution read-out. DRAM memory cells are single ended in contrast to SRAM cells. The read-out of the 1T DRAM cell is destructive; read and refresh operations are necessary for correct operation. Unlike 3T cell, 1T cell require ...

Control Word of 8255 8255 Design Example Interface DAC to a PC

... » Storage cells in SRAM are made of flip-flops and therefore do not require refreshing in order to keep their data » The problem is that each cell requires at least 6 transistors to build and the cell holds only one bit data » The capacity of SRAM is far below DRAM » SRAM is widely used for cache me ...

... » Storage cells in SRAM are made of flip-flops and therefore do not require refreshing in order to keep their data » The problem is that each cell requires at least 6 transistors to build and the cell holds only one bit data » The capacity of SRAM is far below DRAM » SRAM is widely used for cache me ...

Powerpoint

... » Storage cells in SRAM are made of flip-flops and therefore do not require refreshing in order to keep their data » The problem is that each cell requires at least 6 transistors to build and the cell holds only one bit data » The capacity of SRAM is far below DRAM » SRAM is widely used for cache me ...

... » Storage cells in SRAM are made of flip-flops and therefore do not require refreshing in order to keep their data » The problem is that each cell requires at least 6 transistors to build and the cell holds only one bit data » The capacity of SRAM is far below DRAM » SRAM is widely used for cache me ...

1.ddr sdram

... DDR's 2.5 V. The 1.5 V supply voltage works well with the 90 nanometer fabrication technology used in the original DDR3 chips. Some manufacturers further propose using "dual-gate" transistors to reduce leakage of current. According to JEDEC the maximum recommended voltage is 1.575 volts and should b ...

... DDR's 2.5 V. The 1.5 V supply voltage works well with the 90 nanometer fabrication technology used in the original DDR3 chips. Some manufacturers further propose using "dual-gate" transistors to reduce leakage of current. According to JEDEC the maximum recommended voltage is 1.575 volts and should b ...

Operating Instructions

... The card is named POST (Power On Self Test ) card too, it could display the error code by the result of POST ,then you would soon determine cause of the error by error codes table. Especially when the PC can’t boot operating system, or it is a black screen, or the card and motherboard couldn’t issue ...

... The card is named POST (Power On Self Test ) card too, it could display the error code by the result of POST ,then you would soon determine cause of the error by error codes table. Especially when the PC can’t boot operating system, or it is a black screen, or the card and motherboard couldn’t issue ...

Complete PDF Edition (2,711 KB)

... silicon chip. We refer to this capability as “system-on-chip” technology. System-On-Chip Development Issues As device integration scales grew through the 1980s, the enhanced performance of memory, microprocessors and logic devices boosted the performance of the systems they constituted. However, per ...

... silicon chip. We refer to this capability as “system-on-chip” technology. System-On-Chip Development Issues As device integration scales grew through the 1980s, the enhanced performance of memory, microprocessors and logic devices boosted the performance of the systems they constituted. However, per ...

PowerPoint 簡報 - National University of Kaohsiung

... • Nonvolatile memory – ROM (read only memory) • When you turn on a microcomputer system, aprogram in ROM automatically readies the computer for use and produces the initial display-screen prompt ...

... • Nonvolatile memory – ROM (read only memory) • When you turn on a microcomputer system, aprogram in ROM automatically readies the computer for use and produces the initial display-screen prompt ...

Microcomputer Systems Technology

... Offhand it would seem that a shock of 10,000 volts would be more deadly than 100 volts. But this is not so! Individuals have been electrocuted by appliances using ordinary house currents of 110 volts and by electrical apparatus in industry using as little as 42 volts direct current! The real measure ...

... Offhand it would seem that a shock of 10,000 volts would be more deadly than 100 volts. But this is not so! Individuals have been electrocuted by appliances using ordinary house currents of 110 volts and by electrical apparatus in industry using as little as 42 volts direct current! The real measure ...

DRAM pres. - cse.scu.edu

... Enables row decoder. Single word line is asserted. Connects all cells in that row to the digit lines. ...

... Enables row decoder. Single word line is asserted. Connects all cells in that row to the digit lines. ...

System and Circuit Level Power Modeling of Energy

... Tungsten TSVs are employed in our model instead of Copper TSVs, because Tungsten has a relatively low thermal impact and high resistance to electro-migration. It also has relatively low resistivity and can be used to fill the very narrow contact structures. Samsung has also used Tungsten for its fab ...

... Tungsten TSVs are employed in our model instead of Copper TSVs, because Tungsten has a relatively low thermal impact and high resistance to electro-migration. It also has relatively low resistivity and can be used to fill the very narrow contact structures. Samsung has also used Tungsten for its fab ...

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs

... Higher Productivity with the Memory Interface Generator (MIG) A complete memory controller and interface design can be generated with the MIG wizard, a software tool freely available from Xilinx as part of the CORE Generator™ tool. The MIG design flow is similar to the traditional FPGA design flow. ...

... Higher Productivity with the Memory Interface Generator (MIG) A complete memory controller and interface design can be generated with the MIG wizard, a software tool freely available from Xilinx as part of the CORE Generator™ tool. The MIG design flow is similar to the traditional FPGA design flow. ...

Challenges and Solutions for Future Main Memory

... differential clock called “Data Clock” to the DRAM module. It is routed in a topology similar to the Command/Control/Address (CCA) bus and its associated clock. The Data Clock and TRS signals are active only during data transactions and are enabled with fast turn-on times. The Data Clock oscillates ...

... differential clock called “Data Clock” to the DRAM module. It is routed in a topology similar to the Command/Control/Address (CCA) bus and its associated clock. The Data Clock and TRS signals are active only during data transactions and are enabled with fast turn-on times. The Data Clock oscillates ...

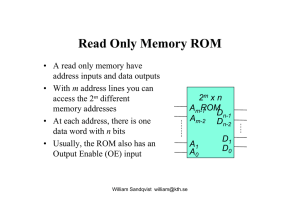

Read Only Memory ROM

... SRAM vs DRAM • SRAM takes up more space but a DRAM requires a simpler access logic and is therefore faster (but also more expensive) • DRAM is used for random access memories in our regular computers • When you remove the power you loses the contents of SRAM or DRAM memory! ...

... SRAM vs DRAM • SRAM takes up more space but a DRAM requires a simpler access logic and is therefore faster (but also more expensive) • DRAM is used for random access memories in our regular computers • When you remove the power you loses the contents of SRAM or DRAM memory! ...

Survey on Content Addressable Memory and Sparse

... CMOS circuit techniques can result in low-power and low-cost CAM’s, these designs can suffer from low noise margins, charge sharing, and other problems not to be energy efficient when scaled. Thus a new family of associative memories based on SCNs has been recently introduced and implemented using f ...

... CMOS circuit techniques can result in low-power and low-cost CAM’s, these designs can suffer from low noise margins, charge sharing, and other problems not to be energy efficient when scaled. Thus a new family of associative memories based on SCNs has been recently introduced and implemented using f ...

Memory for Dell PowerEdge 12th Generation Servers

... Note: This section is an introduction to DDR3 memory. If you already have a general understanding of DDR3, feel free to bypass this section. In any computing environment, the processor executes a series of tasks operating on a collection of data, makes decisions or calculations, and produces results ...

... Note: This section is an introduction to DDR3 memory. If you already have a general understanding of DDR3, feel free to bypass this section. In any computing environment, the processor executes a series of tasks operating on a collection of data, makes decisions or calculations, and produces results ...

CECS470

... • RWM = RAM (Random Access Memory) • Highly structured like ROMs • Can store and retrieve data at (relatively) the same speed • Static RAM (SRAM) retains data in latches (while powered) • Dynamic RAM (DRAM) stores data as capacitor charge; all capacitors must be recharged periodically (refresh). • V ...

... • RWM = RAM (Random Access Memory) • Highly structured like ROMs • Can store and retrieve data at (relatively) the same speed • Static RAM (SRAM) retains data in latches (while powered) • Dynamic RAM (DRAM) stores data as capacitor charge; all capacitors must be recharged periodically (refresh). • V ...

Programmable Logic Controllers - Goodheart

... software in ROM: – Carries out several instructions that check the input, output, and other peripheral devices connected to the CPU. – Serves as a communication interface between PLC hardware and the PLC ...

... software in ROM: – Carries out several instructions that check the input, output, and other peripheral devices connected to the CPU. – Serves as a communication interface between PLC hardware and the PLC ...

Random-access memory

Random-access memory (RAM /ræm/) is a form of computer data storage. A random-access memory device allows data items to be accessed (read or written) in almost the same amount of time irrespective of the physical location of data inside the memory. In contrast, with other direct-access data storage media such as hard disks, CD-RWs, DVD-RWs and the older drum memory, the time required to read and write data items varies significantly depending on their physical locations on the recording medium, due to mechanical limitations such as media rotation speeds and arm movement delays.Today, random-access memory takes the form of integrated circuits. RAM is normally associated with volatile types of memory (such as DRAM memory modules), where stored information is lost if power is removed, although many efforts have been made to develop non-volatile RAM chips. Other types of non-volatile memory exist that allow random access for read operations, but either do not allow write operations or have limitations on them. These include most types of ROM and a type of flash memory called NOR-Flash.Integrated-circuit RAM chips came into the market in the late 1960s, with the first commercially available DRAM chip, the Intel 1103, introduced in October 1970.