* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download LC043

Invention of the integrated circuit wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Radio transmitter design wikipedia , lookup

Integrating ADC wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Surge protector wikipedia , lookup

Operational amplifier wikipedia , lookup

Power electronics wikipedia , lookup

Voltage regulator wikipedia , lookup

Schmitt trigger wikipedia , lookup

Opto-isolator wikipedia , lookup

Integrated circuit wikipedia , lookup

History of the transistor wikipedia , lookup

Digital electronics wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Current mirror wikipedia , lookup

Rectiverter wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

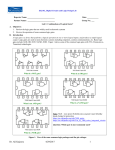

4. Logic Gates Voltage drop on resistor R2, that make currents of VT1, VT2, VT3 or VT4, prevents these transistors from saturation – it is one of reasons of high operation speed of ECL. Another reason is emitter-followers in outputs of the gate. Output resistance of emitter-follower is extremely low and it makes small time constant with sum of input capacitances of loading gates. It is necessary to answer the question, whether the emitter-followers in this circuit are indispensable, whether they improve parameters of the gate only. Voltage drop on resistor R2, which always takes place, plus voltage drop on unsaturated opened transistor is not low logic level for the transistor of loading gate. It becomes low level when it is decreased by 0.7 V – voltage drop on saturated BE junction of emitter-follower. BE junction of emitter-follower takes the role of low level restoring diode in DTL. So answer to the question is such: emitter-followers are indispensable for proper operation of gate, and they make better the properties of gate. Beside the main advantage of ECL – fast operation – large factor of pyramiding of ECL gate could be mentioned. Emitter-followers – current amplifiers – in outputs guarantee the feeding of great number of loading gates. The main disadvantages of ECL are as follows: – the greatest dissipated power of all variants of logic; – complicated circuit and large price as a result; – small logic swing and small interference immunity. I 2L Integrated injection logic (IIL or I2L) gates could not be made from discrete components, it is accentuated with the first word of this logic family name. The sense of the second word we will explain soon. The circuit of I2L gate is modified (but not changed) circuit of DCTL gate. Now we will see the way of modification. Transistors VT1 and VT2 with common collector load R1 make DCTL gate 2NOR. VT3 is an input transistor of the loading gate. Current through collector resistor of DCTL gate is nearly constant when logic level in gate's output VT +E changes: voltage drop on this resistor changes from R1 E – 0.2 V (low logic level in output) till E – 0.7 V (high F= A + B logic level in output). Only the way of current through V T3 R1 changes: either it flows through open VT1 or VT2, V T 1 V T 2 or through input circuits of loading gates. It means that B R1 can be exchanged for direct current generator – A saturated transistor VT with forward biased BE junction. 39 4. Logic Gates The circuit remains unchanged if this DC generator will be carried to the base of VT3, and two other DC generators will be carried to the VT p I + E bases of VT1 and VT2 from the gates, these trann F p sistors are loading. In modified circuit emitters and bases of F transistors – DC generators – are bypassed. It V T 3 means that all these transistors can be exchanged V T1 V T2 for one multicollector transistor VT. n In this stage of modification we will explain p A B the sense of word "injection" in the name of I2L. n The gate is connected with power supply just through transistor VT – DC generator: all gate cirV T4 cuit is fed by charge carriers, injected through emitter of VT . Therefore this emitter is called as "injector," and logic is called as integrated injection logic. VT2 VT1 A VT B I VT2 VT1 A 40 F B F I2L has not standard value of power supply + E voltage. It is determined by two summands: voltage drop on saturated VT (0.2 V), and voltage drop on saturated BE junction (0.7 V) of VT1 or VT2 or VT3 VT3. Usually E (1 1.5) V. Now we will take the last step in modification of circuit. When all logic transistors of the gate are designed as multicollector transistors, one pair of collectors of the gate transistors is loaded by only one transistor of loading gate. In this case input capacitances of loading gates are not summed up, and operation speed of the gate increases. +E Not standard circuit of I2L gate is realized by not standard topology of integrated circuit. Two main ideas are realized in the topology VT3 2 of I L gate: – there is no isolated area for any transistor of the gate (unprecedented case in BJT integrated circuits); – the principle of matching of areas of different transistors is applied. 4. Logic Gates Only one area for transistor VT – DC generator VT3 p – was formed: it is p-injector. n-base of VT is matched p n n n n with n-emitters of VT1, VT2, ... , and both of them are + + + + + + + + matched with n-epitaxial layer. p-collectors of VT are F + + + + matched with p-bases of VT1, VT2, ... . n The merits of I2L: VT2 1. Very small power consumption, because: a) very small voltage (1 V) of power supply; b) small currents are divided some times among A VT1 A I, +E A B the collectors of multicollector transistors; a A A c) there is no resistors that dissipate power. 2. Very low level of logic 0, because: n n n n p p a) n+ collectors of logic transistors have very n + + + + + + + +n small resistances; + + + ++ b+ b) all currents are small. 3. Large scale integration, and small price, because: a) there are no isolated areas for transistors; b) the areas of terminals of different transistors are matched. Disadvantages of I2L: 1. Small logic swing and bad interference immunity because of very small voltage of power supply. 2. Medium operation speed because all capacitances are charged and discharged by small currents; the situation is not as bad as it could be, because: a) there is no resistors and therefore all time constants in the circuit are small; b) input capacitances of loading gates are not summed up; c) small areas of components guarantee small spurious capacitances. Application of I2L has sense in the case of large circuits of complicated logic devices only, when large scale integration is desirable. 4.2. Field Effect Transistors Logic Gates D In this chapter the MOS and CMOS switches and various MOS and G CMOS logic gates are investigated. Logic gates are made entirely from enhancement-mode MOSFETs PM OS with n-channel (NMOS) or p-channel (PMOS). JFETs in the logic circuits are not used. 4.2.1. MOSFET Switches n p S n D p n G MOSFET switch is made from logic or active transistor, controlled by N M OS S signals in switch input, and transistor-load. Resistors are not used in MOS logic circuits. Transistor-load can be passive or controlled by logic signals. p 41 4. Logic Gates Switches with passive load We will analyze three different circuits of switches with passive load. In one of them gate of transistor-load is connected with power supply voltage +E. Both transistors VT1 and VT2 are formed in the same chip with the same + E VT1 processes, so they have the same threshold voltage. Let low logic level in input of switch makes OFF active switch transistor VT2. What is with transistor-load? In the circuits with enhanVT2 UOUT cement-mode MOSFETs power supply voltage E (3 – 4) Uthr . Let UIN VT1 is ON. It means that all power supply voltage E drops on the very large resistance of closed VT2, and UOUT E. UOUT USVT1 E. But UGVT1 E, and control voltage of VT1 USG 0. It disagrees with presumption that VT1 is ON. Let VT1 is OFF. It U OUT means that power supply voltage E is divided E between two very large resistances of closed VT1 and closed VT2: UOUT USVT1 E/2. U 1 E– U thr UGVT1 E, and control voltage of VT1 USG rchanV T1 rchanV T2 E/2 (1.5 – 2) Uthr . It disagrees with presumpE/2 tion that VT1 is OFF. There is only one way out of a situation: to say, that VT1 is slightly open with voltage drop on it that equals to threshold rchanV T1 voltage. Then UOUT E – Uthr (2 – 3) Uthr – U o E/10 10rchanV T2 U IN it is high level that can saturate transistor of 0 U thr E/2 U 1 E– U thr loading gate. Low level in switch input corresponds with high level in its output – the switch realizes inversion of input signal. Let high logic level is in input of switch and active switch transistor VT2 is ON. Let VT1 is ON so. It means that power supply voltage E is divided between two small and equal resistances of opened VT1 and opened VT2: UOUT USVT1 E/2. Control voltage of VT1 USG E/2 (1.5 – 2) Uthr . It agrees with presumption that VT1 is ON. The problem is such that output voltage E/2 is not a low level for loading gates. The problem can be solved when different topology of active transistor and transistor-load is applied and rchanVT2 10 rchanVT1 . Then UOUT E/10 and it is a normal level of logic 0. In another circuit of NMOP switch the gate of transistor-load is +EG E+ Uthr connected with power supply voltage that makes this transistor always +E VT1 ON. When UIN is low, VT2 is OFF and VT1 is ON. All voltage E drops on the large resistance of VT2, UOUT U1 E. The low level in output of switch will be proper, when the same condition as in the VT2 UOUT former switch will be performed: rchanVT2 10 rchanVT1 . Then UIN UOUT U0 E/10. Transfer characteristic of this switch differs from transfer characteristic of the former switch only in the value of a high level in switch output: U1 E. 42