* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Voltage Reference Circuits

Ground (electricity) wikipedia , lookup

Stepper motor wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Mercury-arc valve wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power inverter wikipedia , lookup

Thermal runaway wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Electrical ballast wikipedia , lookup

Three-phase electric power wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Power electronics wikipedia , lookup

Current source wikipedia , lookup

Schmitt trigger wikipedia , lookup

Power MOSFET wikipedia , lookup

Surge protector wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Voltage regulator wikipedia , lookup

Stray voltage wikipedia , lookup

Buck converter wikipedia , lookup

Opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Voltage optimisation wikipedia , lookup

Voltage Reference Circuits

2011/04/12

Ke-Horng Chen

Voltage Reference Circuits

Form a temperature-insensitivity reference

The required temperature dependence assumes one of

three forms:

Operate at low voltages

Are robust to process fluctuations

Exhibit low electrical current consumption

Can be integrated with standard CMOS technologies

Allow flexible voltage adjustment

PTAT: proportional to absolute temperature

Constant-GM behavior: the transconductance of certain

transistors remains constant

Temperature independent

Two design problems:

Supply-independent biasing

Definition of the temperature variation

2

Supply-Independent Biasing

If IREF doesn’t vary with VDD

I out

VDD

(W / L) 2

R1 1/ g m1 (W / L)1

ID2 and ID3 remain independent

The output current of this

of VDD

circuit is quite sensitive to VDD

How do we generate IREF?

The circuit must bias itself

IREF must be somewhat

derived from Iout

3

Simple Circuit to Establish SupplyIndependent Currents

M3 and M4 copy Iout, thereby defining Iout

I out KI REF

IREF is bootstrapped to Iout

Since each diode-connected device feeds from a current

source, Iout and IREF are relatively independent of VDD

4

Addition of RS to Define the Currents

Alternative implementation

eliminating body effect

Resistor RS decreases the current of M2

While the PMOS devices require that Iout=IREF because they have identical dimensions

VGS1 VGS 2 I D 2 RS

2 I out

VTH 1

nCOX (W / L) N

2 I out

VTH 2 I out RS (Assume VTH 1 VTH 2 )

nCOX K (W / L) N

Neglecting body effect, we have

2 I out

1

(1

) I out RS

nCOX (W / L) N

K

2

1

1 2

)

2 (1

nCOX (W / L) N RS

K

and I out 0 (degenerate bias)

I out

The current is independent of supply

voltage

Relatively long channels are used for all of

the transistors in the circuit (channel-length

modulation is negligible)

5

But still a function of process and

temperature

Break the Feedback Loop between the

Gate of two PMOS

DC gain

z1

g m 2 A / g m 2 B ( sCP RB 1)

Vo

Vi ( sC1 / g m 3 1) ( sC2 / g m 2 B 1) ( sCP RB g m 2 A RB 1)

p2

p3

M3A

M2A

p1

M3B

M2B

Zero when

Z = infinite

6

Magnitude Plot & Stability

Typically C1<<Cp C2<<Cp

Zero is always lower than the pole

gm2A is too large, z1 and p1 move further apart

When [Vo/Vi]>0dB, the phase lag introduced by p2 and p3 can

cause instability

7

Compensation

To ensure stability, a capacitor can be added to increase either

C1 or C2

Thereby, creating a pole dominant over p1

For example, to ensure stability with C2, must satisfy the

inequality

DC gain

z1

g m 2 A / g m 2 B ( sCP RB 1)

Vo

1

Vi ( sC1 / g m 3 1) ( sC2 / g m 2 B 1) ( sCP RB g m 2 A RB 1)

p2

p3

p1

g m 2 A RB

C2

CP CP

g m 2 A RB 1

8

Alternative Implementation Eliminating

Body Effect

1

gm4

1

gm4

g

g

VF

( m 3 )(

1

) m3

1

1

g m1

VT

g m1 R

Rs

s

gm2

gm2

The loop gain is positive and stable if and

only if loop gain <1

g m1

1

gm4

1

g m1 Rs

g m1

gm2

1

Rs

VF

VT

g m3

1 where g m 3 g m 4

g m1 R 1

s

gm2

gm2

g m 2 g m1

g m1 g m 2

K 1

g m1

9

Alternative implementation eliminating

body effect (cont’d)

g

g g

VF

1

1

( m 2 )( g m 3 (

Rs )) m 2 m 3 (

Rs ) 1

VT

gm4

g m1

g m 4 g m1

The loop gain is positive and stable if and

only if loop gain <1

g m1

VT

gm2

VF

g m 2 g m3 1

(

Rs ) 1 where g m 3 g m 4

g m 4 g m1

1

Rs

gm2

g m1

gm2

Rs

g m1 g m 2

g m1 g m 2

K 1

g m1

10

A Sub-1 V, 10 ppm/°C, Nanopower

Voltage Reference Generator

An extreme low power voltage reference generator operating

with a supply voltage ranging from 0.9 to 4 V has been

implemented in AMS 0.35 μm CMOS process

A temperature coefficient of 10 ppm/°C is achieved by means of

a perfect suppression of the temperature dependence of the

mobility

the compensation of the channel length modulation effect on the

temperature coefficient

the absence of the body effect

The power supply rejection ratios without any filtering capacitor

at 100 Hz and 10 MHz are lower than -53 and -42 dB,

respectively

The maximum supply current measured at the maximum supply

voltage and at 80 °C is 70 nA

The occupied chip area is 0.045 mm2

Giuseppe De Vita, Giuseppe Iannaccone Dipartimento di Ingegneria dell’Informazione: Elettronica, Informatica,

Telecomunicazioni Università di Pisa, Via Caruso 16, I-56122 Pisa, Italy {giuseppe.devita, g.iannaccone}@iet.unipi.it

低功率混合晶片設計實驗室

LAB 802

11

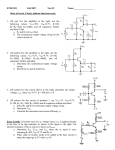

Voltage Reference Circuit

A circuit formed by

transistors numbered

from M1 to M8

generates a current I0

as independent as

possible of the supply

voltage VDD

Such current is then

injected into the diodeconnected NMOS

transistor M10

Start-up

I1

I1

sub

sat

sub

I0

sat

I0

sat

The temperature dependence of I0 is compensated by the

temperature dependence of the gate-source voltage of M10

generating a temperature compensated reference voltage VREF

低功率混合晶片設計實驗室

LAB 802

12

Current generator

The core of the current

generator circuit is

represented by

transistors M1-M4

M5 and M6 impose equal

current I1 in M1 and M3

M7 and M8 impose equal

current I0 in M2 and M4

Determine the value of

the current I0

Start-up

I1

I1

sub

sat

sub

I0

sat

I0

sat

Transistors M1 and M3 are 5V-NMOS transistors with a threshold

voltage of 0.7 V

all the other transistors are 3.3V-MOS transistors with a threshold

voltage of 0.45 V and -0.75 V for NMOS and PMOS, respectively

The two different threshold voltages allow us to

bias M1 and M3 in the subthreshold region

at the same time, to bias M2 and M4 in the saturation region

低功率混合晶片設計實驗室

LAB 802

13

Operation region

Such behavior is achieved by setting the gate-source voltages of M1, M2

and M3, M4 to a value between 0.45 V and 0.7 V

Cox W

2

ID

VGS Vth 1 VDS saturation

2 L

VGS Vth

VDS

2W

exp

I D VT

1 exp

subthreshold region

L

mVT

VT

Consider M1 and M3 in subthreshold with drain current I1 and M2 and M4

in saturation with a drain current I0

Then, by enforcing VGS1 = VGS2 and VGS3 = VGS4

we have

2I0

I1

VGS 1 ( sub) VGS 2 ( sat ) Vth1 mVT ln

V

th 2

2

CoxW2 / L2

/

V

W

L

T 1 1

2I0

I1

VGS 3 ( sub) VGS 4 ( sat ) Vth 3 mVT ln

V

th 4

2

CoxW4 / L4

/

V

W

L

T 3 3

低功率混合晶片設計實驗室

LAB 802

14

Operation region (cont’d)

Obviously, since the source terminals of all NMOS transistors are

grounded, the body effect plays no role and Vth1=Vth3 and Vth2=Vth4

W4 / L4

2 2

2 W3 / L3

m

V

ln

where

N

T

2

W

/

L

W2 / L2

2 N 1

1 1

In order to generate a temperature compensated reference

voltage, M10 operates in the saturation region

I0

CoxW4 / L4

VREF Vth10

W / L

mVT W4 / L4

ln 3 3

N 1 W10 / L10 W1 / L1

Generate the current I0 without using any resistance, that are

conversely used in similar types of circuits

Particularly important in the case of an ultra-low-power voltage

reference generator

Because a very large resistance would be necessary to generate the

small required current I0 (some tens of nA)

Drastically reduce the area occupation on the chip

低功率混合晶片設計實驗室

LAB 802

15

Supply voltage dynamic range

The minimum supply

voltage is imposed by the

current generator circuit

Start-up

M5 operates in the

saturation region with

|VGS5|> Vth5 (Vth5 = 0.75 V)

sub

The VDS dependence of

the current in M1 can be

neglected

AMS 0.35μm CMOS process

I1

I1

M1 has a drain-source

voltage of at least 100

mV

VDS(MAX) of a MOSFET: 3.3 V

VREF VDS 9 MAX

VGS 5 VDS 1MIN

sat

sub

I0

sat

I0

sat

In the AMS 0.35 m CMOS process

VREF VDS 9 MAX VDD VGS 5 VDS 1MIN

4.0 V

低功率混合晶片設計實驗室

LAB 802

0.9 V

16

Temperature compensation

The threshold voltage of an NMOS transistor decreases

linearly with the temperature: (As a first approximation)

Vth (T ) Vth (T0 ) K tn T T0

where K tn 0.33 mV / C is a BSIM3v3 coefficient

VREF

T

W / L

mVT W4 / L4

Vth10

ln 3 3

N 1 W10 / L10 W1 / L1

m kB

K tn

T

N 1 q

W4 / L4

W10 / L10

K tn

m k B W3 / L3

ln

N 1 q W1 / L1

W / L

W4 / L4

ln 3 3 0

W10 / L10 W1 / L1

independent of the temperature

dependence of the carrier mobility

a smaller temperature coefficient

compared to cases in which the

temperature dependence of the

mobility is compensated only at the

reference temperature [8]

[8] K.N. Leung, P.K.T. Mok, “A CMOS Voltage Reference Based on Weighted ΔVGS for CMOS LowDropout Linear Regulators,” IEEE Journal of Solid State Circuits, vol. 38, pp. 146-150, January 2003.

低功率混合晶片設計實驗室

LAB 802

17

Channel length

modulation effect

Subthreshold region:

Start-up

I0

if VDS >>VT, we can

neglect VDS

Considerλ≠0 for a MOS

in the saturation region

I1

I1

I0

sub

sat

sub

sat

sat

Assuming L4 of M4 is sufficiently large to ensure λVDS<<1 (first

order in λVDS)

W10 / L10 K tp

K tn

VREF

VDD Vth8 VREF 0 Vth10 2

N 1

W8 / L8

K tn

T

where K tp is the temperature coefficient for the threshold voltage of a PMOS

VREF 0 is the reference voltage for 0

低功率混合晶片設計實驗室

LAB 802

18

Channel length modulation effect (cont’d)

W10 / L10 K tp

K tn

VREF

VDD Vth8 VREF 0 Vth10 2

0

T

N 1

W8 / L8

K tn

Choose the dimension of M8 so that for a supply voltage in the

middle of the supply voltage range (VDD = 2.45 V)

K tp

VDD Vth8

W10 / L10

2 K tn 2 VREF 0 Vth10

W8 / L8

> 2.45 VDD V

The temperature coefficient is negative

< 2.45 VDD V

The temperature coefficient is positive

低功率混合晶片設計實驗室

LAB 802

19

Experiments:

a) Output Voltage vs. Supply voltage at room temperature, b)

PSRR at room temperature and for a supply voltage of 2 V

A mean reference voltage

of about 670 mV

with a variation of 5.67

mV at room temperature,

when the supply voltage

varies from 0.9 V to 4 V

-42 dB

-53 dB

At the smallest supply voltage

PSRR, without any filtering capacitor, is -47 dB at 100 Hz and -40

dB at 10 MHz

At larger supply voltage

PSRR decreases to -53 dB at 100 Hz and to -42 dB at 10 MHz

低功率混合晶片設計實驗室

LAB 802

20

Measured output voltage vs. temperature

for 4 values of the supply voltage

The output voltage dependence on temperature for different

values of the supply voltage

> 2.45 VDD V

< 2.45 VDD V

低功率混合晶片設計實驗室

LAB 802

The temperature

coefficient is negative

The temperature

coefficient is positive

21

Comparison with voltage reference

generators available in the literature

低功率混合晶片設計實驗室

LAB 802

22

Estimate the Change in Iout

for a Small Change ΔVDD in

the Supply Voltage

Calculate the gain from VDD to Iout

VDD VX

V

I out R3 g m 4 X for Node X

ro 4

R1

VSG4=-IoutR3

VDD VX

ro4

IoutR3gm4

VX

R1

If the equivalent transconductance of M2 and RS by Gm 2 I out / VX

I out

1

1

[

R3 g m 4 ]1

VDD ro 4 Gm 2 (ro 4 // R1 )

g m 2 ro 2

G

m2

RS ro 2 ( g m 2 g mb 2 ) RS ro 2

R1 ro1 //(1/ g m1 )

R3 ro 3 //(1/ g m 3 )

The sensitivity vanishes if ro4=∞

Owing to various capacitive paths, the supply sensitivity of the circuit

typically rises at high frequencies

The supply voltage of the core is often derived from a locally-generated,

less sensitive voltage

23

Start-up Circuit

M5 provides a current path

from VDD through M3 and M1 to

ground upon start-up

M3,M1,M2 and M4 can’t remain

off

This technique is practical

only if VTH 1 VTH 5 | VTH 3 | VDD

And VGS 1 VTH 5 | VGS 3 | VDD : to

ensure M5 remains off after

start-up

The problem of start-up generally requires careful analysis

and simulation (dc sweep, transient simulation)

24

Temperature-Independent Reference

Two quantities having opposite temperature coefficients (TCs)

are added with proper weighting, the result displays a zero

1

V1

V

2 2 0

T

T

VREF 1V1 2V2

The characteristics of bipolar transistors have proven the most

reproducible and well-defined quantities that can provide

positive and negative TCs

Many parameters of MOS devices have been considered for the

task of reference generation

25

Negative-TC Voltage

The base-emitter voltage of bipolar transistor or

the forward of a pn-junction diode exhibits a

negative TC

For a bipolar device,

I C I S exp(VBE / VT ) ,where VT kT / q

I S kTni2 ,where μ denotes the mobility of minority

m

0T

, where m 3 / 2

ni2 T 3 exp Eg /(kT ) , ni is the intrinsic minority carrier

concentration of silicon, where Eg 1.12eV

Eg

4 m

exp

I S bT

kT

Where b is a proportionality factor

26

Negative-TC Voltage (cont’d)

Writing VBE=VTln(IC/IS)

Assume IC is held constant

VBE VT I C VT I S

ln

T

T

I S I S T

Eg

Eg Eg

I S

3 m

4 m

b(4 m)T exp

bT (exp

)( 2 )

kT

kT kT

T

Therefore,

•With VBE 750mV and

VT I S

V

(4 m) T 2 VT

I S T

T kT

Eg

T 300o K VBE / T 1.5mV / o K

VBE VT I C

VT Eg

ln (4 m) 2 VT

T

T

IS

T kT

VBE (4 m)VT

T

Eg

q

VBE VG

k

(4 m)

T

q

VBE

T itself depends on the temperature

27

Positive-TC Voltage

VBE VBE1 VBE 2

VT ln

nI 0

I

VT ln 0

I S1

IS 2

VT ln n

VBE k

ln n

The VBE difference exhibits a positive TC

T

q

This TC is independent of the temperature or behavior of the

collector currents

28

Generation of PTAT voltage

VBE VT ln

nI 0

I

VT ln 0

IS

mI S

VT ln(mn)

The temperature coefficient is therefore equal to (k/q)ln(mn)

29

Bandgap Reference

With negative- and positive- TC voltage , we develop a zero

temperature coefficient ,we write VREF 1VBE 2 (VT ln n)

VT ln n is the difference between the base-emitter voltages of

the two bipolar transistors operating at different current

densities

Since at room temperature,

VBE / T 1.5mV / K whereas VT / T 0.087 mV / K

we may set 1 1 and choose 2 ln n such that

( 2 ln n)(0.087 mV / K ) 1.5mV / K

That is ( 2 ln n) 17.2

Indicate that for zero TC:

VREF VBE 17.2VT 1.25V

30

Conceptual Generation of TemperatureIndependent Voltage

The circuit requires two modifications to become practical

A mechanism must be added to

guarantee Vo1=Vo2

Vo 2 VBE 2 VT ln n , Vo2 can serve as a

temperature-independent reference if

lnn=17.2 (n is large)

RI=VTlnn must be scaled up by a

reasonable factor

VBE1 RI VBE 2

RI VBE1 VBE 2

VT ln

I

I

VT ln

IS

nI S

IS

nIS

VT ln n

31

Actual Generation of TemperatureIndependent Voltage

Vout

VT ln n

( R3 R2 )

VBE 2

R3

R

VBE 2 VT ln n 1 2

R3

VT ln n

T

R3

PATA current

For a zero TC, we must have ln n(1 R2 / R3 ) 17.2

For example, we may choose n 31 and R2 / R3 4

Note these results do not depend on the TC of the resistors

32

Collector Current Variation

VBE / T 1.5mV / K was derived for a

constant current

What happens to the temperature coefficient

of VBE if the collector currents are PTAT?

I C1 I C 2 (VT ln n) / R3

I C / T (VT ln n) /( R3T ) I C / T

VBE VT ln I C / I S

VBE VT I C

1 I C 1 I S

ln VT (

)

T

T

IS

I C T I S T

VBE VT I C VT VT I S

ln

T

T

I S T I S T

VBE VBE (3 m)VT Eg / q

T

T

The TC is slightly less negative than

VBE / T 1.5mV / o K

33

Compatibility with CMOS Technology

In n-well processes, a pnp transistor can

be formed as depicted in the right figure

A p+ region ( the same as the S/D region

of PFETs) inside an n-well serves as the

emitter

The n-well acts as the base

The p-type substrate acts as the collector and it is inevitably

connected to the most negative supply (usually ground)

34

Op Amp Offset and Output Impedance

Assume I C1 I C 2

VBE1 VOS VBE 2 R3 I C 2

IC1

IC2

Vout VBE 2 ( R3 R2 ) I C 2

VBE1 VBE 2 VOS

( R3 R2 )

R3

R

VBE 2 (VT ln n VOS )(1 2 )

R3

Vout VBE 2

Owing to asymmetries, op amps suffer from input “offsets,” the output

voltage of the op amp is not zero if the input is set zero

VOS varies with temperature, raising the temperature coefficient of the

output voltage

35

Lower the Effect of VOS

The op amp incorporates large devices in a carefully chosen

topology so as to minimize the offset

The collector currents of Q1 and Q2 can be ratioed by a

factor of m such that VBE VT ln(mn)

Each branch may use two pn junctions in series to double VBE

R1 and R2 are ratioed by a factor of m,

producing I1 mI 2

mI

Neglect base current and assuming A1 is large

We can write VBE1 VBE 2 VOS VBE 3 VBE 4 R3 I 2

Vout

Vout VBE 3 VBE 4 ( R3 R2 ) I 2

2V ln(mn) VOS

VBE 3 VBE 4 ( R3 R2 ) T

R3

R

2VBE (1 2 )[2VT ln(mn) VOS ]

R3

I

2VBE

36

Conversion of Series Diodes to a

Topology with Grounded Collectors

We must ensure that the bias currents of both transistors have

the same behavior with temperature

37

Reference Generator Incorporating Two

Series Base-emitter Voltages

The op amp experiences no resistive loading,

but the mismatch and channel-length

modulation of the PMOS devices introduce

error at the output

The relatively low current gain of the

“native” pnp transistors

A means of base current cancellation may

be necessary since the base currents of Q2

and Q4 generate an error in the emitter

currents of Q1 and Q3

38

Feedback Polarity

The negative feedback factor

1/ g m 2 R3

N

1/ g m 2 R3 R2

1

g m1

The positive feedback factor

1/ g m1

P

1/ g m1 R1

To ensure an overall negative feedback P N

1

gm2

By a roughly a factor of two

Transient response remains well-behaved with large capacitive

loads

39

The Origin of the Bandgap Reference

V REF V BE VT ln n

V REF V BE VT

0

ln n

T

T

T

V BE (4 m )VT E g / q

V

T ln n

T

T

Eg

V REF

( 4 m )VT

q

The term “bandgap” is used here because as

T 0, VREF Eg / q VG

40

Supply Dependence and Start-up

The output voltage is relatively independent of the supply

voltage so long as the open-loop gain of the op amp is

sufficiently high

Start-up techniques should be added to ensure the op amp

turns on when the supply is applied

The supply rejection of the circuit typically degrades at high

frequencies owing to the op amp’s rejection properties, often

mandating “supply regulation”

41

Curvature Correction

The TC is typically zero at one temperature and positive or

negative at other temperature

The curvature arises from temperature variation of base-emitter

voltages, collector currents, and offset voltage

Many curvature correction techniques have been devised to

suppress the variation of VREF in the bipolar bandgap circuits but

they are seldom used in CMOS counterparts

This is because, due to large offsets and process variations,

samples of a bandgap reference display substantially different zeroTC temperatures, making it difficult to correct the curvature reliably

42

Generation of a PTAT Current

The bias currents of the bipolar transistors are in fact

proportional to absolute temperature

VT ln n kT ln n

I

T

R1

q R1

43

Generation of a PTAT Current Using a

Simple Amplifier

Assuming that M1-M2 and M3-M4 are

identical pairs,

For ID1=ID2, the circuit must ensure that

VX=VY

Thus I D1 I D 2 (VT ln n) / R1 , yielding the

same behavior for ID5

In practice, due to mismatches

between the transistors and

temperature coefficient of R1 the

variation of ID5 deviates from the ideal

equation

ID1

ID5

ID2

44

Generation of a Temperature-Independent

Voltage

The idea is to add a PTAT voltage (VPTAT) ID5R2 to a baseemitter voltage

The output therefore equals VREF VBE 3 ( R2 / R1 )VT ln n

where all PMOS transistors are assumed identical

IPTAT

VPTAT

45

Constant-Gm Biasing

The transconductance of MOSFETs plays a critical role in analog

circuit, determining such performance parameter as noise, smallsignal gain, and speed

It is often desirable to bias the transistors such that their

trnasconductance does not depend on the temperature, process,

or supply voltage

I out

2

1

1 2

(1

)

2

C

W

L

R

(

/

)

n ox

K

N

S

g m1 2nCox (W / L) N I D1

2

1

(1

)

RS

K

Does vary with

temperature

and process

A value independent of the supply and MOS device parameters

46

Constant-Gm Biasing by Means of a

Switched-Capacitor “Resistor”

1

The idea is to establish an average resistance equal to (CS f CK )

between the source of M2 and ground, where fck denotes the

clock frequency

Since the absolute value of capacitors is typically more tightly

controlled and since the TC of capacitors is much smaller than

that of resistor

This technique provides a higher reproducibility in the bias

current and transconductance

Capacitor CB is added to shunt the

high-frequency components

resulting from switching to ground

RS (CS fCK ) 1

47

Voltage-to-Current Conversion by

Means of a Switched Capacitor Resistor

RS (CS fCK ) 1

A switched capacitor resistor

48

Speed and Noise Issues

The voltage at node N is heavily

disturbed by the circuit fed by M5

For fast changes in VN, the op amp

can’t maintain VP constant and the bias

current of M5 and M6 experience large

transient changes

CB

Also, the duration of the transient at

node P may be quite long if the op amp

suffers from a slow response

The critical node P can be bypassed to ground by means of a

large capacitor (CB) so as to suppress the effect of external

disturbances

The stability of the op amp must not degrade with the addition of

the capacitor, requiring the op amp to be of one-stage nature

Since CB generally slows down the transient response of the op

amp, its value must be greater than the capacitance that

49

couples the disturbance to node P

Speed and Noise Issues (cont’d)

If CB is not large, then VP experiences a change and takes a

long time to return to its original value

In general, the response of the circuit must be analyzed by

applying a disturbance at the output and observing the

settling behavior

50

The Small-Signal Output Impedance of

the Bandgap Reference

g mpVX R1 A( s )

CB

g mpVX

A( s )

g mpVX (

1

R1 )

g mN

A0

(1 s / 0 )

Assuming M1 and M2 are identical, a different voltage at the input of

the op amp

VAB g mPVX

1

g mN

1

1

g mPVX (

R1 ) g mPVX R1

g mN

g mN

The current flowing through Rout is given by

IX

VX g mPVX R1 A( s )

Rout

51

The Small-Signal Output Impedance of

the Bandgap Reference (cont’d)

1

s

Rout

Rout

Rout

0

VX

A0

s

I X 1 g mP R1 A( s ) 1 g R

1 g mP R1 A0 1

mP 1

(1 g mP R1 A0 )0

1 s / 0

A zero at 0

A pole at (1 g mP R1 A0 )0

|Zout| is only 30% lower than the open-loop value

| Z out |

Rout

1 j (1 g mP R1 A0 ) Rout

1 g mP R1 A0

1 j

2

52

Circuit for Calculation of Noise in a V

V

g (R g

Reference Generator

n ,out

P

mp

1

1

mN

)

Taking into account only the inputreferred noise voltage of the op

amp, Vn,op

At node A, we can write

Vn ,out

Vn ,out

1

(Vn ,op Vn ,out )

1

R1 g 1 g mN

g

A

R

g

(

)

mP

0

1

mN

mN

1

1

1

(

) 1] Vn ,op

Vn ,out [

1

R1 g mN g mN g mP A0

Vn ,out [

1

R1 g mN 1

1] Vn ,op

Vn ,out

1

R1 g mN

Vn ,op Vn ,out

Vn ,out

1

R1 g mN

Since typically g mP A0

g mN

R11

| Vn ,out | Vn ,op suggests that the noise of the op amp directly appears at the

output

The addition of a large capacitor from the output to ground may not suppress

low-frequency 1/f noise components, a serious difficulty in low-noise

53

applications

Case Study:

Simplified of the Bandgap Circuit

The reference generator which is with

two series base-emitter voltage in

each branch can reduce the effect of

MOSFET mismatches

The PMOS current mirror

arrangement ensures equal collector

currents for Q1-Q4

Channel-length modulation of the MOS

devices still results in significant

supply dependence

54

Case Study

Addition of cascode devices to

improve supply rejection

Use of self-biased cascode to

eliminate Vb1 and Vb2

R2 and R3 sustain proper

voltages to allow all MOSFETs

to remain in saturation

55

Case Study:

Generation of a Floating Reference Voltage

I D10 2(VT ln n) / R1

VR 5 2(VT ln n)( R5 / R1 )

VR 4 VBE 4 ( R4 / R6 )

I D 9 VBE 4 / R6

Vout

R

R4

VBE 4 2 5 VT ln n

R6

R1

56

Regulation of the Supply Voltage of the Core

and Op Amp to Improve Supply Rejection

The design regulates the supply voltage of the core and the op

amp

The idea is to generate a local supply, VDDL

VDDL remains relatively independent of the global supply voltage

To minimize the dependence of VR1 upon the supply, this voltage is

established inside the core

RM is chosen such that VR1 is a bandgap reference

57

Case Study:

Overall Circuit of the Bandgap Generator

Operating from a 5-V supply

The reference generator produces a 2.00-V output while consuming

2.2 mW

The supply rejection is 94 dB at low frequencies, dropping to 58 dB

at 100 kHz

58

Sub-1-V Bandgap Without Requiring

Low Threshold Voltage Device

Low-voltage design of PTAT current generation

loop is limited by Vin,cm of the amplifier

NMOS input stage:

VDD

Vin ,cm (of OP) < VEB ( on )

M3

M2

M1

2VDS ( sat ) Vth ,n VEB ( on )

Vref

2*50mV Vth ,n 0.7V

VB

Vth ,n 0.6V

Problem of TC:

VBE:-2mV/K

Vth:greater than -2mV/K (about -1.4mV/K)

Circuit may not function properly

低功率混合晶片設計實驗室

LAB 802

R1

Q1

R2

Q3

Q2

59

Sub-1-V Bandgap (cont’d)

VDD

PMOS input stage

VDD-2VSD(sat)-|Vth,p| > VEB(on)

1V-2*50mV-|Vth,p| > 0.7V

|Vth,P| < 0.2V

M1

M2

M3

VDD

VB

Vref

+

PMOS input stage

-

R1

Q1

低功率混合晶片設計實驗室

LAB 802

R2

Q2

Q3

60

Sub-1-V Bandgap (cont’d)

OP enforces N1 and N2 to

have the same potential

R2A1=R2B1;R2A2=R2B2

Thus, VN3=VN4

IVBE

Vref

V

V ln( N )

I EB 2 T

R2

R1

VDD

I

I

I

VB

N3

R

R

Vref 3 VEB 2 VT ln( N ) 2

R2

R1

Minimum supply voltage

N4

R2B1

R2A1

+

IPTAT

N1

R2A2

R2 B 2

Vs (min) VEB 2

Vthp 2VSD ( sat )

R2 B1 R2 B 2

M3

M2

M1

Vref

-

N2

R1

R3

R2B2

1

N

Q1

Q2

which should be evaluated at

the lowest operating

temperature

低功率混合晶片設計實驗室

LAB 802

61

Complete Schematic

Bandgap core

Startup

VSB bias

低功率混合晶片設計實驗室

LAB 802

Low voltage OP

62

Forward Biasing the VSB of PMOS

Transfer characteristic of the OP

VSB=0時的Vth

Vthp Vthp ,0

2 f VSB 2 f

Let VSB>0,|VGSP| reduced to |VGSP’|

Make a temperature-independent voltage across RSB

The voltage across RSB decreases slightly according to temperature

Set to about 0.3V at the lowest operating temperature

低功率混合晶片設計實驗室

LAB 802

63

DC Level-Shifting

A. Without dc level-shifting

B. With dc level-shifting

VDD

VB

MA05

+

Vin+

MA08

VSD,8=[Vin+ +|VGS,8|-VGS,10]

-

MA12

Vin+|VGS8|

Vin+|VGS8|

VSD,8=[Vin+ +|VGS,8|-VGS,10+VEB,16]

VGS,10-VEB,16

VGS,10

MA10

If Vth,n>|Vth,p|,it may make VSD,8<VSD(sat)

If Vth,n>|Vth,p|,it won’t make VSD,8<VSD(sat)

低功率混合晶片設計實驗室

LAB 802

64

Startup Circuit

When the circuit is off,VG,M1~VG,M3 are pulled high

Turn on MS3、MS4

The output of the inverter (MS1 and MS2) is low

MS3 makes the bandgap core on

MS4 makes the low-voltage amplifier on

Till the input of the inverter is low and output is high

VD,M2 increases

Amplifier forces VD,M1 to increase by pulling down VG,M1~VG,M3

Let (W/L)MS2<(W/L)MS1

Choose at Vs(max) and T(max) (ensure a complete cutoff of MS3 and MS4)

低功率混合晶片設計實驗室

LAB 802

65

Effect of Vos

Vref

VN 2 VN 1 VOS

I1

VR1

R1

I2

VEB 2

R2

Vref

VN 2 VOS

R2

Vf 1

R2 A 2

R1

Vf 2 Vf 1

R2

VOS

V

N

ln(

)

T

V

R2 A 2

R3 EB 2

R1

R2

Minimize the effect

Increase N

Reduce R2/R1

R1

R2

VOS

R2 A 2

R2

VOS

V ln( N ) R2 A 2

T

R1

R1

R

R

R

3 VEB 2 2 VT ln( N ) 2 VOS

R1

R2 A 2

R2

larger

低功率混合晶片設計實驗室

LAB 802

66

BG Based on Subthreshold MOSFETs

VGS v.s. T in subthreshold MOSFETs

Assuming channel length is sufficiently long, two equivalent

representations for ID are:

I D S U T 2

I D S U T 2

And

q si N CH

e

4B

S 2 B

q si N CH

e

4B

VT

VGS VTH VOFF

nVT

S (T ) S (T0 )

T 3kT T Eg (T ) Eg (T0 ) T

ln

T0

q

T

q

q T0

0

Surface potential:

Bulk Fermi potential: B (T ) B (T0 )

S (T ) 2B (T ) S (T0 ) 2B (T0 )

VGS VTH VOFF

S 2B

n

T 3kT T Eg (T ) Eg (T0 ) T

ln

T0 2q T0

2q

2q T0

T

T0

低功率混合晶片設計實驗室

LAB 802

67

The negative temperature coefficient of VGS

T

VGS (T ) VTH (T ) VOFF n S T0 2B T0

T

0

VGS (T0 ) VTH (T0 ) VOFF n S T0 2B T0 when T T0

We can get

Assuming n(T) has small variation

n(T )

T

VGS (T ) VTH (T ) VOFF

VGS (T0 ) VTH (T0 ) VOFF

n(T0 )

T0

T

VTH (T ) VTH (T0 ) KT 1

T0

The final result is

T

VGS (T ) VGS (T0 ) K G 1

T0

where

K G KT VGS (T0 ) VTH (T0 ) VOFF

Approximately -330mV

Approximately -57.2mV

is negative

低功率混合晶片設計實驗室

LAB 802

68

Subthreshold Current Equation

VDD

If MOS work in weak inversion region

M2

M4

I D SI D0e

M3

R

n is slope factor

S is aspect ratio

ID0 is characteristic current

I D SI D 0 e

M1

VGS

nVT

VGS

nVT

I D1 S1 I D 0 e

VGS 1

nVT

I D 3 S3 I D 0e

低功率混合晶片設計實驗室

LAB 802

VGS1 VGS 3 VT ln

S 2 S3

S1S4

VGS 3

nVT

69

Generate VR Voltage Reference

VDD

M3

M4

M5

M6

IR1S5/S4

M 11

M 10

IR1S6/S4

IB

VR

M9

R4

M2

M7

M8

IR4

M1

CC1

I R1

CL

CC 2

IR1

R2

R1

VR3

VR3/R3

VGS 1 ( I B )

R1

V

S

VR I R 4 R4 VR 3 R 3 I R1 6 R4 VR 3

S4

R3

R3

VR 3 I R1

S5

S R

SS

R2 VGS 7 VGS 8 5 2 VGS 1 ( I B ) VT ln 5 8

S4

S 4 R1

S6 S7

低功率混合晶片設計實驗室

LAB 802

70

Determine the Parameters to

Generate the Reference Voltage

T

VGS (T ) VGS (T0 ) K G 1

T0

VR VGS1 ( I B ) VT

R4 R2 S5 R4 S6

R4 S5 S8

where 1

, 1 ln

R

R

S

R

S

R

S

S

3 1

4

1

4

3

4 7

Nullifying the TC

1 VR

TCVR

0

VR T

If

VT (T0 )

then TCVR 0

KG

低功率混合晶片設計實驗室

LAB 802

71

Current IB Generation & Result

VDD

M P6

M P3

M P5

M P4

IB

M P7

I P4

M P1

M P2

CP

RP

SP5

S P 5 VT S P 2 S P 4

ln

IB

IP4

SP4

S P 4 RP S P1 S P 3

低功率混合晶片設計實驗室

LAB 802

295.3+/- 10.8mV

119+/- 35.7ppm/K

3.6uA

72

A Sub-1 V, 10 ppm/°C, Nanopower

Voltage Reference Generator

An extreme low power voltage reference generator operating

with a supply voltage ranging from 0.9 to 4 V has been

implemented in AMS 0.35 μm CMOS process

A temperature coefficient of 10 ppm/°C is achieved by means of

A perfect suppression of the temperature dependence of the

mobility

The compensation of the channel length modulation effect on the

temperature coefficient

The absence of the body effect

The power supply rejection ratios without any filtering capacitor

at 100 Hz and 10 MHz are lower than -53 and -42 dB, respectively

The maximum supply current measured at the maximum supply

voltage and at 80 °C is 70 nA

The occupied chip area is 0.045 mm2

Giuseppe De Vita, Giuseppe Iannaccone Dipartimento di Ingegneria dell’Informazione: Elettronica, Informatica,

Telecomunicazioni Università di Pisa, Via Caruso 16, I-56122 Pisa, Italy {giuseppe.devita, g.iannaccone}@iet.unipi.it

低功率混合晶片設計實驗室

LAB 802

73

Voltage Reference Circuit

A circuit formed by

transistors numbered

from M1 to M8 generates

a current I0 as

independent as possible

of the supply voltage

VDD

Such current is then

injected into the diodeconnected NMOS

transistor M10

Start-up

I1

I1

sub

sat

sub

I0

sat

I0

sat

The temperature dependence of I0 is compensated by the

temperature dependence of the gate-source voltage of M10

generating a temperature compensated reference voltage VREF

低功率混合晶片設計實驗室

LAB 802

74

Current generator

The core of the current

generator circuit is

represented by

transistors M1-M4

M5 and M6 impose equal

current I1 in M1 and M3

M7 and M8 impose equal

current I0 in M2 and M4

Determine the value of

the current I0

Start-up

I1

I1

sub

sat

sub

I0

sat

I0

sat

Transistors M1 and M3 are 5V-NMOS transistors with a threshold

voltage of 0.7 V

all the other transistors are 3.3V-MOS transistors with a threshold

voltage of 0.45 V and -0.75 V for NMOS and PMOS, respectively

The two different threshold voltages allow us to

bias M1 and M3 in the subthreshold region

at the same time, to bias M2 and M4 in the saturation region

低功率混合晶片設計實驗室

LAB 802

75

Operation region

Such behavior is achieved by setting the gate-source voltages of M1, M2

and M3, M4 to a value between 0.45 V and 0.7 V

Cox W

2

ID

VGS Vth 1 VDS saturation

2 L

VGS Vth

VDS

2W

exp

I D VT

1 exp

subthreshold region

L

mVT

VT

Consider M1 and M3 in subthreshold with drain current I1 and M2 and M4

in saturation with a drain current I0

Then, by enforcing VGS1 = VGS2 and VGS3 = VGS4

we have

2I0

I1

V

VGS 1 ( sub) VGS 2 ( sat ) Vth1 mVT ln

th 2

2

/

CoxW2 / L2

V

W

L

T 1 1

2I0

I1

V

VGS 3 ( sub) VGS 4 ( sat ) Vth 3 mVT ln

th 4

2

/

V

W

L

CoxW4 / L4

T 3 3

低功率混合晶片設計實驗室

LAB 802

76

Operation region (cont’d)

Obviously, since the source terminals of all NMOS transistors are

grounded, the body effect plays no role and Vth1=Vth3 and Vth2=Vth4

W4 / L4

2 2

2 W3 / L3

m

V

ln

where

N

T

2

W

/

L

W2 / L2

2 N 1

1 1

In order to generate a temperature compensated reference

voltage, M10 operates in the saturation region

I0

CoxW4 / L4

VREF Vth10

W / L

mVT W4 / L4

ln 3 3

N 1 W10 / L10 W1 / L1

Generate the current I0 without using any resistance, that are

conversely used in similar types of circuits

Particularly important in the case of an ultra-low-power voltage

reference generator

Because a very large resistance would be necessary to generate the

small required current I0 (some tens of nA)

Drastically reduce the area occupation on the chip

低功率混合晶片設計實驗室

LAB 802

77

Supply voltage dynamic range

The minimum supply

voltage is imposed by the

current generator circuit

Start-up

I1

M5 operates in the

saturation region with

|VGS5|> Vth5 (Vth5 = -0.75 V)

I1

M1 has a drain-source

voltage of at least 100 mV

sub

The VDS dependence of

the current in M1 can be

neglected

sat

sub

I0

sat

I0

sat

In the AMS 0.35 m CMOS process

VREF VDS 9 MAX VDD VGS 5 VDS 1MIN

AMS 0.35μm CMOS process

VREF VDS 9 MAX

VGS 5 VDS 1MIN

VDS(MAX) of a MOSFET: 3.3 V

4.0 V

低功率混合晶片設計實驗室

LAB 802

0.9 V

78

Temperature compensation

The threshold voltage of an NMOS transistor decreases

linearly with the temperature: (As a first approximation)

Vth (T ) Vth (T0 ) K tn T T0

where K tn 0.33 mV / C is a BSIM3v3 coefficient

VREF

T

W / L

mVT W4 / L4

ln 3 3

Vth10

N 1 W10 / L10 W1 / L1

m kB

K tn

N 1 q

T

W4 / L4

W10 / L10

K tn

m k B W3 / L3

ln

N 1 q W1 / L1

W / L

W4 / L4

ln 3 3 0

W10 / L10 W1 / L1

independent of the temperature

dependence of the carrier mobility

a smaller temperature coefficient

compared to cases in which the

temperature dependence of the

mobility is compensated only at the

reference temperature [8]

[8] K.N. Leung, P.K.T. Mok, “A CMOS Voltage Reference Based on Weighted ΔVGS for CMOS LowDropout Linear Regulators,” IEEE Journal of Solid State Circuits, vol. 38, pp. 146-150, January 2003.

低功率混合晶片設計實驗室

LAB 802

79

Channel length

modulation effect

Subthreshold region:

Start-up

I0

if VDS >>VT, we can

neglect VDS

Considerλ≠0 for a MOS

in the saturation region

I1

I1

I0

sub

sat

sub

sat

sat

Assuming L4 of M4 is sufficiently large to ensure λVDS<<1 (first

order in λVDS)

W10 / L10 K tp

K tn

VREF

VDD Vth8 VREF 0 Vth10 2

T

N 1

W8 / L8

K tn

where K tp is the temperature coefficient for the threshold voltage of a PMOS

VREF 0 is the reference voltage for 0

低功率混合晶片設計實驗室

LAB 802

80

Channel length modulation effect (cont’d)

W10 / L10 K tp

K tn

VREF

VDD Vth8 VREF 0 Vth10 2

0

T

N 1

W8 / L8

K tn

Choose the dimension of M8 so that for a supply voltage in the

middle of the supply voltage range (VDD = 2.45 V)

K tp

VDD Vth8

W10 / L10

2 K tn 2 VREF 0 Vth10

W8 / L8

> 2.45 VDD V

The temperature coefficient is negative

< 2.45 VDD V

The temperature coefficient is positive

低功率混合晶片設計實驗室

LAB 802

81

Experiments:

a) Output Voltage vs. Supply voltage at room temperature, b)

PSRR at room temperature and for a supply voltage of 2 V

A mean reference voltage

of about 670 mV

with a variation of 5.67 mV

at room temperature,

when the supply voltage

varies from 0.9 V to 4 V

-42 dB

-53 dB

At the smallest supply voltage

PSRR, without any filtering capacitor, is -47 dB at 100 Hz and -40

dB at 10 MHz

At larger supply voltage

PSRR decreases to -53 dB at 100 Hz and to -42 dB at 10 MHz

低功率混合晶片設計實驗室

LAB 802

82

Measured output voltage vs. temperature

for 4 values of the supply voltage

The output voltage dependence on temperature for different

values of the supply voltage

> 2.45 VDD V

< 2.45 VDD V

低功率混合晶片設計實驗室

LAB 802

The temperature

coefficient is negative

The temperature

coefficient is positive

83

Comparison with voltage reference

generators available in the literature

低功率混合晶片設計實驗室

LAB 802

84