* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download A SiGe PA With Dual Dynamic Bias Control and Handset Applications

Dynamic range compression wikipedia , lookup

History of electric power transmission wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Control system wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Electric power system wikipedia , lookup

Power inverter wikipedia , lookup

Electrification wikipedia , lookup

Three-phase electric power wikipedia , lookup

Wireless power transfer wikipedia , lookup

Buck converter wikipedia , lookup

Mains electricity wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Power engineering wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Power over Ethernet wikipedia , lookup

Alternating current wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

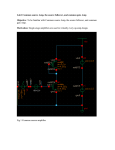

1210 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 5, MAY 2006 A SiGe PA With Dual Dynamic Bias Control and Memoryless Digital Predistortion for WCDMA Handset Applications Junxiong Deng, Member, IEEE, Prasad S. Gudem, Member, IEEE, Lawrence E. Larson, Fellow, IEEE, Donald F. Kimball, Member, IEEE, and Peter M. Asbeck, Fellow, IEEE Abstract—This paper demonstrates a two-stage 1.95-GHz WCDMA handset RFIC power amplifier (PA) implemented in a 0.25- m SiGe BiCMOS process. With an integrated dual dynamic bias control of the collector current and collector voltage, the average power efficiency of the two-stage PA is improved from 1.9% to 5.0%. The measured power gain is 18.5 dB. The gain variation with dynamic biasing is less than 1.8 dB. An off-chip memoryless digital predistortion linearizer is also adopted, satisfying the 3GPP wideband code division multiple access (WCDMA) linearity specification by a 10 dB improvement of adjacent channel power ratio (ACPR) at 26 dBm average channel output power. TABLE I 3GPP WCDMA CLASS 3 HANDSET POWER AMPLIFIER SPECIFICATIONS [3] + Index Terms—ACPR, average power efficiency, digital predistortion, dynamic bias control, linearity, memoryless systems, power amplifiers, Silicon Germanium, WCDMA. I. INTRODUCTION ILICON GERMANIUM (SiGe) is an attractive candidate for the development of handset power amplifiers (PAs), because of its competitive performance in efficiency, linearity, cost, and integration with BiCMOS technology [1], [2]. In wireless communications systems, PAs are key components that consume a significant portion of the DC power budget in the transmitter. For third-generation cellular systems, like wideband code division multiple access (WCDMA), more stringent linearity is required in terms of adjacent channel power ratio (ACPR) for higher spectral efficiency. Therefore, linearity and efficiency are the most critical parameters in the WCDMA PA design. In WCDMA systems [3], different power classes are required for the maximum transmit power at the output of the transmitter. Also, there are three operation bands (band I: 1920–1980 MHz; band II: 1850–1910 MHz; band III: 1710–1780 MHz) under different scenarios. Power Class 3 is the highest power class applicable to all three operation bands and the most common power class in practice, and hence the design objective in this S Manuscript received September 9, 2005; revised December 17, 2005. This work was supported by the UCSD Center for Wireless Communications and its Member Companies and by a UC Discovery Grant. J. Deng was with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA. He is now with Qualcomm Inc., San Diego, CA 92121 USA (e-mail: [email protected]). P. S. Gudem is with Qualcomm Inc., San Diego, CA 92121 USA. L. E. Larson, D. F. Kimball, and P. M. Asbeck are with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA. Digital Object Identifier 10.1109/JSSC.2006.872735 paper. Correspondingly, the design specifications for WCDMA Class 3 PAs are summarized in Table I. “Average” power efficiency, which is the ratio of the energy delivered to the antenna to the energy derived from the battery, is the key factor determining the talk time and battery life for portable wireless applications [4]. Linear PAs are typically operated in class AB mode and are often backed off from the maximum output power to achieve the desired linearity. Even though peak power efficiency may be high at high output powers, it drops quickly with the power back-off, resulting in a poor average power efficiency. To increase power efficiencies in the low-power region, different dynamic biasing techniques [5]–[8] have been developed. Altering the DC bias current in response to changing power requirements—also known as dynamic current biasing (DCB)—often results in significant amplifier gain variation. Although this gain-variation issue may be alleviated through the power control loop of the CDMA handset, it adds an extra burden to the algorithm. Furthermore, considering the power amplifier as a standalone block, this gain-variation can dramatically degrade the error vector magnitude (EVM), a system-level figure of merit for the accuracy of digitally modulated signals. Altering the DC bias collector voltage in response to changing power requirements—also known as dynamic voltage biasing (DVB)—typically requires the use of DC-DC converters with their associated large off-chip components and extra chip area and cost. Therefore, it is not attractive for small feature size handset PAs. A dual dynamic bias (DDB) control scheme [9] that does not require any additional off-chip components is proposed in this paper to provide an integrated solution with improved 0018-9200/$20.00 © 2006 IEEE DENG et al.: A SIGE PA WITH DUAL DYNAMIC BIAS CONTROL AND MEMORYLESS DIGITAL PREDISTORTION FOR WCDMA HANDSET APPLICATIONS 1211 Fig. 2. BJT current versus voltage, demonstrating different dynamic biasing strategies (DC/VB: dynamic current/voltage biasing). Fig. 1. DC current consumption of a two-stage class AB PA with fixed bias and a representative CDMA probability distribution function (PDF) [15]. average power efficiency and near-constant power gain for WCDMA Class 3 handset power amplifiers. In addition, an off-chip memoryless digital predistortion (DP) [10]–[14] based on the measured AM-AM and AM-PM characteristics is also employed to substantially improve the linearity of the PA. The resulting performance meets the WCDMA linearity specifications with significantly improved efficiency. The result is a low-cost WCDMA power amplifier. This paper is organized as follows. In Section II, we propose the dual dynamic bias technique to enhance the average power efficiency of a prototype two-stage power amplifier, and design considerations will be illustrated in detail. In Section III, we introduce memoryless digital predistortion as the linearization technique for the power amplifier. Predistortion algorithms and implementation details are also presented. In Section IV, the validity of the dual dynamic bias and digital predistortion is verified with experimental results. Conclusions are given in Section V. II. DUAL DYNAMIC BIAS CONTROL FOR EFFICIENCY ENHANCEMENT To improve the average power efficiency, it is necessary to reduce the dc current when the PA delivers a low output power. Fig. 1 shows the DC current consumption of a two-stage class AB power amplifier and a representative CDMA probability distribution function (PDF) as a function of output power [15]. At low output powers, the power amplifier is operated at a fixed bias current, and therefore, the efficiency is degraded; more than 90% of the output power occurs between 15 dBm and 15 dBm, where the efficiency is low. The average power efficiency is defined as (1) is the output power, the probability of where and the efficiency at output power output power . For example, using the PDF of Fig. 1, the average power efficiency of a Class AB amplifier is very low—below 2%. One of the main design objectives in this work is to achieve an average power efficiency far better than 2%. Fig. 3. Simplified schematic of a dynamic current bias. A. Principle of Dual Dynamic Biasing As shown in Fig. 2, we propose an integrated DDB control that reduces both the DC bias current and voltage without the use of external DC-DC converters. The DDB adopts a one-step approach with current re-use in the “low-power” group to reduce the DC voltage across the transistors. The dual dynamic biasing control includes dynamic current biasing (DCB) and dynamic voltage biasing (DVB). DCB is achieved by varying the bias current in response to the output power requirements. As shown in Fig. 3, there are two groups of SiGe HBT transistors: a high-power group (of 100 devices) and a low-power group (of 20 devices). The high-power group is biased at a current of 110 mA, whereas the low-power group is biased at 22 mA. The switching between different power groups is controlled by low-loss NFET switches on the bases of the HBT transistors. When the PA enters the low-power region, the high-power group is switched off and the low-power group is switched on. Therefore, the total bias current is reduced. On the other hand, DVB is realized by reusing the bias current. As shown in Fig. 4, the high-power group is the same as that in Fig. 3. The low-power group has two sub-groups and each sub-group has 20 devices. In the high-power group, each ; whereas transistor is connected in parallel and biased at in the low-power group, two sub-groups are series-connected to reuse the common bias current. Each transistor in the sub-group , and hence the DC bias voltage is lowered. is biased at Combining DCB and DVB, the DC power consumption of the power amplifier is significantly reduced. The DDB technique can be expanded to more than the one power control step used here. Several factors influence the op- 1212 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 5, MAY 2006 • A constant collector current density is essential for achieving constant gain [16]. • The connection between two power groups adds parasitics to each individual group, which degrades the overall gain. However, this connection decreases the difference between the gains in the two power modes since the input impedance of the output stage changes little between high-power and low-power operation. from the output of the • The routing line inductance low-power group to that of the high-power group is optimized to boost the gain in the low-power mode, by partially resonating the output capacitance of the high-power group. Since the output impedance of the low-power device is higher than that of the high-power device, the parasitic capacitance at the output has a larger degrading effect on the low-power gain. By partially resonating the parasitic capacitance in low-power operation, the gain difference between the two power modes is further reduced. Fig. 4. Simplified schematic of a dynamic voltage bias. Fig. 5. Comparison of average power efficiencies versus the number of power control steps for a SiGe power amplifier. timum number of power control steps, including the added complexity and parasitics associated with additional steps, the expected gain variation, and the reduced power consumption at the lowest output power levels. For example, based on the simulation results for a SiGe PA shown in Fig. 5, a single output stage with a two-step DDB achieves better average power efficiency (8.9%) than its one-step counterpart (7.7%); however, the corresponding circuit complexity increases dramatically and the achievable power gain also drops due to the added parasitics. More steps result in further diminishing returns, so the one-step topology was finally adopted in our prototype PA. B. Gain Variation With Power Control The gain of the PA should remain roughly constant as it switches from low-power to high-power operation.1 The following design methodologies are employed to achieve this goal. 1Besides the gain variation, the phase change is another important parameter for EVM. There is a phase jump when the amplifier is switched from the highpower mode to the low-power mode in the DDB operation. Since this phase change is fixed, it is readily compensated during the handset calibration period. C. Circuit Design Considerations 1) Two-Stage Design: A simplified schematic of the prototype two-stage PA with the DDB control is shown in Fig. 6. The driver stage, low-power group, and high-power group are all biased in class AB mode, to achieve the best tradeoff of efficiency and linearity. The driver stage has 20 HBTs and the low-power group has 20 switches and 2 20 HBTs in series. The high-power group uses 100 HBTs and 100 NFET switches. m m and each NFET switch Each HBT emitter is is 45 m/0.25 m. The optimal design of the NFET switches for power gain and 1 dB compression point has been analyzed in [16]. 2) Bias Network: To achieve better linearity [17], a low DC base impedance is employed for the driver stage and the highpower group in the output stage. Since the DC current behavior in the low-power group is determined by the lower 20 devices, a low DC impedance is provided at the bases of these devices. In this way, when the input power increases, the DC current in the low-power group also rises. Consequently, the linearity of the low-power group improves. On the other hand, the top 20 devices are biased with a fixed bias voltage through a resistor to the base, eliminating the need for an extra bias inductor, since the linearity requirement is readily met at low powers. As shown in Fig. 7, the bias network is composed of a helper and a low impedance buffer, to provide a constant voltage bias and to terminate the low-frequency components for improved linearity [18]. The DC impedance is approximately (2) for MHz Based on our simulations, (i.e., the channel bandwidth for WCDMA handset PAs). Fig. 8 shows the simulated third-order intermodulation ratio IMR3 (i.e., the ratio between the third-order intermodulation product and the fundamental tone) at 12 dBm output power and 10-MHz offset frequency. Clearly, the low-frequency termination improves the linearity of the power amplifier. DENG et al.: A SIGE PA WITH DUAL DYNAMIC BIAS CONTROL AND MEMORYLESS DIGITAL PREDISTORTION FOR WCDMA HANDSET APPLICATIONS 1213 Fig. 6. Simplified schematic of a two-stage prototype power amplifier with the dual dynamic biasing in the output stage. Fig. 7. Simplified schematic of the constant voltage bias network. 3) Miscellaneous Details: Ballasting resistors are inserted in the emitter of each transistor to prevent thermal runaway. From to prevent thermal runaway is given [19], a lower bound on by (3) and are the DC collector bias current and voltage, where is the thermal resistance. respectively, and [20], mA and Assuming that , we find to insure thermal stability. The output matching network (OMN) is primarily designed for the high-power group to achieve the maximum output power, i.e., 26 dBm. The OMN transfers the load impedance (50 ) into the load-line impedance (6 ) of the high-power group while resonating the output susceptance. To achieve better power gain and efficiency, the OMN is implemented with high-Q off-chip discrete components. The routing line from the output of the low-power group to inductance that of the high-power group acts as one part of the OMN in the low-power mode to boost the power gain, as depicted in Section II-B. Fig. 8. Simulated third-order intermodulation ratio versus the bias network impedance. III. MEMORYLESS DIGITAL PREDISTORTION FOR LINEARITY IMPROVEMENT Linearization techniques improve the linearity of power amplifiers as well as their maximum output power and efficiency. Memoryless digital predistortion (DP) techniques [10] are attractive for a number of reasons. First, they can be more economical than feed-forward techniques, which are widely applied in base-station PAs [11]. Even though the cost to implement DP in commercial handsets is still high, the demand for wireless high-data-rate applications should keep lowering the cost. Second, DP does not result in the gain loss that is common in analog predistortion techniques [21]. Third, memory effects are not strong in handset PAs compared to base-station PAs, so only memoryless distortion, including gain compression (AM/AM distortion) and phase deviation (AM/PM distortion), needs to be considered and the corresponding predistortion algorithm is straightforward. Finally, since predistortion is implemented 1214 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 5, MAY 2006 Fig. 9. Block diagram of memoryless digital predistortion. with digital signal processing (DSP), it can be performed accurately and flexibly. Therefore, DP is employed to improve the linearity of the prototype WCDMA PA. A. System Topology A block diagram of the DP system is shown in Fig. 9. The DP system downconverts a portion of the 1.95-GHz output signal to an analog IF of 140 MHz, which is then converted to a 12-bit digital second IF of 26.88 MHz at a sample rate of 107.52 MHz and fed to the DSP. After comparison with the corresponding input signal during a “training” period, the resulting error amplitude and phase signal are used to adaptively predistort subsequent input I/Q signals. The predistorted digital signal is converted to a 14-bit analog signal at an IF of 140 MHz, and then upconverted to the final 1.95-GHz output. This digital IF approach was recently demonstrated in a low-power WCDMA upconverter IC [22]. B. Predistortion Algorithm The amount of predistortion is controlled by a look-up table (LUT) in the DSP that characterizes the nonlinearities of the RF PA. For the LUT implementation, a number of predistortion algorithms have been proposed [12]–[14]. A straightforward solution is mapping predistortion. As shown in Fig. 10(a), a two-dimensional table in a random access memory (RAM) contains complex predistorting signals. The mapping table accepts the input signal in Cartesian form as the table address and outto predistort the puts the corresponding correction value signal . The predistorted signal is obtained with the sum of and . The major drawback of this approach is the size of the two-dimensional table (e.g., 2 Mwords in [12]). To overcome the size issue of the mapping predistortion, Faulkner proposed a polar predistortion [13], which contains two one-dimensional tables controlling gain and phase compensations, respectively. As shown in Fig. 10(b), the input signal is predistorted after the gain factor multiplication and phase rotation. In order to find the gain factor in the gain table, the Cartesian input signals need to be converted into the one-dimensional amplitude signal as the address in the gain table. The address of the phase table is obtained by multiplying the amplitude signal with the gain factor. The adaptive correction terms for the gain and phase tables are obtained by comparing the gain and phase differences, respectively, between the input signal and the sampled output signal. Compared with the mapping counterpart, the polar digital predistortion reduces Fig. 10. Predistortion algorithm comparison [23]. (a) Mapping predistortion. (b) Polar predistortion. (c) Complex-gain predistortion. the table size considerably. The size of the polar table is three orders of magnitude less than that of the mapping counterpart [12], as shown in Fig. 11. Cavers [14] presented another approach using a complex-gain table instead of two separate gain and phase tables. As shown in Fig. 10(c), the input signal is predistorted by a complex multiplication between the input signal and the complex gain factor. The address of the complex gain factor is obtained by calculating the squared magnitude of the input signal. The complexgain approach requires more than three orders of magnitude less memory than its mapping counterpart [12] and reduces convergence time. Because of its low memory and fast adaptation, the complex-gain predistortion is adopted as the predistortion algorithm in this paper. DENG et al.: A SIGE PA WITH DUAL DYNAMIC BIAS CONTROL AND MEMORYLESS DIGITAL PREDISTORTION FOR WCDMA HANDSET APPLICATIONS 1215 Fig. 12. Conceptual implementation diagram of complex-gain predistortion [24]. Fig. 11. Look-up table (LUT) comparison. (a) Mapping LUT. (b) Polar LUT. Fig. 13. Block diagram of memoryless digital predistortion. To simplify the above expression, let C. Complex-Gain Digital Predistortion The operating principle of the complex-gain digital predistortion is illustrated in the conceptual implementation diagram shown in Fig. 12. Note that the quadrature up- and down-converters and the reconstruction and anti-aliasing filters are ignored for simplicity. It is straightforward to derive the output as signal (4) is the input signal, denotes the transfer function where of the nonlinear PA, and represents the predistortion cor, is rection function. At time instant , the amplifier output . Hence, equal to the desired output (5) For the ideal amplification with a constant gain . Then (9) The magnitude correction of the predistortion function can be found as (10) Consequently, the way to calculate the magnitude correction of the predistortion function is a procedure of rescaling the input magnitude. The principle of magnitude rescaling is illustrated in Fig. 13. For any input power , the corresponding . The actual amplifier is ideal output power is equal to capable of yielding the same output power, but at the scaled . Therefore, . This inverse input power scaling is readily described in (10). is simply the inverse of the phase The phase correction error at the rescaled magnitude: (11) (6) Combining (5) and (6), we have D. Practical Issues (7) Assume that components of yields and are the magnitude and phase . Taking the magnitude of both sides of (7) (8) From the output of the DSP to the input of the PA, the predistorted signal passes through the transmitter IC (TxIC), which consists of a D/A converter, a reconstruction filter, and a modulator. To maximize the overall system performance, it is critical to analyze and correct the nonidealities of the TxIC, including phase deviation of the reconstruction filter [25] and I/Q imbalance of the modulator [24]. 1216 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 5, MAY 2006 TABLE II EFFECTS OF DIFFERENT RECONSTRUCTION FILTERS WITH f Fig. 14. Visualization of a two-tone test in a transmitter. (a) Without digital predistortion and with an ideal TxIC. (b) With digital predistortion and an ideal TxIC. (c) With digital predistortion and a nonlinear TxIC. Fig. 15. Magnitude and phase responses of an ideal analog filter, where is the phase deviation of the IMD3 relative to the fundamental tone. 1) Phase Deviation: To simplify the analysis, a two-tone test in a transmitter will be analyzed here. Fig. 14(a) shows the case without digital predistortion and with an ideal TxIC, where a third-order intermodulation product (IMD3) occurs at the output of the nonlinear PA. Fig. 14(b) demonstrates the case with digital predistortion and an ideal TxIC. Two pre-generated IMD3 and ) together with two fundaproducts ( mental tones ( and ) are transmitted to the input of the nonlinear PA. Without any dispersion by the ideal TxIC, the resultant IMD3 becomes zero at the output of the nonlinear power amplifier, due to the cancellation of the digitally generated products and the nonlinear products of the amplifier. In the case with a nonideal TxIC, there is a phase deviation ) relative to the funof the pre-generated IMD3 (e.g., damental tone (e.g., ). As shown in Fig. 14(c), the resultant IMD3 will be greater than zero and hence the linearization performance is degraded. The reconstruction filter yields the major phase deviation in the TxIC. The magnitude and phase responses of an ideal analog the filter is shown in Fig. 15, where is the filter order, 3 dB frequency, (e.g., ) and (e.g., ) = 40 MHz Fig. 16. Vector analysis of IMD3 cancellation. the fundamental and third-intermodulation tones, respectively, relative to . Generally, and the phase deviation of there is negligible amplitude deviation, since the filter magni. The phase shift of tude response remains flat when relative to the DC frequency will be neglected here for simplicity, since it is typically small. As an example, different types of seventh-order2 filters are , compared with the phase deviation in Table II, where , and are assumed to be 40 MHz,3 2 MHz, and 4 MHz, respectively. The resulting IMD3 degradations are also listed. As expected, elliptic filters achieve the best performance of the three types of filters, due to their flatter phase response within the passband. A simple vector analysis can be used to illustrate this cancellation degradation problem [26]. In Fig. 16, vectors A1 and A2 are the IMD3 and anti-IMD3 sidebands generated by the PA and the PD, respectively, for the case without a filter. The initial phase of A1 is and the phase difference of A1 and A2 is . The amplitude of the IMD3 after cancellation is A3: (12) The filter can alter both the amplitude and phase of the fundamental and predistorted sideband components. For simplicity, we make several assumptions. First, the baseband amplitude variation is ignored, which is reasonable since most filters for this application will have small passband ripple—usually less than 0.5 dB. Second, there are no PM to AM and PM to PM distortions in the PA, which is also reasonable, if the PA is represented by a quasi-memoryless model. With these assumptions, and have the the filtered IMD3 and anti-IMD3 vectors same amplitude as A1 and A2, but the phase difference between instead of due to the different them is changed to 2Here, 3The a seventh-order filter is chosen as a representative realistic order [25]. predistorted input signal after the DSP has wider bandwidth than that of an ideal input signal without the digital predistortion. Consequently, the D/A converter and the reconstruction filter need to be very wideband to accommodate the predistorted signal. In our experimental predistortion system, the bandwidth of the reconstruction filter is selected to be 40 MHz. DENG et al.: A SIGE PA WITH DUAL DYNAMIC BIAS CONTROL AND MEMORYLESS DIGITAL PREDISTORTION FOR WCDMA HANDSET APPLICATIONS 1217 phase shift within the passband of the filter shown in Fig. 15. : The amplitude of the new IMD3 after cancellation is (13) Using (12) and (13), the cancellation degeneration due to the phase dispersion can be quantified. To maximize the predistortion system performance, it is necessary to correct the phase deviation due to the reconstruction filter in the predistortion algorithm. In [27], this “memory effect” has been effectively compensated with an iterative technique of successive approximations. The effect can be corrected as follows: • Memoryless distortion extraction. By applying a single tone signal to the nonlinear amplifier, the AM/AM and AM/PM distortions are extracted. Accordingly, a memoryless predistortion table is generated in the DSP. • Memory effect extraction. Based on the memoryless predistortion table, a two-tone signal with varying tone spacing is predistorted. After letting the resulting predistorted signal pass through the transmitter and sampling the amplifier output signal, the memory effect due to the phase deviation of the reconstruction filter is characterized at each frequency offset with the AM and PM tables. • Frequency domain correction. The predistorted time domain input signal is transformed into the frequency domain through the fast Fourier transform (FFT). Based on the PM table generated in the previous step, a phase equalizer is employed in the frequency domain to adjust individual phases at different frequencies. Therefore, the phase deviation due to the reconstruction filter will be corrected at the IMD3 frequency. Then the resultant signal is transformed back into a time-domain signal through the inverse fast Fourier transform (IFFT). This time domain signal will be transmitted to the A/D converter. With the above procedure, the phase deviation due to the reconstruction filter is compensated. 2) I/Q Imbalance: It is important to maintain equal gains and exactly 90 degree phase difference between the in-phase (I) and quadrature (Q) paths of the upconversion chain. Any disparity in gain and phase will respectively yield amplitude- and phase-dependent amplitude (AM-AM and PM-AM) distortion. Since an amplitude-based predistortion algorithm will not correct phase-dependent errors, I/Q imbalance needs to be separately corrected in the DSP. I/Q imbalance can be measured by transmitting a sine wave on the I path and a cosine wave on the Q path , where the I path LO signal is assumed to be perfect for simand are the amplitude and phase errors plicity, and of the Q path LO signal. Therefore, at the output the upconverter, we have (14) (15) in which the output amplitude is found to be at the desired frequency (16) where the output amplitude error is (17) which includes PM-AM distortion as well as AM-AM distortion. is given by Furthermore, the output phase (18) Consequently, the output phase error is nonlinear and comprises both AM-PM and PM-PM distortions. In general, I/Q imbalance is compensated digitally [28] with less expense and higher precision. A simple criterion for the compensation algorithm is employed by observing the output at the image frequency , which is amplitude readily found to be (19) and As shown in Fig. 17, there are two tones at , respectively, on the resulting output spectrum, with the first being much larger than the second. Assuming that I/Q imbalance has been compensated perfectly (i.e., both and are zero) and there are no other modulator imperfecwill be completely suptions, the second tone at pressed (i.e., (19) is zero). 1218 IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 5, MAY 2006 Fig. 17. Output spectrum showing imperfectly and perfectly balanced IQ modulations. Fig. 20. Photograph of the packaged die of the prototype power amplifier. The die area is 1.8 mm . Fig. 18. Measured input/output behavior without digital predistortion—measured data (dots), ideal performance (dashed line). Fig. 19. Measured input/output behavior with digital predistortion—measured data (dots), ideal performance (dashed line). E. Experimental Validation The effectiveness of digital predistortion is checked by comparing the AM/AM relationship between input and output envelope amplitudes. Fig. 18 shows the AM/AM curve without digital predistortion. With digital predistortion, the output amplitude has been thoroughly linearized, as shown in Fig. 19. Based on the above discussions, digital predistortion is an effective linearization technique for handset PAs. IV. MEASUREMENT RESULTS The prototype two-stage PA with the dual dynamic bias control was fabricated in a 0.25- m SiGe BiCMOS process [29]. The die area is 1 mm 1.8 mm. A packaged die with bonding wires is shown in Fig. 20. The Micro Lead Frame (MLF20) package is used due to its small body size and short bond-wires along with excellent electrical and thermal performance. Fig. 21 compares the measured DC currents for different biasing approaches for the two-stage WCDMA PA, superimposed on a representative probability distribution function for the output power [15]. These approaches include constant base voltage (CV) biasing with a fixed number of parallel transistors (the traditional Class-AB approach) and the dual dynamic bias (DDB) proposed here. Their corresponding power-added efficiencies (PAEs) are compared in Fig. 22, where the DDB PA achieves much better PAE in the low-power region. As shown in Fig. 23, average power efficiencies are calculated from (1) to be: 1.9% for CV biasing, 3.8% for the DCB approach proposed earlier [16]4 and 5.0% for DDB, all in two-stage PAs. This verifies that DDB does achieve dramatically improved average efficiency for WCDMA applications. With a WCDMA reverse-link signal, the linearity of the power amplifier is measured in terms of ACPR for two cases: with and without digital predistortion (DP). The measured results at the output power of 22.4 dBm are shown in Fig. 24, where the ACPR performance of the power amplifier is improved by 10 dB with digital predistortion. The ACPR measurement at 5 MHz is shown in Fig. 25. Note that it is only necessary to utilize the predistortion in the highpower mode, so DP is not applied in the low-power mode; this is the reason for the large discontinuity in ACPR in the “after DP” curve. The ACPR is improved by at least 8 dB with digital predistortion, and the maximum output power satisfying the WCDMA linearity specification is improved from 22.4 dBm to 26 dBm. This satisfies the WCDMA Class 3 requirement of maximum output power. Correspondingly, the peak PAE is improved by 60% (from 17% to 27%). Fig. 26 shows the measured gain of the DDB PA with DP. The gain change for DDB is less than 1.8 dB, which is much 4Note that the average power efficiency reported in [16] is based on a single output stage; therefore it is higher than what are reported here based on a twostage power amplifier, where the driver stage adopts the classical CV bias considering the gain degradation and circuit complexity. DENG et al.: A SIGE PA WITH DUAL DYNAMIC BIAS CONTROL AND MEMORYLESS DIGITAL PREDISTORTION FOR WCDMA HANDSET APPLICATIONS 1219 Fig. 24. Comparison of measured spectrum with DP (dark line) and without DP (light line). Fig. 21. Output power probability distribution function Pe and measured DC current comparison for different biasing techniques (CV: constant voltage biasing; DDB: dual dynamic biasing). The switch point from high-power mode to low-power mode is 16 dBm. Fig. 25. Measured ACPRs of the DDB power amplifier with digital predistortion (DP) (before DP and after DP). Fig. 22. Measured power-added efficiency (PAE) of CV and DDB power amplifiers. Fig. 26. Measured gain of the DDB power amplifier with DP. Fig. 23. Average power efficiency comparison (CV: constant base voltage; DCB: dynamic current biasing; DDB: dual dynamic bias) in a two-stage power amplifier. in a SiGe HBT BiCMOS technology. With the proposed dual dynamic bias technique, the average power efficiency of the power amplifier is improved from 1.9% to 5.0%. With the complex-gain digital predistortion, the ACPR and the peak PAE of the power amplifier are improved by 8 dB and 60%, respectively. The measured maximum output power is 26 dBm, and the peak PAE is 27%. ACKNOWLEDGMENT more constant than the case if the power amplifier is operated with dynamic bias without changing the device size. V. CONCLUSION An integrated two-stage power amplifier chip with dual dynamic bias control and memoryless digital predistortion for WCDMA handset applications was fabricated and measured The authors would like to acknowledge useful discussions with Mr. M. Li and Mr. H. Khatri, both of the University of California at San Diego. REFERENCES [1] A. Raghavan, D. Heo, M. Maeng, A. Sutono, K. Lim, and J. Laskar, “A 2.4 GHz high efficiency SiGe HBT power amplifier with high-Q LTCC Harmonic suppression filter,” in IEEE MTT-S Int. Microwave Symp. Dig., 2002, pp. 1019–1022. 1220 [2] J. Pusl, S. Sridharan, P. Antognetti, D. Helms, A. Nigam, J. Griffiths, K. Louie, and M. Doherty, “SiGe power amplifier ICs with SWR protection for handset applications,” Microwave J., Jun. 2001 [Online]. Available: http://www.mwjounal.com [3] TS 25.101(V5.3.0), 3GPP Standard, 2002. [4] J. F. Sevic, “Statistical characterization of RF power amplifier efficiency for CDMA wireless communication systems,” in Proc. Wireless Communications Conf., 1997, pp. 110–113. [5] D. Dening, “Setting bias points for linear RF amplifiers,” Microwaves & RF, Jun. 2002 [Online]. Available: http://www.mwrf.com [6] T. Fowler, K. Burger, N. S. Cheng, A. Samelis, E. Enobakhare, and S. Rohlfing, “Efficiency improvement techniques at low power levels for linear CDMA and WCDMA power amplifiers,” in IEEE RFIC Symp. Dig. Papers, 2002, pp. 41–44. [7] G. Hanington, P. Chen, P. M. Asbeck, and L. E. Larson, “High-efficiency power amplifier using dynamic power-supply voltage for CDMA applications,” IEEE Trans. Microw. Theory Tech., vol. 47, no. 8, pp. 1471–1476, Aug. 1999. [8] F. Wang, A. Yang, D. Kimball, L. E. Larson, and P. M. Asbeck, “Design of wide-bandwidth envelope-tracking power amplifiers for OFDM applications,” IEEE Trans. Microw. Theory Tech., vol. 53, no. 4, pp. 1244–1255, Apr. 2005. [9] J. Deng, P. Gudem, L. E. Larson, D. Kimball, and P. M. Asbeck, “A SiGe PA with dual dynamic bias control and memoryless digital predistortion for WCDMA handset applications,” in IEEE RFIC Symp. Dig. Papers, 2005, pp. 247–250. [10] N. Ceylan, J. Mueller, and R. Weigel, “Optimization of EDGE terminal power amplifiers using memoryless digital predistortion,” IEEE Trans. Microw. Theory Tech., vol. 53, no. 2, pp. 515–522, Feb. 2005. [11] K. Cho, J. Kim, and S. Stapleton, “A highly efficient Doherty feedforward linear power amplifier for W-CDMA base-station applications,” IEEE Trans. Microw. Theory Tech., vol. 53, no. 1, pp. 292–300, Jan. 2005. [12] Y. Nagata, “Linear amplification technique for digital mobile communications,” in Proc. IEEE Vehicular Technology Conf., 1989, pp. 159–164. [13] M. Faulkner and M. Johansson, “Adaptive linearization using predistortion-experimental results,” IEEE Trans. Veh. Technol., vol. 43, no. 5, pp. 323–332, May 1994. [14] J. K. Cavers, “Amplifier linearization using a digital predistorter with fast adaptation and low memory requirements,” IEEE Trans. Veh. Technol., vol. 39, no. 11, pp. 374–382, Nov. 1990. [15] P. Asbeck, Univ. California, San Diego, private communication, Apr. 2003. [16] J. Deng, P. Gudem, L. Larson, and P. Asbeck, “A high-average-efficiency SiGe HBT power amplifier for WCDMA handset applications,” IEEE Trans. Microw. Theory Tech., vol. 53, no. 2, pp. 529–537, Feb. 2005. [17] P. Gudem and L. E. Larson, UCSD Wireless Communication Circuit Design, Course Materials, Univ. California, San Diego, 2002. [18] V. Aparin and C. Persico, “Effect of out-of-band terminations on intermodulation distortion in common-emitter circuits,” in IEEE MTT-S Int. Microwave Symp. Dig., 1999, vol. 3, pp. 977–980. [19] M. G. Adlerstein, “Thermal stability of emitter ballasted HBTs,” IEEE Trans. Electron Devices, vol. 45, no. 8, pp. 1653–1655, Aug. 1998. [20] J. Rieh, J. Johnson, S. Furkay, D. Greenberg, G. Freeman, and S. Subbanna, “Structural dependence of the thermal resistance of trench-isolated bipolar transistors,” in IEEE BCTM Tech. Dig., 2002, pp. 100–103. [21] K. Yamauchi, M. Nakayama, Y. Ikeda, H. Nakaguro, N. Kadowaki, and T. Araki, “An 18 GHz-band MMIC linearizer using a parallel diode with a bias feed resistance and a parallel capacitor,” in IEEE MTT-S Int. Microwave Symp. Dig., 2000, vol. 3, pp. 1507–1510. [22] V. Leung, L. E. Larson, and P. S. Gudem, “Digital-IF WCDMA handset transmitter IC in 0.25 m SiGe BiCMOS,” IEEE J. Solid-State Circuits, vol. 39, no. 12, pp. 2215–2225, Dec. 2004. [23] L. Sundstrom, “Digital RF power amplifier linearizers—analysis and design,” Ph.D. dissertation, Lund Univ., Lund, Sweden, Aug. 1995. [24] “Real time adaptive digital baseband predistortion,” White Paper, Ericsson, 2002. [25] L. Sundstrom, M. Faulkner, and M. Johansson, “Effects of reconstruction filters in digital predistortion linearizers for RF power amplifiers,” IEEE Trans. Veh. Technol., vol. 44, no. 2, pp. 131–139, Feb. 1995. [26] M. Li, J. Deng, L. Larson, and P. Asbeck, “Nonideal effects of reconstruction filter and I/Q imbalance in digital predistortion,” presented at the IEEE Radio and Wireless Symp., San Diego, CA, 2006. IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 41, NO. 5, MAY 2006 [27] P. Draxler, J. Deng, D. Kimball, I. Langmore, and P. M. Asbeck, “Memory effect evaluation and predistortion of power amplifiers,” presented at the IEEE MTT-S Int. Microwave Symp., Long Beach, CA, 2005. [28] J. Glas, “Digital I/Q imbalance compensation in a low-IF receiver,” in Proc. IEEE Global Telecommunications Conf., 1998, pp. 1461–1466. [29] IBM 6HP BiCMOS Process. [Online]. Available: http://www-3.ibm. com/chips/techlib/techlib.nsf/products/BiCMOS_6HP Junxiong Deng (S’02–M’05) received the B.S. degree in electrical engineering from Southeast University, Nanjing, China, in 1997, and the M.S. and Ph.D. degrees in electrical engineering from the University of California at San Diego (UCSD), La Jolla, in 2003 and 2005, respectively. His doctoral research concerned high-efficiency and high-linearity power amplifiers for advanced wireless communication systems. He is currently a Senior Design Engineer with Qualcomm, San Diego, CA, where he has worked on RF/analog design for next-generation wireless handset applications. Prasad S. Gudem (M’96) received the Ph.D. degree in electrical and computer engineering from the University of Waterloo, Waterloo, ON, Canada, in 1996. His doctoral research concerned the modeling and numerical simulation of amorphous silicon devices. After a brief time with Mitel Semiconductors, Kanata, ON, Canada, he joined Cadence Design Systems, San Diego, CA, where he was involved with semiconductor-device modeling for analog and RF applications. In August 2000, he joined the Watson Research Center, IBM, where he was involved with RF integrated-circuit design for WCDMA applications using IBM’s SiGe technology. He was also appointed a Lecturer with the University of California at San Diego, La Jolla, where he taught a three-quarter course on communication circuit design. He recently joined Qualcomm Inc., San Diego, CA, where he continues to work on RF circuit design for wireless applications. Lawrence E. Larson (S’82–M’86–SM’90–F’00) received the B.S. and M.Eng. degrees in electrical engineering from Cornell University, Ithaca, NY, in 1979 and 1980, respectively, and the Ph.D. degree in electrical engineering from the University of California at Los Angeles (UCLA) in 1986. From 1980 to 1996, he was with Hughes Research Laboratories, Malibu, CA, where he directed the development of high-frequency microelectronics in GaAs, InP, and Si/SiGe and MEMS technologies. In 1996, he joined the faculty of the University of California at San Diego (UCSD), La Jolla, where he is Inaugural Holder of the Communications Industry Chair. He is currently Director of the UCSD Center for Wireless Communications. During the 2000–2001 academic year, he was on leave with IBM Research, San Diego, CA, where he directed the development of RF integrated circuits (RFICs) for third-generation (3G) applications. He was a Visiting Professor at TU Delft in the Netherlands during the 2004–2005 academic year. He has authored or coauthored over 200 papers. He holds 31 U.S. patents. Dr. Larson was the recipient of the 1995 Hughes Electronics Sector Patent Award for his work on RF MEMS technology. He was co-recipient of the 1996 Lawrence A. Hyland Patent Award of Hughes Electronics for his work on lownoise millimeter-wave high electron-mobility transistors (HEMTs), the 1999 IBM Microelectronics Excellence Award for his work in Si/SiGe HBT technology and the 2003 Custom Integrated Circuits Best Invited Paper Award. DENG et al.: A SIGE PA WITH DUAL DYNAMIC BIAS CONTROL AND MEMORYLESS DIGITAL PREDISTORTION FOR WCDMA HANDSET APPLICATIONS Donald F. Kimball (S’82–M’83) was born in Cleveland, OH, in 1959. He received the B.S.E.E. (summa cum laude) and M.S.E.E. degrees from The Ohio State University, Columbus, in 1982 and 1983, respectively. From 1983 to 1986, he was a TEMPEST Engineer with the Data General Corporation. From 1986 to 1994, he was an Electromagnetic Compatibility Engineer/Manager with Data Products New England. From 1994 to 1999, he was a Regulatory Product Approval Engineer/Manager with Qualcomm, Inc. From 1999 to 2002, he was a Research and Technology Engineer/Manager with Ericsson, Inc. Since 2003, he has been a Principal Development Engineer with Cal(IT)2 with the University of California at San Diego, La Jolla. He holds four U.S. patents with two patents pending associated with high-power RF amplifiers (HPAs). His research interests include HPA EER techniques, switching HPAs, adaptive digital predistortion, memory effect inversion, mobile and portable wireless device battery management, and small electric-powered radio-controlled autonomous aircraft. 1221 Peter M. Asbeck (M’75–SM’97–F’00) received the B.S. and Ph.D. degrees from the Massachusetts Institute of Technology (MIT), Cambridge, in 1969 and 1975, respectively. He is the Skyworks Chair Professor in the Department of Electrical and Computer Engineering, University of California at San Diego (UCSD), La Jolla. He worked at the Sarnoff Research Center, Princeton, NJ, and at Philips Laboratory, Briarcliff Manor, NY, in the areas of quantum electronics and GaAlAs-GaAs laser physics and applications. In 1978, he joined Rockwell International Science Center, where he was involved in the development of high-speed devices and circuits using III-V compounds and heterojunctions. He pioneered the effort to develop heterojunction bipolar transistors based on GaAlAs-GaAs and InAlAs-InGaAs materials and has contributed widely in the areas of physics, fabrication and applications of these devices. In 1991, he joined the UCSD. His research interests are in development of high-speed heterojunction transistors and their circuit applications. His research has led to more than 250 publications. Dr. Asbeck is a Distinguished Lecturer for the IEEE Electron Devices Society and the Microwave Theory and Techniques societies. He received the 2003 IEEE David Sarnoff Award for his work on heterojunction bipolar transistors.