* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download EEE331-Exp-6

Thermal runaway wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Galvanometer wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Index of electronics articles wikipedia , lookup

Operational amplifier wikipedia , lookup

Regenerative circuit wikipedia , lookup

Integrated circuit wikipedia , lookup

Opto-isolator wikipedia , lookup

Rectiverter wikipedia , lookup

Current source wikipedia , lookup

RLC circuit wikipedia , lookup

Interferometry wikipedia , lookup

Power MOSFET wikipedia , lookup

Two-port network wikipedia , lookup

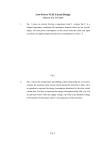

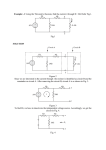

İzmir University of Economics ETE 331 Analog Electronics - Lab EXPERIMENT 6 MOSFET Current Sources A. Background The short circuit connection between gate and source in the NMOS circuit given in Fig. 6.1 guarantees the condition that NMOS is in SAT region as long as VGS ≥ VTN. VDD IR RF + D VDS B G S - Fig. 6. 1. NMOS DC Circuit A simple current source may be formed by connecting another NMOS transistor as shown in Fig. 6.2. If the transistors MR and MO are matched, then the current IO through the transistor MO is equal to IR. So the change in RD will not effect the current IO. However due to Early effect at output characteristics, IO may be slightly changed as a result of the large changes in RD. VDD RF MR IR RD IO MO Fig. 6.2. Simple Current Mirror 6-1 B. Preliminary Work a) Consider the NMOS circuit given in Fig. 6.3. Assume VDD = 12 V. Determine the value of RF to set the current IR = 1 mA, using the transistor parameters obtained in Experiment 2. VDD IR RF + D VDS B G S - Fig. 6. 3. NMOS Circuit b) Add MO and RO to the circuit as given in Fig. 6.3 as shown in Fig. 6.4; to form a simple current mirror to be used as a current source. Assume MR and MO are matched with the same parameters. With VDD = 12 V, and the value of RF as obtained in part (a), and RD = 5 k, determine IO and VDSO. VDD RF IR RD IO + MR MO VDSO - Fig. 6.4. Simple Current Mirror 6-2 C. Experimental Work C.1. NMOS Biasing 1. Set up the circuit given in Fig. 6.5. with VDD= 15 V, RF1= 5.6 k, RF2 as a potentiometer of value 50 k. VDD RF1 5.6K RF2 50K IF A + D VDS V B G S - Fig. 6. 5. NMOS Biasing 2. Adjust IR = 1 mA and measure VGS = VDS= ……………… V. 3. Calculate RF1 + RF2. RF1 + RF2 = …………… k. C.2. NMOS Simple Current Mirror 4. Set up the circuit given in Fig. 6.6. by modifying Fig. 6.5. VDD RF1 5.6K RF2 50K IF RO 4.7K IO A + V VDSO - Fig. 6. 5. NMOS Biasing 5. Measure IO and VDSO. IO = ………….. mA and VDSO = ……………….V. 6. Repeat Part 5, for RO = 10 K. IO = ………….. mA and VDSO = ……………….V. 7. Comment on the differences between IO and IR. 6-3