* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download review material

List of first-order theories wikipedia , lookup

Mathematics of radio engineering wikipedia , lookup

Location arithmetic wikipedia , lookup

Functional decomposition wikipedia , lookup

History of the function concept wikipedia , lookup

Elementary mathematics wikipedia , lookup

Principia Mathematica wikipedia , lookup

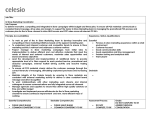

ECE3223 – Microprocessor Systems Design Prof. MP Tull REVIEW MATERIAL NUMBER SYSTEMS: Base-2 or Binary Integers 1. Signed Magnitude 2. 1’s-Complement (Diminished Radix Complement) 3. 2’s-Complement (Radix Complement) For 8-bit signed 2’s complement, the number line looks like: -128 0 +127 10000000 00000000 01111111 The most significant bit (msb) is the sign bit. The 1’s-complement of a binary number is found by simply inverting each bit. Finding the 2’s-complement is important since it allows us to negate a number and is the method used by most Arithmetic and Logic Units (ALUs) for subtracting. There are two easy ways to find the 2’s-complement: 1. Find the 1’s-complement and add 1. 2. Examine the number, beginning with the least significant bit (lsb), writing down 0’s until the first (rightmost) 1 is found. Leave this bit a 1 and invert all bits to the left. Adding signed 2’s-complement numbers is shown below: Add two positives Add a negative to a positive Add two positives with overflow 00101011 00101011 01101011 +00010001 + 10010001 +01110000 00111100 10111100 11011011 Note that overflow is possible in all limited precision ALUs. It results from adding two positive (or two negative) numbers and getting a negative (positive) number, i.e., the sign bit changes. A carry-out from the sign bit is NOT an indication of overflow for signed 2’s-complement numbers. 2’s-complement subtraction can be performed by finding the 2’s-complement of the minuend and adding it to the subtrahend. ECE3223 – Microprocessor Systems Design Prof. MP Tull REVIEW MATERIAL Octal (base-8) and hexadecimal (base-16) numbers are both convenient number systems for expressing base-2 numbers. Octal groups the binary bits in groups of three bits, while hexadecimal uses four bit groups. The binary number 01110011 is (163) 8 and (73)16. Conversion of decimal (base-10) numbers to binary is most easily performed by successive division of the decimal number by 2 and recording the 0 or 1 remainder until a zero dividend is reached. The first 0 or 1 remainder is the lsb, while the last 0 or 1 remainder is the msb. This is commonly known as the dibble-dabble method and can be used for any number base conversion. LOGIC GATES: The logical operations AND, OR, and NOT form a functionally complete set, i.e., any binary switching function can be expressed using only these operators. NAND is also functionally complete, as is NOR. Common symbols for these gates are: AND OR NOT NAND NOR Alternative symbols for these gates should be used when signals are asserted low. For example, the NAND gate can be interpreted as ORing lows, in which case the symbol below is used: AND, OR, NOR, and NOT all have alternative symbols. Two other common gates are exclusive-or and exclusive-nor (coincidence function). XOR XNOR ECE3223 – Microprocessor Systems Design Prof. MP Tull REVIEW MATERIAL SWITCHING FUNCTIONS: The sum-of-products (SOP) and product-of-sums (POS) are two methods of expressing switching functions. A SOP or AND-OR function is written as the OR of min-terms: f(X,Y,Z) = XY + XZ’ + X’Y’Z’ while the POS or OR-AND function is written as the AND of max-terms: f(X,Y,Z) = (X + Y’)(Y + Z)(X’ + Z’). It is not always evident if an algebraic SOP or POS expression is minimal. Canonical form of a switching function expresses all min-terms or max-terms either algebraically or in a special notational form: SOP: f(X,Y,Z) = m(0,4,6,7) POS: f(X,Y,Z) = M(1,2,3,5) DeMorgan’s Theorem can be applied to convert any two-level AND-OR circuit to a twolevel NAND-NAND circuit, or any two-level OR-AND circuit to a two-level NOR-NOR circuit. When the number of variables is low (<6), Karnaugh Maps (K-Maps) provide a way to minimize switching functions so that a minimal circuit can be implemented. (The QuineMcClusky method can handle more than 6 variables, but is still tedious to perform by hand.) A minimal SOP is obtained from the K-Map by grouping 1’s; a minimal POS is obtained by grouping 0’s. From the K-Map below, the following SOP and POS functions are obtained: AB C 00 01 11 10 0 1 0 d 1 f(A,B,C) = A’B’+AB+AC’ 1 1 0 1 0 f(A,B,C) = (A+B’)(A’+B+C’) When the don’t-care terms are grouped with 1’s, the function will have an output of 1 for the don’t-care min-term, and 0 when it is included with 0’s. ECE3223 – Microprocessor Systems Design Prof. MP Tull REVIEW MATERIAL The SOP or POS form that provides a minimal gate count is considered to be the best circuit implementation. Hazards may be a consideration. Hazards result from adjacent min-terms or max-terms that are included in different groups of 1’s or 0’s. The SOP and POS circuits are: SOP POS A' A B' B' A f f B A' B C' A C DECODERS: Decoders such as the 3-to-8 line decoder (74138) can generate all min-terms or maxterms of three variables and can implement any three variable SOP or POS. Using a 74138 decoder for the previous circuit we have: +5V 138 G1 G2A G2B A B C C B A Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 f We should use the other symbol for the NAND gate, but it is not available in my symbol library. MULTIPLEXERS: Multiplexers (MUXs) can also implement switching functions, although they are also used to steer or select data. Using a 4-to1 line MUX for the circuit above we have: +5V EN A B C' S1 S0 D3 D2 D1 D0 Q f ECE3223 – Microprocessor Systems Design Prof. MP Tull REVIEW MATERIAL ARITHMETIC & LOGIC UNIT: A simple ALU circuit is shown below: B4-B7 A4-A7 B0-B3 A0-A3 Logic Function Select B0 3D1 3D0 2D1 2D0 1D1 1D0 3Q 2Q 1Q 13 S0 CIN 15 S3 2 S2 6 S1 9 83 CI A3 1 A2 3 A1 8 A0 10 4D1 4D0 4Q S0 16 B3 4 B2 B1 7 B0 11 EN CI S0 CO 1D1 1D0 1Q 83 15 S3 2 S2 6 S1 9 14 Z0 3D1 3D0 2D1 2D0 1D1 1D0 3Q 2Q 1Q 1Q 4D1 4D0 1D1 1D0 2Q 4Q 2D1 2D0 3Q S0 3D1 3D0 4Q EN 4D1 4D0 S0 ALU Output Select EN Logic Unit Bits 1-6 Not Show n 13 Q Q ..... Z7 1 2D1 2D0 2Q CO B3 B2 B1 B0 D3 D2 D1 D0 S1 S0 EN D3 D2 D1 D0 S1 S0 EN COUT 14 A3 3 A2 8 A1 10 A0 3D1 3D0 3Q 16 4 7 11 4D1 4D0 4Q A0 EN A7 S0 B7 ALU OUT Notice the use of MUXs for selecting and steering of data as well as generating the logic functions in the Logic Unit. FLIP-FLOPS: The D latch and D flip-flop (positive or negative edge triggered), the Set-Reset, and JK flip-flops (edge triggered) comprise the generally available types. When needed, Toggle and clocked Toggle flip-flops are made from D or JK flip-flops but are not generally available from vendors. ECE3223 – Microcprocessor Systems Design Prof. MP Tull REVIEW MATERIAL A toggle flip-flop is made from a D or JK as shown below: +5V Toggle D CLK S Q C R Q CLK S J Q C K R Q A clocked toggle is made from a JK as shown below: T CLK S J Q C K R Q Note that these symbols should show the > on the clock pin to indicate edge triggering.