* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download UCD90XX Reset Behavior

History of electric power transmission wikipedia , lookup

Three-phase electric power wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Electrical ballast wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Current source wikipedia , lookup

Power over Ethernet wikipedia , lookup

Stray voltage wikipedia , lookup

Buck converter wikipedia , lookup

Alternating current wikipedia , lookup

Opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Rectiverter wikipedia , lookup

Power MOSFET wikipedia , lookup

Earthing system wikipedia , lookup

Voltage optimisation wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Surge protector wikipedia , lookup

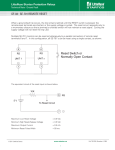

Application Report February 22, 2012 UCD90xxx Sequencer Reset Behavior Introduction: Recently, it has been discovered that the UCD90xxx series of TI’s digital sequencers can exhibit an undesired behavior on the general purpose input-output (GPIO) pins during power ramp up. Depending on the method used to interface with these pins, system level issues may be observed. Generally speaking, non-FPWM GPIO pins will be in a high impedance (HIZ) state when the device is in reset and can be pulled either low or high with resistors to system ground or supply to control the logic state. FPWM GPIO pins will sink current when the device is in reset. The undesired behavior of the GPIO pin can occur during device supply ramp up or ramp down. At low supply voltages (generally less than ~1.7V), the GPIO pins may sink or source current which can cause a negative or positive glitch on the GPIO. Data sheet wording: Currently, the wording in the “DEVICE RESET” section of the UCD90xxx sequencer data sheets contains the following wording: The UCD90xxx has an integrated power-on reset (POR) circuit which monitors the supply voltage. At power up, the POR detects the V33D rise. When V33D is greater than VRESET, the device comes out of reset. The device can be forced into the reset state by an external circuit connected to the RESET pin. A logiclow voltage on this pin for longer than tRESET holds the device in reset. It comes out of reset within 1ms after RESET is released and can return to a logic-high level. To avoid an erroneous trigger caused by noise, connect RESET to a 10kΩ pullup resistor (from RESET to 3.3V) and a 1000pF capacitor (from RESET to AVSS). Any time the device comes out of reset, it begins an initialization routine that lasts about 20ms. During the initialization routine, the FPWM pins are held low, and all other GPIO and GPI pins are open-circuit. At the end of initialization, the device begins normal operation as defined by the device configuration. The implication in the first sentence above is that when the device supply voltage is less than VRESET the device is in reset; FPWM GPIO will sink current and non-FPWM GPIO will be in a HIZ state. Further investigation shows that the data sheet wording should be revised to better clarify the behavior of the GPIO during supply ramp up. The following text is suggested: The UCD90xxx has three different reset mechanisms; RESET1 as determined by the voltage on the supply pin (V33D) RESET2 as determined by the voltage on the RESET pin, or RESET2 by a soft reset command issued over PMBus. The UCD90xxx has an integrated power-on reset (POR) circuit which monitors the supply voltage, V 33D. When V33D is less than VRESET (2.4V maximum) the device is in the RESET1 state and when V 33D is greater than VRESET the device exits the RESET1 state. As V33D increases above ~2.6V, the device begins an initialization routine which includes a flash error log integrity check. Normally, the duration of this initialization routine is approximately 20ms (TINIT in figure 1). If the flash error log integrity check fails, the initialization routine can last for approximately 200ms (except for UCD90124A whose initialization routine is always approximately 20ms). At the end of the initialization routine, the device begins normal operation as defined by the device configuration. During the initialization routine, the device is considered to be in the RESET2 state. 1 . The device can be forced into the RESET2 state by an external circuit connected to the RESET pin (hard reset) while the device is operating within the recommended supply voltage range. A voltage less than VIL for longer than tRESET places the device in RESET2 and a voltage greater than V IH on the RESET pin allows the initialization routine to start. The device can also be forced into RESET2 by issuing the soft reset command (SendByte 0xDB) over PMBus. After the self clearing soft reset command is processed, the initialization routine begins. The state of the GPIO pins during RESET1 and RESET2 can be described as follows; All GPIO: During RESET1 these may sink or source current when ~0.7V < V33D < VRESET FPWM GPIO: During RESET2, these pins sink current Other GPIO: During RESET2, these pins behave as inputs (HIZ) To avoid an erroneous trigger caused by noise, connect RESET to a 10kΩ pullup resistor (from RESET to 3.3V) and a 1000pF capacitor (from RESET to AVSS). VV33D 3.0V < VV33D < 3.6V ~2.6V VRESET RESET1 TINIT RESET2 TINIT RESET2 RESET1 RESET2 Time Hard or Soft RESET asserted Hard or Soft RESET de-asserted UCD90xxx RESET1/RESET2 Behavior Figure 1. UCD90xxx RESET1/RESET2 Behavior Recommended work around: For cases where system circuitry is affected by the GPIO behavior during UCD90xxx supply ramp up, a buffer circuit should be inserted between the UCD90xxx and the system circuitry. 2 UCD90xxx Sequencer Reset Behavior