* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download MOSFET Lab1 - University of Pennsylvania

Stepper motor wikipedia , lookup

Ground loop (electricity) wikipedia , lookup

Signal-flow graph wikipedia , lookup

Three-phase electric power wikipedia , lookup

Power inverter wikipedia , lookup

Electrical substation wikipedia , lookup

History of electric power transmission wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Electrical ballast wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Semiconductor device wikipedia , lookup

Surge protector wikipedia , lookup

Current source wikipedia , lookup

Power electronics wikipedia , lookup

Alternating current wikipedia , lookup

Stray voltage wikipedia , lookup

Two-port network wikipedia , lookup

History of the transistor wikipedia , lookup

Voltage optimisation wikipedia , lookup

Voltage regulator wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Schmitt trigger wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Mains electricity wikipedia , lookup

Buck converter wikipedia , lookup

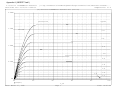

University of Pennsylvania ESE206: Electrical Circuits and Systems II – Lab MOSFET (Field Effect Transistor) Lab 1: NMOS Measurements and Characterization 1. Objectives The objectives of this first Field Effect Transistors (FETs) lab is: 1. To understand the operation of the MOSFET 2. To measure the I-V characteristics and to determine the transistor parameters: a. Threshold voltage Vt, b. Transconductance parameter kn'W/L c. Channel length modulation parameter λ (or Early voltage VA) 3. To illustrate amplification using a MOSFET 2. Background A MOSFET transistor is a three terminal semiconductor device in which current, flowing from the drain-source terminals, is controlled by the voltage on the gate terminal ( Figure 1a). The current-voltage characteristics of a NMOS transistor are shown in Figure 1b. In order for current to flow the gate voltage VGS has to be larger than the threshold voltage Vt. (a) JVdS/2005 1 (b) Figure 1 (a) NMOS transistor showing two different symbols (with biasing voltages) and (b) Drain current ID vs. drain-source voltage VDS with gate-source voltage VGS as a parameter (VGS=1 to 3V in steps of 0.2V). There are two regions in which the transistor operates depending on the voltages one applies. The first region is called the "triode" region and the second one is called "saturation" as indicated in Figure 1b. The current-voltage relationship in each region is given below. 2.1 Triode region (vDS < vGS-Vt) When the drain to source voltage vDS is smaller than vGS-Vt, the transistor operates in the triode region. The currents-voltage relationship is given by, i D = k n' W L 1 2 ⎤ ⎡ ⎢⎣(vGS − Vt )v DS − 2 v DS ⎥⎦ when vDS < (vGS - Vt) (1) The parameter kn' = μnCox is the transconductance parameter, μn is the mobility, Cox is the oxide thickness and W/L the ratio of the channel (or gate) width over length. Notice that when vDS is much smaller than vGS-Vt, the current can be approximated as follows, i D ≈ k n' W (vGS − Vt )v DS L when vDS << (vGS - Vt). (2) Thus the transistor acts as a voltage-controlled resistor whose value is given by (provided that vGS > Vt), JVdS/2005 2 rDS = 1 (3) W k (vGS − Vt ) L ' n 2.2. Saturation region (vDS > vGS-Vt) When the drain to source voltage exceeds the value vGS-Vt, the channel will be pinchedoff and the current can be written as iD = 1 'W k n (vGS − Vt ) 2 L 2 when vDS > (vGS - Vt) (4) In the expression above, the drain current is independent of the drain-source voltage what implies that the transistor acts as an ideal current source in this region. This is only an approximation. In reality, the current will vary slightly with the drain voltage. This variation can be modeled by adding a parameter λ, called the channel length modulation parameter, as shown in the following expression, iD = 1 'W k n (vGS − Vt ) 2 (1 + λv DS ) L 2 when vDS > (vGS - Vt) (5) The channel length modulation parameter λ is usually pretty small (typical values are 0.02 V-1). The output resistance of the transistor in saturation can now be written as, ro = 1 I Dλ = VA ID (6). in which ID is the drain current, and VA (=1/λ) is the Early voltage. 2.3 Determination of the transistor characteristics. The main parameters that characterize a MOSFET are the threshold voltage Vt, the parameter (kn'W/L) and the channel length modulation parameter λ. The first two parameters can be easily found by plotting the square root of the drain current versus the gate voltage vGS, when the transistor is in saturation. Indeed, using equation (4) one can write that 1 'W k n (vGS − Vt ) (7) 2 L The intersection with the horizontal axis gives the threshold voltage Vt. and the slope of this graph corresponds to, iD = JVdS/2005 3 1 ' k nW / L . 2 Slope = (8) 2.4 PMOS transistor The PMOS transistor has similar characteristics. The only difference is that the polarity of the voltages changes, as shown in Figure 2. Figure 2: PMOS transistor showing two symbols and direction of the current flow. The values of the threshold voltage Vt (for enhancement transistor), and of λ and kp' are now negative. The current expressions are then given by, Triode region: i D = k p' W L 1 2 ⎤ ⎡ ⎢⎣(vGS − Vt )v DS − 2 v DS ⎥⎦ when vDS > (vGS - Vt) (9) when vDS < (vGS - Vt) (10) Saturation region: iD = 1 ' W k p (vGS − Vt ) 2 2 L If can takes into account the channel length modulation, the current is given by iD = 1 ' W k p (vGS − Vt ) 2 (1 + λv DS ) 2 L JVdS/2005 when vDS < (vGS - Vt) 4 (11) 2.5 Precaution when handling MOSFETs MOSFET transistors are easily damaged, mainly as a result of static discharge at the gate terminal. For that reason, one should handle MOSFETs with care and not touch the pins of the package. In many cases one uses a ground strap to ground oneself when handling MOSFETs. 3. Pre-lab assignment 3.1 Read the section on "The MOSFET as an Amplifier and Switch," (section 4.4, Sedra-Smith, 5th edition). 3.2 Consider the circuit of Figure 4 in which the gate and drain terminals of the NMOS are shorted together. Assume that the transistor has a Vt=0.7V and a kn'= 0.125mA/V2 and W/L= 5. a. In what region is the transistor operating (Triode, Saturation)? b. Calculate the drain current for the following gate-to-source voltages, vGS=vDS=0, 1, 2, 3, 4, and 6V. Plot the current vs. voltage (use excel or Matlab). 3.3 The same transistor as above is used as a resistor, shown in Figure 5, with the drainsource voltage VDS=0.2V. a. Calculate the value of the drain-source resistance rDS for the following gate voltages: vGS = 3, 4, 5, 6, 7, 8, 9 and 10V. b. Plot the value of the resistance as a function of the gate voltage (using excel or Matlab). 3.4 Consider the circuit of Figure 6 in which the NMOS transistor is used as a basic common-source amplifier. The transistor characteristics are given in Figure 1b.and the Appendix A. a. Using the graph of Figure 1b (see appendix A) and the load line, find graphically the output voltage vDS=vo as a function of the gate voltage vGS, for vGS varying from 1 to 3V in steps of 0.2V. Use the same procedure as explained in the textbook section 4.4.1 (Transfer Characteristic) of Sedra-Smith 5th ed.). Plot the output voltage vDS=vo as a function of the input voltage vin = vGS. Use excel or Matlab to draw this graph (called the transfer function). b. Find the value of the slope of the graph at the point where the output is 5V. This slope corresponds to the amplification of the amplifier. c. For the pre-lab include the two graphs (i.e. the IDS-vGS) with load line and the Transfer characteristic (vDS-vGS). JVdS/2005 5 4. In-Lab Experiments Parts 1 - CD4007 MOS transistor array (data sheet from National Semiconductor) 2 - 0.1 microFarad capacitors 2 - 10 kOhm resistor Power supplies Oscilloscope with FFT module Digital multimeter (Voltage and Current meter) Procedure You will be using the CD4007 MOSFET array that contains three NMOS and three PMOS transistors as shown in Figure 3. The key point to remember when using this array is that the substrate of the NMOS (bulk connection) is connected to pin 7 and should always be connected to the most negative supply voltage. Pin 14 is the substrate of the PMOS and must be connected to the most positive supply voltage in the circuit! Figure 3: The CD4007 MOSFET array. Pin 7 is connected to the substrate of the NMOS and should be connected to the most negative voltage of the circuit; pin 14 is the bulk of the PMOS and should be connected to the most positive voltage in the circuit. (Source: National Semiconductor CD4007 Datasheet) 4.1. IDSvGS characteristics and determination of Vt and kn'W/L The goal of this experiment is to determine the drain current as a function of the gate voltage when the transistor is in saturation. From this characteristic you can determine the threshold voltage and the transconductance parameter. a. Build the circuit of Figure 4. You can use any of the three NMOS transistors of the CD4007 array. The node numbers given on the schematic assume that you use the transistor between the pins 3, 4 and 5. Do not forget to connect the substrate pin 7 to the ground. Place a 0.1 microFarad capacitor between Pin 14 and the ground. Notice that the transistor is always in saturation since vGS= vDS or vGS - Vt < vDS. JVdS/2005 6 Figure 4: NMOS transistor in saturation used to measure iD-vGS characteristic. b. Vary the gate voltage (vGS= vDS) from 0 to 6V in steps of 1V and record the corresponding drain current iD. c. For the report: Plot the ID-vGS graph. Also, calculate the square root of iD and plot the √iD - vGS relationship. Use the method outlined in section 2.3 to find the threshold voltage Vt (the intersection with the horizontal axis) and the transconductance parameter (kn'W/L). 4.2 ID - vDS characteristics and determination of the output resistance ro and λ The objective of the following experiment is to measure the output characteristics of the NMOS transistor: iD-vDS with vGS as a parameter. From this graph you will be able to determine the output resistor ro and the channel length modulation parameter λ. Figure 5: Circuit to measure the output characteristics of a transistor. a. Build the circuit of Figure 5 (or modify the circuit of Figure 3). Use the same transistor as you used for the previous experiment. b. Keep the gate voltage constant at 3V and measure the drain current while varying the drain voltage from 0, 0.5, 1.0, 1.5, 2, 4, 6, 8 to 10V. c. Do the same of a gate voltages vGS of 5V. d. For your report: Plot the two curves on the same graph. Determine the output resistance ro (i.e. the inverse of the slope of the graphs) at a drain voltage of 5V for each graph. Notice that the output resistance decreases with current, as one expects from expression (6). Find the corresponding value of λ and the Early JVdS/2005 7 voltage VA. It is likely that the values you find for λ are slightly different for each graph. In that case, take the average value as the value for the transistor. 4.3 ID - vGS for small values of vDS (determination of the resistance of a MOSFET) In this experiment you will keep the value of the drain voltage small so that the transistor operates in the triode region. Since vDS is kept small the transistor acts as a resistor with a value that is determined by the gate voltage (see expression (3) above). The goal of this experiment is to experimentally determine the resistor values rDS for various gate voltages. a. In the circuit of Figure 5, set the voltage vDS=0.2V so that the transistor will act as a electronically controlled resistor. b. Vary the gate voltage vGS from 3 to 10V in steps of 1V, and record the corresponding drain current iDS. Find also the value of the resistor rDS = (vDS/iDS). c. For the report: determine the resistance rDS from the measurements and plot the value of rDS as a function of the gate voltage vGS. Also, calculate the value of the resistance according to the expression (3) and using the measured values of Vt and kn'W/L. Plot the measured and calculated resistor values on the same graph. Notice the 1/x relationship. 4.4 Large-Signal Operation: Transfer characteristic The objective of this measurement is to determine the transfer characteristic of the MOSFET amplifier, shown in Figure 6. You will determine the output versus the input voltage. The graph you'll obtain will be similar to the one in Fig. 4.26(b) of the textbook (Sedra-Smith, 5th ed., section 4.4.1). From this characteristic you will be able to determine the amplification of this circuit. Figure 6: Common Source NMOS amplifier. a. Build the circuit of Figure 6. b. Vary the gate voltage between 0 and 6V, and record the output voltage vDS. You will notice that the output will change rapidly at one point. When that happens JVdS/2005 8 vary the input voltage in small steps of 0.1V so that you can record the transfer characteristic accurately. It will be useful to make a rough sketch of the characteristic in your lab notebook (or using excel) so see how the transfer characteristic looks like. c. For your report: plot the output voltage as a function of the input voltage. Find the slope of the transfer characteristic around the point where the characteristic is steepest. The slope is the amplification of the amplifier (i.e. the ratio of the output to the input voltage). You'll notice that when the changes in the input voltage around the Q point are kept small, the characteristic is quite linear and gives a constant amplification. For larger values of the input voltage, one will see some distortion in the output signal since the characteristic is not linear for large input signals. Determine the maximum value (in peak-to-peak voltage) of the input signal that gives a relatively constant amplification. 4.5. The MOSFET as a voltage amplifier In this experiment you will build a simple common-source voltage amplifier, similar to the one shown in Figure 6. From the previous experiment you have noticed that the amplification (i.e. the change of output voltage over input voltage) is relatively large around a narrow range of the input voltage (see e.g. Fig. 4.26c in Sedra-Smith, 5th ed.). So, it is important to bias the transistor in the region where the amplification is large. It is for that reason that we need to apply a DC input voltage V1 shown in Figure 7. The actual input signal vin will be superimposed on this DC signal. This can be done by a coupling capacitor C1 shown in Figure 7. The voltage seen at the gate terminal of the transistor will than be the sum of V1 and vin. Figure 7: Common source amplifier with input signal vin is superimposed on the bias voltage V1, using a coupling capacitor C1. a. Build the circuit of Figure 7. Adjust the voltage V1 so that the output voltage vo is around 5V (you can the corresponding vGS from the previous measurement of the transfer characteristic). Use the oscilloscope to verify the value of vo. For the input signal vin use a sinusoidal signal of 5 kHz and amplitude of 200 mV (i.e. 400 mV peak-to-peak). Display this signal on the oscilloscope to verify it value. b. Display the output vo of the amplifier on the oscilloscope together with the input signal. Measure the amplitude of the output signal. What is the corresponding JVdS/2005 9 c. d. e. f. value of amplification (i.e. the ratio of the amplitude of the output sinusoid to the input sinusoid)? What do you notice about the phase relationship between the input and output signal? Is the signal distorted? Take a snapshot of the input and output signals for your report. You may change the amplitude of the input and see if the distortion improves or deteriorates. You can see the effect of the non-linearity of the amplifier better when you switch to a triangular input signal. Notice the distortion (or lack of distortion). Take a snapshot for your report. Switch the input back to a sinusoid with 5 kHz frequency. Set the amplitude so that the output signal is not too much distorted. Take the FFT of the output signal and determine the amplitude (in dB) and position (frequency) of the peaks. If the signal is not distorted you should have a single peak at a frequency of 5kHz. The presence of peaks at multiples of the fundamental frequency of 5kHz indicates that the signal is distorted. It is normal to see multiple peaks for this simple amplifier. Later we'll discuss ways to reduce the distortion. Take a snapshot for your report. Determine the cut-off frequencies (i.e. the 3-dB where the amplitude of the output signal has decreased by 3-dB). Do this by changing the frequency of the input signal from a few tens of Hz up to hundred of kHz. Record the values of the two 3-dB points. What is bandwidth of the amplifier? For your report: • Compare the value of the amplification determined in this experiment with the value obtained from the transfer characteristic (previous experiment of section 4.4). • What is the phase relationship between input and output? Can you explain the phase relationship? • From the FFT determine the total harmonic distortion THD of the output signal (for definition of total harmonic distortion see previous lab on AM Demodulator: www.seas.upenn.edu/~ese216/labs/ AMDemodLabOpAmpPart2.pdf. • The coupling capacitor and resistor R1 in Figure 7 acts as a high pass filter. Calculate the corresponding 3-dB point of this filter. Express the value in Hz. Compare this value to the one measured in the lab (low frequency 3-dB point). References 1. "Microelectronic Circuits, Sedra, Smith, 5th edition, Oxford University Press, New York, 2004. 2. "The Art of Electronics", Horowitz and Hill, Cambridge University Press. 3. "CD4007M/CD4007C Dual Complementary Pair Plus Inverter" Datasheet, National Semiconductor, 1995. Created by Jan Van der Spiegel jan_at_seas.upenn.edu April 5, 2005 JVdS/2005 10 Appendix A (MOSFET Lab1) ** Profile: "SCHEMATIC1-DCTran2" Date/Time run: 03/27/05 14:00:35 [ C:\My Documents\ClassWork\@ESE216\PSpiceSimulations\nmoschar-schemati... Temperature: 27.0 (A) nmoschar-SCHEMATIC1-DCTran2.dat (active) 2.0mA Saturation 1.5mA Vgs=3V Triode 2.8 2.6 1.0mA 2.4 2.2 2.0 0.5mA 1.8 1.6 1.0 0A 0V ID(M1) Date: March 27, 2005 2V 4V 6V V_V2 Page 1 8V 1.4 1.2 10V Time: 14:07:04