AN2760

... In the STCD10x0 chip design, there are ESD diodes for the EN pins to connect to VCC and GND for ESD protection. If VCC is powered down (disconnect to supply) and an active high signal is present on the EN pin (for example, 2.8 V), the ESD diode which connects the EN pin to VCC will conduct and pull ...

... In the STCD10x0 chip design, there are ESD diodes for the EN pins to connect to VCC and GND for ESD protection. If VCC is powered down (disconnect to supply) and an active high signal is present on the EN pin (for example, 2.8 V), the ESD diode which connects the EN pin to VCC will conduct and pull ...

Electronic Circuits – EE359A

... Figure 11.7 A simple implementation of the D flip-flop. The circuit in (a) utilizes the two-phase nonoverlapping clock whose waveforms are shown in (b). ...

... Figure 11.7 A simple implementation of the D flip-flop. The circuit in (a) utilizes the two-phase nonoverlapping clock whose waveforms are shown in (b). ...

MAX1488E ±15kV ESD-Protected, Quad, Low-Power RS-232 Line Driver _______________General Description

... Machine Model The Machine Model for ESD testing uses a 200pF storage capacitor and zero-discharge resistance. Its objective is to mimic the stress caused by contact that occurs with handling and assembly during manufacturing. Of course, all pins (not just RS-232 inputs and outputs) require this prot ...

... Machine Model The Machine Model for ESD testing uses a 200pF storage capacitor and zero-discharge resistance. Its objective is to mimic the stress caused by contact that occurs with handling and assembly during manufacturing. Of course, all pins (not just RS-232 inputs and outputs) require this prot ...

ARM-based Flash MCU SAM G51 Series Description SUMMARY DATASHEET

... UARTs, two TWIs, one high-speed TWI, up to two SPIs, one three-channel generalpurpose 16-bit timer, one RTT and one 8-channel 12-bit ADC. The SAM G51 series is a general-purpose microcontroller with the best ratio in terms of reduced power consumption, processing power and optimized peripheral set. ...

... UARTs, two TWIs, one high-speed TWI, up to two SPIs, one three-channel generalpurpose 16-bit timer, one RTT and one 8-channel 12-bit ADC. The SAM G51 series is a general-purpose microcontroller with the best ratio in terms of reduced power consumption, processing power and optimized peripheral set. ...

Low voltage CMOS single inverter with 5V tolerant input

... Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implicatio ...

... Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implicatio ...

EECS150 - Digital Design Lecture 1

... 3. Changes in the signals correspond to changes in clock signal (but don’t change every cycle). ...

... 3. Changes in the signals correspond to changes in clock signal (but don’t change every cycle). ...

Timing at ALBA, Jairo Moldes/Ramón Suñe

... Output Input Output Input Output Input Output Input Output Input ...

... Output Input Output Input Output Input Output Input Output Input ...

ADuM1100 数据手册DataSheet下载

... Inc. iCoupler® technology. Combining high speed CMOS and monolithic air core transformer technology, this isolation component provides outstanding performance characteristics superior to alternatives, such as optocoupler devices. ...

... Inc. iCoupler® technology. Combining high speed CMOS and monolithic air core transformer technology, this isolation component provides outstanding performance characteristics superior to alternatives, such as optocoupler devices. ...

High-Speed, Single-Supply, Rail-to-Rail

... OPA353 series extends 100mV beyond the supply rails. This is achieved with a complementary input stage—an N-channel input differential pair in parallel with a P-channel differential pair (see Figure 2). The N-channel pair is active for input voltages close to the positive rail, typically (V+) – 1.8V ...

... OPA353 series extends 100mV beyond the supply rails. This is achieved with a complementary input stage—an N-channel input differential pair in parallel with a P-channel differential pair (see Figure 2). The N-channel pair is active for input voltages close to the positive rail, typically (V+) – 1.8V ...

HMC854LC5

... broadband operation. All clock and data inputs to the HMC854LC5 are CML and terminated on-chip with 50 Ohms to the positive supply, GND, and may be DC or AC coupled. The differential outputs are source terminated to 50 Ohms and may also be AC or DC coupled. Outputs can be connected directly to a 50 ...

... broadband operation. All clock and data inputs to the HMC854LC5 are CML and terminated on-chip with 50 Ohms to the positive supply, GND, and may be DC or AC coupled. The differential outputs are source terminated to 50 Ohms and may also be AC or DC coupled. Outputs can be connected directly to a 50 ...

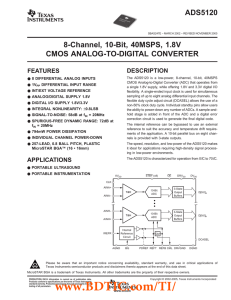

ADS5120 数据资料 dataSheet 下载

... +1.8V single supply. For additional interfacing flexibility, the digital I/O supply (DRVDD) can be set to either +1.8V or +3.3V. The ADC core of each channel consists of 10 pipeline stages. Each of the 10 stages produces one digital bit per stage. Both the rising and the falling clock edges are util ...

... +1.8V single supply. For additional interfacing flexibility, the digital I/O supply (DRVDD) can be set to either +1.8V or +3.3V. The ADC core of each channel consists of 10 pipeline stages. Each of the 10 stages produces one digital bit per stage. Both the rising and the falling clock edges are util ...

Zero Drift, Unidirectional Current Shunt Monitor AD8219

... OUT = (R4/R1) × (V1 − V2) Resistors R4 and R1 are matched to within 0.01% and have values of 1.5 MΩ and 25 kΩ, respectively, meaning an input to output total gain of 60 V/V for the AD8219, while the difference at V1 and V2 is the voltage across the shunt resistor or VIN. Therefore, the input-to-outp ...

... OUT = (R4/R1) × (V1 − V2) Resistors R4 and R1 are matched to within 0.01% and have values of 1.5 MΩ and 25 kΩ, respectively, meaning an input to output total gain of 60 V/V for the AD8219, while the difference at V1 and V2 is the voltage across the shunt resistor or VIN. Therefore, the input-to-outp ...

ADS8345 数据资料 dataSheet 下载

... The basic operation of the ADS8345 is shown in Figure 1. The device requires an external reference and an external clock. It operates from a single supply of 2.7V to 5.25V. The external reference can be any voltage between 500mV and +VCC/2. The value of the reference voltage directly sets the input ...

... The basic operation of the ADS8345 is shown in Figure 1. The device requires an external reference and an external clock. It operates from a single supply of 2.7V to 5.25V. The external reference can be any voltage between 500mV and +VCC/2. The value of the reference voltage directly sets the input ...

MAX1730 50mA Regulated Step-Down Charge Pump for 1.8V or 1.9V Logic General Description

... In the MAX1730, pulse-skipping PFM mode pauses the oscillator when the output is in regulation. Using the 2:1 charge-pump configuration as an example, when the output is set to half the input, the switching frequency is near the oscillator frequency. However, for outputs below half the input, switch ...

... In the MAX1730, pulse-skipping PFM mode pauses the oscillator when the output is in regulation. Using the 2:1 charge-pump configuration as an example, when the output is set to half the input, the switching frequency is near the oscillator frequency. However, for outputs below half the input, switch ...

74LCX760 Low Voltage Buffer/Line Driver 7

... 74LCX760 Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Open Drain Outputs ...

... 74LCX760 Low Voltage Buffer/Line Driver with 5V Tolerant Inputs and Open Drain Outputs ...

JEDEC STANDARD

... The third clause specifies the minimum required output characteristics of, and ac test conditions for, compliant outputs targeted for various application environments. The fourth clause specifies requirements for differential signaling. The full input reference level (VREF) range specified is requir ...

... The third clause specifies the minimum required output characteristics of, and ac test conditions for, compliant outputs targeted for various application environments. The fourth clause specifies requirements for differential signaling. The full input reference level (VREF) range specified is requir ...

Evaluates: MAX1774 MAX1774 Evaluation Kit General Description Features

... The MAX1774 EV kit features several jumper-selectable options. Shutdown mode jumpers that reduce the MAX1774 shutdown current to less than 8µA (typ) are provided for the main and core outputs. Power to the core input can be fed from the main output (VMAIN) or an external voltage source. The availabl ...

... The MAX1774 EV kit features several jumper-selectable options. Shutdown mode jumpers that reduce the MAX1774 shutdown current to less than 8µA (typ) are provided for the main and core outputs. Power to the core input can be fed from the main output (VMAIN) or an external voltage source. The availabl ...

Time Delay Relays – Application Data

... • opening or closing of a trigger signal (Off Delay, Single Shot & Watchdog). These trigger signals can be one of two designs: • a control switch (dry contact), i.e., limit switch, push button, float switch, etc. • voltage (commonly known as a power trigger). To help understand, some definitions are ...

... • opening or closing of a trigger signal (Off Delay, Single Shot & Watchdog). These trigger signals can be one of two designs: • a control switch (dry contact), i.e., limit switch, push button, float switch, etc. • voltage (commonly known as a power trigger). To help understand, some definitions are ...

DS92LV1212A 16-40MHz 10-Bit Bus LVDS Random Lck

... Low-High transition takes place in a clock cycle over multiple cycles. This occurs when any bit, except DIN 9, is held at a low state and the adjacent bit is held high, creating a 0-1 transition. In the worst case, the Deserializer could become locked to the data pattern rather than the clock. Circu ...

... Low-High transition takes place in a clock cycle over multiple cycles. This occurs when any bit, except DIN 9, is held at a low state and the adjacent bit is held high, creating a 0-1 transition. In the worst case, the Deserializer could become locked to the data pattern rather than the clock. Circu ...

MAX5166 32-Channel Sample/Hold Amplifier with Four Multiplexed Inputs General Description

... Figure 5 shows a typical demultiplexer application. Different digital codes are converted by the digital-toanalog converter (DAC) and then stored on eight different channels, or as many as 32 different channels when all four inputs are active. The 100mV/sec (max) droop rate requires refreshing the h ...

... Figure 5 shows a typical demultiplexer application. Different digital codes are converted by the digital-toanalog converter (DAC) and then stored on eight different channels, or as many as 32 different channels when all four inputs are active. The 100mV/sec (max) droop rate requires refreshing the h ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.