AD7653 - Analog Devices

... The AD7653 is a 16-bit, 1 MSPS, charge redistribution SAR analog-to-digital converter that operates from a single 5 V power supply. The part contains a high speed 16-bit sampling ADC, internal conversion clock, internal reference, error correction circuits, and both serial and parallel system interf ...

... The AD7653 is a 16-bit, 1 MSPS, charge redistribution SAR analog-to-digital converter that operates from a single 5 V power supply. The part contains a high speed 16-bit sampling ADC, internal conversion clock, internal reference, error correction circuits, and both serial and parallel system interf ...

LT5517 - 40MHz to 900MHz Quadrature Demodulator.

... L-C circuits to produce the required balanced waveforms at the RF+ and RF– inputs using three discrete elements as shown in Figure 5. Nominal values are listed in Table 1. (In practice, these values should be compensated according to the parasitics of the PCB.) The conversion gain and NF ...

... L-C circuits to produce the required balanced waveforms at the RF+ and RF– inputs using three discrete elements as shown in Figure 5. Nominal values are listed in Table 1. (In practice, these values should be compensated according to the parasitics of the PCB.) The conversion gain and NF ...

1-Gbps to 4.25-Gbps Rate-Selectable Limiting

... This device provides a gain of about 43 dB, which ensures a fully differential output swing for input signals as low as 5 mVp-p. The ONET4291PA provides loss-of-signal detection with either digital or analog threshold adjust. The part is available in a small-footprint, 4-mm × 4-mm, 16-terminal QFN p ...

... This device provides a gain of about 43 dB, which ensures a fully differential output swing for input signals as low as 5 mVp-p. The ONET4291PA provides loss-of-signal detection with either digital or analog threshold adjust. The part is available in a small-footprint, 4-mm × 4-mm, 16-terminal QFN p ...

MAX9169/MAX9170 4-Port LVDS and LVTTL-to-LVDS Repeaters General Description Features

... recovery or serializers and deserializers. The highspeed switching performance guarantees 630Mbps data rate and less than 120ps channel-to-channel skew over the 3.0V to 3.6V operating supply range. Supply current is 30mA (max) for the MAX9169, and 25mA (max) for the MAX9170. LVDS inputs and outputs ...

... recovery or serializers and deserializers. The highspeed switching performance guarantees 630Mbps data rate and less than 120ps channel-to-channel skew over the 3.0V to 3.6V operating supply range. Supply current is 30mA (max) for the MAX9169, and 25mA (max) for the MAX9170. LVDS inputs and outputs ...

MAX2205–MAX2208 RF Power Detectors in UCSP General Description Features

... detector goes to an op amp in an analog GSM powercontrol scheme, or to an ADC in other systems such as TDMA or discrete-time GSM power control. The MAX2205 has high-input impedance for use with high-value resistive tapping from a CDMA power amplifier. This coupling method is the lowest cost and lowe ...

... detector goes to an op amp in an analog GSM powercontrol scheme, or to an ADC in other systems such as TDMA or discrete-time GSM power control. The MAX2205 has high-input impedance for use with high-value resistive tapping from a CDMA power amplifier. This coupling method is the lowest cost and lowe ...

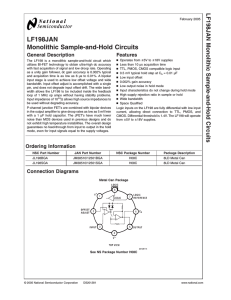

LF198JAN Monolithic Sample-and-Hold Circuits Monolithic General Description

... confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actuality, there are finite phase delays through the circuit creat ...

... confusion among sample-and-hold users than any other parameter. The primary reason for this is that many users make the assumption that the sample and hold amplifier is truly locked on to the input signal while in the sample mode. In actuality, there are finite phase delays through the circuit creat ...

TLV906x 10-MHz, RRIO, CMOS Operational

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absol ...

... Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absol ...

MAX1179/MAX1187/MAX1189 16-Bit, 135ksps, Single-Supply ADCs with Bipolar Analog Input Range General Description

... The MAX1179/MAX1187/MAX1189 16-bit, low-power, successive-approximation analog-to-digital converters (ADCs) feature automatic power-down, a factorytrimmed internal clock, and a 16-bit wide parallel interface. The devices operate from a single +4.75V to +5.25V analog supply and feature a separate dig ...

... The MAX1179/MAX1187/MAX1189 16-bit, low-power, successive-approximation analog-to-digital converters (ADCs) feature automatic power-down, a factorytrimmed internal clock, and a 16-bit wide parallel interface. The devices operate from a single +4.75V to +5.25V analog supply and feature a separate dig ...

TL3016 数据资料 dataSheet 下载

... Supply voltage, VDD (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 7 V to 7 V Differential input voltage, VID (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

... Supply voltage, VDD (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . – 7 V to 7 V Differential input voltage, VID (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

A 10-BIT 1.2-GS/s NYQUIST CURRENT

... unsynchronized digital input is fed in from the left and the cascode current source and the current switch are shown on the right. The capacitive coupling to the analog output is minimized by limiting the amplitude of the control signals just high enough to switch the tail current completely to the ...

... unsynchronized digital input is fed in from the left and the cascode current source and the current switch are shown on the right. The capacitive coupling to the analog output is minimized by limiting the amplitude of the control signals just high enough to switch the tail current completely to the ...

PDF (Publisher`s version)

... normalizing oscillator phase noise or filter SNR to power. In [7], DTG FFs (DTG-FFs) were used and able to achieve very low phase errors at much lower power consumption than CML. Explorative simulations in [10] confirmed that DTGFFs have significant advantages over CML FFs (CML-FFs) for MPCG. Howeve ...

... normalizing oscillator phase noise or filter SNR to power. In [7], DTG FFs (DTG-FFs) were used and able to achieve very low phase errors at much lower power consumption than CML. Explorative simulations in [10] confirmed that DTGFFs have significant advantages over CML FFs (CML-FFs) for MPCG. Howeve ...

MAX1446 10-Bit, 60Msps, 3.0V, Low-Power ADC with Internal Reference General Description

... (ADC) features a fully differential input, a pipelined 10stage ADC architecture with digital error correction and wideband track and hold (T/H) incorporating a fully differential signal path. This ADC is optimized for lowpower, high dynamic performance applications in imaging and digital communicati ...

... (ADC) features a fully differential input, a pipelined 10stage ADC architecture with digital error correction and wideband track and hold (T/H) incorporating a fully differential signal path. This ADC is optimized for lowpower, high dynamic performance applications in imaging and digital communicati ...

A Single-ended Simultaneous Bidirectional Transceiver in 65

... are all set to “0” and the backward comma detection block sets FLAG to “1” if DRX is “1” at least once. For the case shown in Fig. 10(a), the flag bits FLAG<1:8> are “1” and the flag bits FLAG<0, 9:19> are “0”. Then, we can know that the rising edge of the input signal DQSRC lies between the r ...

... are all set to “0” and the backward comma detection block sets FLAG to “1” if DRX is “1” at least once. For the case shown in Fig. 10(a), the flag bits FLAG<1:8> are “1” and the flag bits FLAG<0, 9:19> are “0”. Then, we can know that the rising edge of the input signal DQSRC lies between the r ...

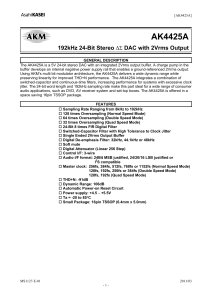

AK4425 English Datasheet - Asahi Kasei Microdevices

... are two methods to set MCLK frequency. In Manual Setting Mode (ACKS = “0”: Register 00H), the sampling speed is set by DFS0/1 (Table 1). The frequency of MCLK at each sampling speed is set automatically. (Table 2) When the power applied, the AK4425A is in Auto Setting Mode. In Auto Setting Mode (ACK ...

... are two methods to set MCLK frequency. In Manual Setting Mode (ACKS = “0”: Register 00H), the sampling speed is set by DFS0/1 (Table 1). The frequency of MCLK at each sampling speed is set automatically. (Table 2) When the power applied, the AK4425A is in Auto Setting Mode. In Auto Setting Mode (ACK ...

EiceDRIVER™ 1EDI Compact Family

... Using the IN+ pin as enable signal leaves the IN- to control the output PWM with an inverted logic input signal. The enable signal can be shared between gate driver ICs of a complete inverter to start operation with a single control signal. C) Shutdown Using the IN- pin as shutdown signal leaves the ...

... Using the IN+ pin as enable signal leaves the IN- to control the output PWM with an inverted logic input signal. The enable signal can be shared between gate driver ICs of a complete inverter to start operation with a single control signal. C) Shutdown Using the IN- pin as shutdown signal leaves the ...

View datasheet

... synchronized. If a status word is read, the terminal will be reset. In “external synchronous mode, “this is an input terminal. A “High” on this input forces the MSM82C51A-2 to start receiving data characters. In “asynchronous mode,” this is an output terminal which generates “high level”output upon ...

... synchronized. If a status word is read, the terminal will be reset. In “external synchronous mode, “this is an input terminal. A “High” on this input forces the MSM82C51A-2 to start receiving data characters. In “asynchronous mode,” this is an output terminal which generates “high level”output upon ...

LT1260 - Low Cost Dual and Triple 130MHz Current Feedback Amplifiers with Shutdown

... The LT1259/LT1260 will operate from single or split supplies from ±2V (4V total) to ±15V (30V total). It is not necessary to use equal value split supplies, however the offset voltage and inverting input bias current will change. The offset voltage changes about 500µV per volt of supply mismatch. Th ...

... The LT1259/LT1260 will operate from single or split supplies from ±2V (4V total) to ±15V (30V total). It is not necessary to use equal value split supplies, however the offset voltage and inverting input bias current will change. The offset voltage changes about 500µV per volt of supply mismatch. Th ...

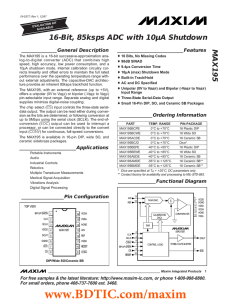

MAX195 16-Bit, 85ksps ADC with 10µA Shutdown _______________General Description ____________________________Features

... period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low only while CLK is low (Figure 5 ...

... period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low only while CLK is low (Figure 5 ...

A Microcontroller System for Experimentation

... The PIC’s instruction set is refreshingly small and simple. Instructions consist of 14 bits and are divided into 4 classes as shown in Fig.2. The byte-oriented instructions operate on the W-register (accumulator) and the addressed byte in memory, and they store the result either in the same memory l ...

... The PIC’s instruction set is refreshingly small and simple. Instructions consist of 14 bits and are divided into 4 classes as shown in Fig.2. The byte-oriented instructions operate on the W-register (accumulator) and the addressed byte in memory, and they store the result either in the same memory l ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.