DEVELOPMENT OF AN AUDIO EVOKED RESPONSE SYSTEM TO FACILITATE ANAESTHESIA MONITORING

... from the neuro-muscular system of a human or other animal when a stimulus is presented at a suitable point. 17 It is distinct from the spontaneous potentials as detected by normal EEG or voluntary EMG (Electromyography- which is a technique for evaluating and recording the activation signal of muscl ...

... from the neuro-muscular system of a human or other animal when a stimulus is presented at a suitable point. 17 It is distinct from the spontaneous potentials as detected by normal EEG or voluntary EMG (Electromyography- which is a technique for evaluating and recording the activation signal of muscl ...

Engineer-to-Engineer Note EE-281

... Copyright 2008, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers’ products or for any infringements of patents or rights of others which may result from Analog Devices’ assistance. All trademarks and ...

... Copyright 2008, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers’ products or for any infringements of patents or rights of others which may result from Analog Devices’ assistance. All trademarks and ...

ADM488 数据手册DataSheet 下载

... Receiver Output Enable. A low level enables the receiver output, RO. A high level places it in a high impedance state. Driver Output Enable. A high level enables the driver differential outputs, Y and Z. A low level places it in a high impedance state. Driver Input. When the driver is enabled, a log ...

... Receiver Output Enable. A low level enables the receiver output, RO. A high level places it in a high impedance state. Driver Output Enable. A high level enables the driver differential outputs, Y and Z. A low level places it in a high impedance state. Driver Input. When the driver is enabled, a log ...

LMC6462 Dual/LMC6464 Quad Micropower, Rail-to

... It is generally recognized that any circuit which must operate with less than 1000 pA of leakage current requires special layout of the PC board. When one wishes to take advantage of the ultra-low input current of the LMC6462/4, typically 150 fA, it is essential to have an excellent layout. Fortunat ...

... It is generally recognized that any circuit which must operate with less than 1000 pA of leakage current requires special layout of the PC board. When one wishes to take advantage of the ultra-low input current of the LMC6462/4, typically 150 fA, it is essential to have an excellent layout. Fortunat ...

ADC108S102 8-Channel, 500 kSPS to 1 MSPS, 10

... CROSSTALK is the coupling of energy from one channel into another channel. This is similar to Channel-toChannel Isolation, except for the sign of the data. DIFFERENTIAL NON-LINEARITY (DNL) is the measure of the maximum deviation from the ideal step size of 1 LSB. DUTY CYCLE is the ratio of the time ...

... CROSSTALK is the coupling of energy from one channel into another channel. This is similar to Channel-toChannel Isolation, except for the sign of the data. DIFFERENTIAL NON-LINEARITY (DNL) is the measure of the maximum deviation from the ideal step size of 1 LSB. DUTY CYCLE is the ratio of the time ...

MAX3314E ±15kV ESD-Protected, 460kbps, 1µA, RS-232-Compatible Transceiver General Description

... The MAX3314E driver outputs and receiver inputs have extra protection against static discharge. Maxim’s engineers have developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and ...

... The MAX3314E driver outputs and receiver inputs have extra protection against static discharge. Maxim’s engineers have developed state-of-the-art structures to protect these pins against ESD of ±15kV without damage. The ESD structures withstand high ESD in all states: normal operation, shutdown, and ...

IX Gamma-Gamma Angular Correlation

... Adjust the voltage to approximately 1300 volts. Note that it may be necessary to lower this to 1200 V in order not to exceed the 1.4 V output limit of the linear fan-out when looking at the 60Co source. DO NOT EXCEED 1500 V. Turn the switch to on. Make sure the power supply has been on for at least ...

... Adjust the voltage to approximately 1300 volts. Note that it may be necessary to lower this to 1200 V in order not to exceed the 1.4 V output limit of the linear fan-out when looking at the 60Co source. DO NOT EXCEED 1500 V. Turn the switch to on. Make sure the power supply has been on for at least ...

74ABT244 - Nexperia

... 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated condition ...

... 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated condition ...

MAX9152 800Mbps LVDS/LVPECL-to-LVDS 2 x 2 Crosspoint Switch General Description

... intended for point-to-point communication over a controlled impedance medium as defined by the ANSI TIA/EIA-644 and IEEE 1596.3 standards. LVDS uses a lower voltage swing than other common communication standards, achieving higher data rates with reduced power consumption while reducing EMI emission ...

... intended for point-to-point communication over a controlled impedance medium as defined by the ANSI TIA/EIA-644 and IEEE 1596.3 standards. LVDS uses a lower voltage swing than other common communication standards, achieving higher data rates with reduced power consumption while reducing EMI emission ...

DS91M040 125 MHz Quad M-LVDS Transceiver DS91M040 FEATURES DESCRIPTION

... specifically designed for multipoint and multidrop cable and backplane applications. It differs from standard LVDS in providing increased drive current to handle double terminations that are required in multipoint applications. Controlled transition times minimize reflections that are common in mult ...

... specifically designed for multipoint and multidrop cable and backplane applications. It differs from standard LVDS in providing increased drive current to handle double terminations that are required in multipoint applications. Controlled transition times minimize reflections that are common in mult ...

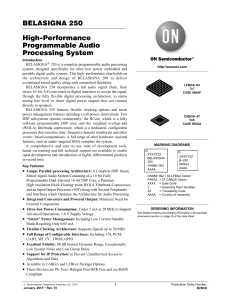

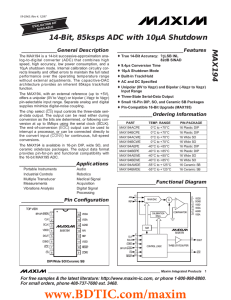

MAX194 14-Bit, 85ksps ADC with 10µA Shutdown _______________General Description ____________________________Features

... your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low only while CLK is low (Figure 5). Ensure that the maximum propagation delay through the gate is less th ...

... your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start signal with the conversion clock so that CONV can go low only while CLK is low (Figure 5). Ensure that the maximum propagation delay through the gate is less th ...

PROCESS CALIBRATOR TechChek™ Model 820

... Lighten your load by taking the TechChek to every site. It’s like bringing a cartload of test equipment from the shop to the control room or the field. The TechChek 820 sources & reads DC like a milliamp or voltage calibrator, simulates and measures T/Cs & RTDs like a temperature calibrator and gene ...

... Lighten your load by taking the TechChek to every site. It’s like bringing a cartload of test equipment from the shop to the control room or the field. The TechChek 820 sources & reads DC like a milliamp or voltage calibrator, simulates and measures T/Cs & RTDs like a temperature calibrator and gene ...

LT5570 - Fast Responding, 40MHz to 2.7GHz Mean-Squared Power Detector.

... OUT (Pin 6): DC Output Pin. The output impedance is mainly determined by an internal 100Ω series resistance that provides output circuit protection if the output is shorted to ground. DNC (Pins 7, 8): Do Not Connect. Don’t connect any external component at these pins. Avoid a long wire or metal trac ...

... OUT (Pin 6): DC Output Pin. The output impedance is mainly determined by an internal 100Ω series resistance that provides output circuit protection if the output is shorted to ground. DNC (Pins 7, 8): Do Not Connect. Don’t connect any external component at these pins. Avoid a long wire or metal trac ...

High-Speed Digital Logic

... • do not use the built-in XOR gate found in the GigaBit Logic shift register • tie unused CMOS and TTL input high or low, do not let them float – floating ECL and GaAs inputs are interpreted as logical LO – grounded input interpreted as logical HI with ECL and GaAs ...

... • do not use the built-in XOR gate found in the GigaBit Logic shift register • tie unused CMOS and TTL input high or low, do not let them float – floating ECL and GaAs inputs are interpreted as logical LO – grounded input interpreted as logical HI with ECL and GaAs ...

file (7.8 MB, pdf)

... • The parallel R-C circuit time constant is typically 100 times the time period corresponding to the minimum frequency of operation. • The R-C time constant also controls the response time. • Slew rate is the primary specification that needs to be looked into while choosing the right opamp for the c ...

... • The parallel R-C circuit time constant is typically 100 times the time period corresponding to the minimum frequency of operation. • The R-C time constant also controls the response time. • Slew rate is the primary specification that needs to be looked into while choosing the right opamp for the c ...

The UC1901 Simplifies the Problem of Isolated

... one-to-one will be required for the coupling transformer if the detector output must exceed approximately 1V, (allowing for a detector diode drop of 0.6V). It should be noted that many switching power supplies now being designed include an integrated PWM control IC. A typical PWM IC includes a dedic ...

... one-to-one will be required for the coupling transformer if the detector output must exceed approximately 1V, (allowing for a detector diode drop of 0.6V). It should be noted that many switching power supplies now being designed include an integrated PWM control IC. A typical PWM IC includes a dedic ...

MAX5886 3.3V, 12-Bit, 500Msps High Dynamic Performance DAC with Differential LVDS Inputs

... The MAX5886 is a high-performance, 12-bit, currentsteering DAC (Figure 1) capable of operating with clock speeds up to 500MHz. The converter consists of separate input and DAC registers, followed by a currentsteering circuit. This circuit is capable of generating differential full-scale currents in ...

... The MAX5886 is a high-performance, 12-bit, currentsteering DAC (Figure 1) capable of operating with clock speeds up to 500MHz. The converter consists of separate input and DAC registers, followed by a currentsteering circuit. This circuit is capable of generating differential full-scale currents in ...

74LCX573 Low Voltage Octal Latch with 5V Tolerant Inputs and Outputs

... output buffers. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW the latches store the information that was present on the D inputs a ...

... output buffers. When the Latch Enable (LE) input is HIGH, data on the Dn inputs enters the latches. In this condition the latches are transparent, i.e., a latch output will change state each time its D input changes. When LE is LOW the latches store the information that was present on the D inputs a ...

MAX3676 622Mbps, 3.3V Clock-Recovery and Data-Retiming IC with Limiting Amplifier General Description

... The frequency detector incorporated into the PLL uses the input data stream edges to sample the quadrature components of the VCO clock. This generates a difference frequency that aids acquisition during startup. Depending on the polarity of the difference frequency, the PFD drives the VCO so that th ...

... The frequency detector incorporated into the PLL uses the input data stream edges to sample the quadrature components of the VCO clock. This generates a difference frequency that aids acquisition during startup. Depending on the polarity of the difference frequency, the PFD drives the VCO so that th ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.