Control of G4JNT AD9850 Direct Digital Synthesizer module

... There is one wire link that needs to be installed on the board. This is the input to the internal comparator, Pin 16, on the AD9850 that is used to generate a square wave output from the filtered sine wave. If this function is wanted, connect a thin insulated wire from the pad adjacent to pin 16 to ...

... There is one wire link that needs to be installed on the board. This is the input to the internal comparator, Pin 16, on the AD9850 that is used to generate a square wave output from the filtered sine wave. If this function is wanted, connect a thin insulated wire from the pad adjacent to pin 16 to ...

MAX9392/MAX9393 Anything-to-LVDS Dual 2 x 2 Crosspoint Switches General Description

... ♦ LVDS Outputs for Clock or High-Speed Data ...

... ♦ LVDS Outputs for Clock or High-Speed Data ...

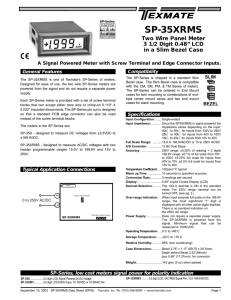

SP-35XRMS Two Wire Panel Meter 3 1/2 Digit 0.48” LCD

... General Features The SP-35XRMS is one of Texmate's SP-Series of meters. Designed for ease of use, the two wire SP-Series meters are powered from the signal and do not require a separate power supply. Each SP-Series meter is provided with a set of screw terminal blocks that can accept either bare wir ...

... General Features The SP-35XRMS is one of Texmate's SP-Series of meters. Designed for ease of use, the two wire SP-Series meters are powered from the signal and do not require a separate power supply. Each SP-Series meter is provided with a set of screw terminal blocks that can accept either bare wir ...

AD8195 数据手册DataSheet 下载

... encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Temporarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of 175°C for an ...

... encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Temporarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of 175°C for an ...

AnyVolt - Dimension Engineering

... When either of the input or output current limits of 2A have been exceeded, the AnyVolt’s voltage regulation controller will shut off and the output voltage will drop to zero. The AnyVolt will remain in shut-down mode for 1-2 seconds. During this time “OC” (overcurrent) will be displayed. It will th ...

... When either of the input or output current limits of 2A have been exceeded, the AnyVolt’s voltage regulation controller will shut off and the output voltage will drop to zero. The AnyVolt will remain in shut-down mode for 1-2 seconds. During this time “OC” (overcurrent) will be displayed. It will th ...

MAX9180 400Mbps, Low-Jitter, Low-Noise LVDS Repeater in an SC70 Package General Description

... the bus. The point-to-point connection between the MAX9180 output and the destination IC, such as an FPGA or ASIC, allows the destination IC to be located at greater distances from the bus connector. Ultra-low, 23ps P-P added deterministic jitter and 0.6psRMS added random jitter ensure reliable comm ...

... the bus. The point-to-point connection between the MAX9180 output and the destination IC, such as an FPGA or ASIC, allows the destination IC to be located at greater distances from the bus connector. Ultra-low, 23ps P-P added deterministic jitter and 0.6psRMS added random jitter ensure reliable comm ...

TLC7225 数据资料 dataSheet 下载

... The TLC7225 consists of four 8-bit voltage-output digital-to-analog converters (DACs), with output buffer amplifiers and interface logic with double register-buffering. Separate on-chip latches are provided for each of the DACs. Data is transferred into one of these data latches through a common 8-b ...

... The TLC7225 consists of four 8-bit voltage-output digital-to-analog converters (DACs), with output buffer amplifiers and interface logic with double register-buffering. Separate on-chip latches are provided for each of the DACs. Data is transferred into one of these data latches through a common 8-b ...

MAX3322E/MAX3323E ±15kV ESD-Protected, RS-232 Transceivers for Multidrop Applications General Description

... The MAX3322E/MAX3323E are RS-232 transceivers for multidrop applications (i.e., multiple-receiver operation). The devices are pin selectable between standard RS-232 operation with 5kΩ input resistance receivers or highinput-impedance receivers. Receivers of the MAX3322E/ MAX3323E remain active in bo ...

... The MAX3322E/MAX3323E are RS-232 transceivers for multidrop applications (i.e., multiple-receiver operation). The devices are pin selectable between standard RS-232 operation with 5kΩ input resistance receivers or highinput-impedance receivers. Receivers of the MAX3322E/ MAX3323E remain active in bo ...

nemic lambda

... of DC isolation tester must be done before the test. Ensure that the unit is fully discharged after the test. (a) Output ~ FG (chassis) : 500VDC, 100MΩ or more ...

... of DC isolation tester must be done before the test. Ensure that the unit is fully discharged after the test. (a) Output ~ FG (chassis) : 500VDC, 100MΩ or more ...

Chapter 11 ASK Modulator

... balanced modulator. The carrier signal and data signal are single-ended input. The carrier signal is inputted at pin 10 and the data signal is inputted at pin 1. R 13 and R 14 determine the gain and the bias current of this circuit, respe ctively. If we adjust VR 1 or the data signal amplitude, it c ...

... balanced modulator. The carrier signal and data signal are single-ended input. The carrier signal is inputted at pin 10 and the data signal is inputted at pin 1. R 13 and R 14 determine the gain and the bias current of this circuit, respe ctively. If we adjust VR 1 or the data signal amplitude, it c ...

Lecture 1_F12

... Timer 1 and Output Compare • The AVR has two output compares (OCR1A/B) – OCR1A/B are 16-bit registers – When the value of OCR1A/OCR1B matches that of Timer1: • A user-defined action can take place on the OC1A/OC1B pin (set/clear/inv) i.e.,(OC1A )PD5 / (OC1B) PD4 need to set as output • An interrupt ...

... Timer 1 and Output Compare • The AVR has two output compares (OCR1A/B) – OCR1A/B are 16-bit registers – When the value of OCR1A/OCR1B matches that of Timer1: • A user-defined action can take place on the OC1A/OC1B pin (set/clear/inv) i.e.,(OC1A )PD5 / (OC1B) PD4 need to set as output • An interrupt ...

DAC

... Settling Time: The time required for the voltage to settle within +/the voltage associated with the VLSB. Any change in the input time will not be reflected immediately due to the lag time. Overshoot: occurs when the output voltage overshoots the desired analog output voltage. ...

... Settling Time: The time required for the voltage to settle within +/the voltage associated with the VLSB. Any change in the input time will not be reflected immediately due to the lag time. Overshoot: occurs when the output voltage overshoots the desired analog output voltage. ...

Single/Dual/Quad, Ultra-High-Speed, +3V/+5V, Beyond-the-Rails Comparators MAX961–MAX964/MAX997/MAX999 _________________General Description

... The MAX961–MAX964/MAX997/MAX999 are low-power, ultra-high-speed comparators with internal hysteresis. These devices are optimized for single +3V or +5V operation. The input common-mode range extends 100mV Beyond-the-Rails™, and the outputs can sink or source 4mA to within 0.52V of GND and V CC . Pro ...

... The MAX961–MAX964/MAX997/MAX999 are low-power, ultra-high-speed comparators with internal hysteresis. These devices are optimized for single +3V or +5V operation. The input common-mode range extends 100mV Beyond-the-Rails™, and the outputs can sink or source 4mA to within 0.52V of GND and V CC . Pro ...

Bus-Hold Circuit - Texas Instruments

... Furthermore, CMOS device data sheets recommend the slowest possible rise time for the input signal to ensure optimum functioning of components. However, slowly rising edges cause fast integrated circuits to malfunction and can, in extreme cases, lead to destruction of the circuit. Figure 3 shows an ...

... Furthermore, CMOS device data sheets recommend the slowest possible rise time for the input signal to ensure optimum functioning of components. However, slowly rising edges cause fast integrated circuits to malfunction and can, in extreme cases, lead to destruction of the circuit. Figure 3 shows an ...

Single/Dual/Quad, Ultra-High-Speed, +3V/+5V, Beyond-the

... The MAX961–MAX964/MAX997/MAX999 are low-power, ultra-high-speed comparators with internal hysteresis. These devices are optimized for single +3V or +5V operation. The input common-mode range extends 100mV Beyond-the-Rails™, and the outputs can sink or source 4mA to within 0.52V of GND and V CC . Pro ...

... The MAX961–MAX964/MAX997/MAX999 are low-power, ultra-high-speed comparators with internal hysteresis. These devices are optimized for single +3V or +5V operation. The input common-mode range extends 100mV Beyond-the-Rails™, and the outputs can sink or source 4mA to within 0.52V of GND and V CC . Pro ...

12 GHz - Electrocomponents

... The HMC363S8G & HMC363S8GE are low noise Divide-by-8 Static Dividers with InGaP GaAs HBT technology in 8 lead surface mount plastic packages. This device operates from DC (with a square wave input) to 12 GHz input frequency with a single +5V DC supply. The low additive SSB phase noise of -153 dBc/Hz ...

... The HMC363S8G & HMC363S8GE are low noise Divide-by-8 Static Dividers with InGaP GaAs HBT technology in 8 lead surface mount plastic packages. This device operates from DC (with a square wave input) to 12 GHz input frequency with a single +5V DC supply. The low additive SSB phase noise of -153 dBc/Hz ...

LT5570 - Linear Technology

... OUT (Pin 6): DC Output Pin. The output impedance is mainly determined by an internal 100Ω series resistance that provides output circuit protection if the output is shorted to ground. DNC (Pins 7, 8): Do Not Connect. Don’t connect any external component at these pins. Avoid a long wire or metal trac ...

... OUT (Pin 6): DC Output Pin. The output impedance is mainly determined by an internal 100Ω series resistance that provides output circuit protection if the output is shorted to ground. DNC (Pins 7, 8): Do Not Connect. Don’t connect any external component at these pins. Avoid a long wire or metal trac ...

An ultimatic adapter for iambic keyers

... 4. Lin = 0, Rin = 0 after Lin = 1, Rin = 0 gives output Lout = 1, Rout = 0. 5. Lin = 0, Rin = 0 after Lin = 0, Rin = 1 gives output Lout = 0, Rout = 1. State 1 has both paddles open and neither key line keyed. States 2 and 3 have either just the left or just the right paddle closed and the correspo ...

... 4. Lin = 0, Rin = 0 after Lin = 1, Rin = 0 gives output Lout = 1, Rout = 0. 5. Lin = 0, Rin = 0 after Lin = 0, Rin = 1 gives output Lout = 0, Rout = 1. State 1 has both paddles open and neither key line keyed. States 2 and 3 have either just the left or just the right paddle closed and the correspo ...

VSP3010 数据资料 dataSheet 下载

... The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specific ...

... The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specific ...

SP485E 数据资料DataSheet下载

... accepted ESD testing method for semiconductors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’s potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by ...

... accepted ESD testing method for semiconductors. This method is also specified in MIL-STD-883, Method 3015.7 for ESD testing. The premise of this ESD test is to simulate the human body’s potential to store electro-static energy and discharge it to an integrated circuit. The simulation is performed by ...

Ω MAX9153/MAX9154 Low-Jitter, 800Mbps, 10-Port LVDS Repeaters with 100

... signaling (LVDS) repeaters are ideal for applications that require high-speed data or clock distribution while minimizing power, space, and noise. The devices accept a single LVDS input (MAX9153) or single LVPECL input (MAX9154) and repeat the signal at 10 LVDS outputs. Each differential output driv ...

... signaling (LVDS) repeaters are ideal for applications that require high-speed data or clock distribution while minimizing power, space, and noise. The devices accept a single LVDS input (MAX9153) or single LVPECL input (MAX9154) and repeat the signal at 10 LVDS outputs. Each differential output driv ...

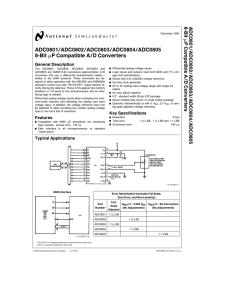

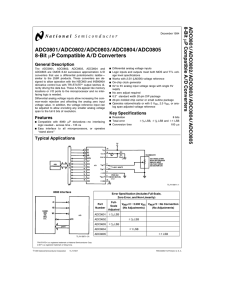

ADC0801 ADC0802 ADC0803 ADC0804 ADC0805 8

... latch and then an interrupt is asserted (INTR makes a highto-low transition). A conversion in process can be interrupted by issuing a second start command. The device may be operated in the free-running mode by connecting INTR to the WR input with CS e 0. To ensure start-up under all possible condit ...

... latch and then an interrupt is asserted (INTR makes a highto-low transition). A conversion in process can be interrupted by issuing a second start command. The device may be operated in the free-running mode by connecting INTR to the WR input with CS e 0. To ensure start-up under all possible condit ...

ADC0801/ADC0802/ADC0803/ADC0804/ADC0805 8-Bit mP Compatible A/D Converters 8-Bit m

... latch and then an interrupt is asserted (INTR makes a highto-low transition). A conversion in process can be interrupted by issuing a second start command. The device may be operated in the free-running mode by connecting INTR to the WR input with CS e 0. To ensure start-up under all possible condit ...

... latch and then an interrupt is asserted (INTR makes a highto-low transition). A conversion in process can be interrupted by issuing a second start command. The device may be operated in the free-running mode by connecting INTR to the WR input with CS e 0. To ensure start-up under all possible condit ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.