2139000 - ESCIES

... The time between the specified reference points on the input and output voltage waveforms with the specified output changing from the defined high level to the defined low level. The reference points on both the input and output waveforms are the same value which is midway between the maximum low-le ...

... The time between the specified reference points on the input and output voltage waveforms with the specified output changing from the defined high level to the defined low level. The reference points on both the input and output waveforms are the same value which is midway between the maximum low-le ...

a AN-581 APPLICATION NOTE Biasing and Decoupling Op Amps

... used to buffer the output of a VS/2 voltage divider. If a low voltage battery such as 3.3 V is used, the op amp should be a “rail-to-rail” device and able to operate effectively from this supply voltage. The op amp also needs to be able to supply an output current large enough to power the load circ ...

... used to buffer the output of a VS/2 voltage divider. If a low voltage battery such as 3.3 V is used, the op amp should be a “rail-to-rail” device and able to operate effectively from this supply voltage. The op amp also needs to be able to supply an output current large enough to power the load circ ...

www.BDTIC.com/TI Designing With Logic SDYA009C June 1997

... Many parameter values in data sheets are not measured when the circuits are tested. The information is based on typical values that have been established experimentally and that are applicable to the majority of devices of the same type or family. In individual cases it might be necessary to interpr ...

... Many parameter values in data sheets are not measured when the circuits are tested. The information is based on typical values that have been established experimentally and that are applicable to the majority of devices of the same type or family. In individual cases it might be necessary to interpr ...

AD8328 - Analog Devices

... Data Enable Low Input. This port controls the 8-bit parallel data latch and shift register. A Logic 0-to-Logic 1 transition transfers the latched data to the attenuator core (updates the gain) and simultaneously inhibits serial data transfer into the register. A Logic 1-to-Logic 0 transition inhibit ...

... Data Enable Low Input. This port controls the 8-bit parallel data latch and shift register. A Logic 0-to-Logic 1 transition transfers the latched data to the attenuator core (updates the gain) and simultaneously inhibits serial data transfer into the register. A Logic 1-to-Logic 0 transition inhibit ...

VLSI Digital System Design

... • Surround pMOS transistor by: – p+ ring connected to VDD, surrounded by – n-well with n+ connection to VSS ...

... • Surround pMOS transistor by: – p+ ring connected to VDD, surrounded by – n-well with n+ connection to VSS ...

MAX3801 3.2Gbps Adaptive Equalizer General Description Features

... The adaptive cable equalizer accepts differential CML input data at rates up to 3.2Gbps and is capable of equalizing differential or single-ended signals. It automatically adjusts to attenuation levels of up to 30dB at 1.6GHz (because of skin-effect losses in copper cable). The equalizer consists of ...

... The adaptive cable equalizer accepts differential CML input data at rates up to 3.2Gbps and is capable of equalizing differential or single-ended signals. It automatically adjusts to attenuation levels of up to 30dB at 1.6GHz (because of skin-effect losses in copper cable). The equalizer consists of ...

FAN4174 / FAN4274 Single and Dual, Rail-to-Rail I/O, CMOS Amplifier nd Dual,

... the rails by more than 0.5 V, the input ESD devices begin to conduct. The output stays at the rail during this overdrive condition. If the absolute maximum input VIN (700 mV beyond either rail) is exceeded, externally limit the input current to ±5 mA, as shown in Figure 22. ...

... the rails by more than 0.5 V, the input ESD devices begin to conduct. The output stays at the rail during this overdrive condition. If the absolute maximum input VIN (700 mV beyond either rail) is exceeded, externally limit the input current to ±5 mA, as shown in Figure 22. ...

FXLA104 Low-Voltage Dual-Supply 4-Bit Voltage Translator with

... as low as 1.1V. The A port tracks the VCCA level and the B port tracks the VCCB level. This allows for bi-directional voltage translation over a variety of voltage levels: 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V. The device remains in three-state as long as either VCC=0V, allowing either VCC to be powered ...

... as low as 1.1V. The A port tracks the VCCA level and the B port tracks the VCCB level. This allows for bi-directional voltage translation over a variety of voltage levels: 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V. The device remains in three-state as long as either VCC=0V, allowing either VCC to be powered ...

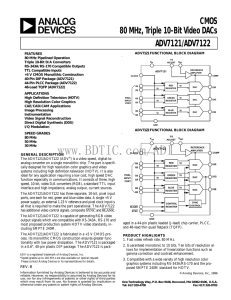

ADV7122 数据手册DataSheet 下载

... All these digital inputs are specified to accept TTL logic levels. Clock Input The CLOCK input of the ADV7121/ADV7122 is typically the pixel clock rate of the system. It is also known as the dot rate. The dot rate, and hence the required CLOCK frequency, will be determined by the on-screen resolutio ...

... All these digital inputs are specified to accept TTL logic levels. Clock Input The CLOCK input of the ADV7121/ADV7122 is typically the pixel clock rate of the system. It is also known as the dot rate. The dot rate, and hence the required CLOCK frequency, will be determined by the on-screen resolutio ...

ICS843201-375 - Integrated Device Technology

... and a multi-layer board, the appropriate value is 99.9°C/W per Table 8 below. Therefore, Tj for an ambient temperature of 70°C with all outputs switching is: 70°C + 0.404W * 99.9°C/W = 110°C. This is well below the limit of 125°C. This calculation is only an example. Tj will obviously vary depending ...

... and a multi-layer board, the appropriate value is 99.9°C/W per Table 8 below. Therefore, Tj for an ambient temperature of 70°C with all outputs switching is: 70°C + 0.404W * 99.9°C/W = 110°C. This is well below the limit of 125°C. This calculation is only an example. Tj will obviously vary depending ...

MAX2150 Wideband I/Q Modulator with Sigma-Delta Fractional-N Synthesizer General Description

... Differential Local-Oscillator Input. These inputs require DC-blocking capacitors. The LO can be applied with a single-ended input to the LO+/LO- pin. In this mode, the other pin should be AC-grounded. ...

... Differential Local-Oscillator Input. These inputs require DC-blocking capacitors. The LO can be applied with a single-ended input to the LO+/LO- pin. In this mode, the other pin should be AC-grounded. ...

DMR-203

... connection failure by using short and properly terminated connection cables. Do not twist wires together. DO NOT make connections while the system is powered up. RC control requires signals to be synchronised and the input signal may be misinterpreted. DO NOT connect LED's or other I/O devices to th ...

... connection failure by using short and properly terminated connection cables. Do not twist wires together. DO NOT make connections while the system is powered up. RC control requires signals to be synchronised and the input signal may be misinterpreted. DO NOT connect LED's or other I/O devices to th ...

Low Cost 10-Bit, 6-Channel Output Decimating LCD DecDriver AD8383

... The AD8383 provides a fast, 10-bit latched decimating digital input that drives six high voltage outputs. 10-bit input words are sequentially loaded into six separate, high speed, bipolar DACs. Flexible digital input format allows several AD8383s to be used in parallel for higher resolution displays ...

... The AD8383 provides a fast, 10-bit latched decimating digital input that drives six high voltage outputs. 10-bit input words are sequentially loaded into six separate, high speed, bipolar DACs. Flexible digital input format allows several AD8383s to be used in parallel for higher resolution displays ...

1. Input matching

... source degeneration topology. The value of inductor L4 is kept low around 0.025nH. The value of inductance L5 is varied accordingly to be tuned at resonant frequency 4.29GHz. If the matching is done properly the no power is reflected back at the input side. 2. OUTPUT MATCHING Output matching is resp ...

... source degeneration topology. The value of inductor L4 is kept low around 0.025nH. The value of inductance L5 is varied accordingly to be tuned at resonant frequency 4.29GHz. If the matching is done properly the no power is reflected back at the input side. 2. OUTPUT MATCHING Output matching is resp ...

Dual Channel, High-Voltage - Multi

... CW gate input signal for A output. An input ‘1’ means that current sinks from OUTA. An input ‘0’ means that current sources from OUTA. This pin directly accesses the output A CW FET gates. ...

... CW gate input signal for A output. An input ‘1’ means that current sinks from OUTA. An input ‘0’ means that current sources from OUTA. This pin directly accesses the output A CW FET gates. ...

Multiple Choice Questions

... 75. What is asynchronous counter : a) each flip-flop has it own clock b) all the flip-flop are combined to common clock c) both a and b d) none of the above 76. UP Counter is : a) it counts in upward manner b) it count in down ward manner c) it counts in both the direction d) none of the above 77. D ...

... 75. What is asynchronous counter : a) each flip-flop has it own clock b) all the flip-flop are combined to common clock c) both a and b d) none of the above 76. UP Counter is : a) it counts in upward manner b) it count in down ward manner c) it counts in both the direction d) none of the above 77. D ...

Complete 14-Bit CCD/CIS Signal Processor AD9822

... The AD9822 is a complete analog signal processor for CCD imaging applications. It features a 3-channel architecture designed to sample and condition the outputs of trilinear color CCD arrays. Each channel consists of an input clamp, correlated double sampler (CDS), offset DAC, and programmable gain ...

... The AD9822 is a complete analog signal processor for CCD imaging applications. It features a 3-channel architecture designed to sample and condition the outputs of trilinear color CCD arrays. Each channel consists of an input clamp, correlated double sampler (CDS), offset DAC, and programmable gain ...

arad waterworks

... A 3 pointer register with a serrated wheel mounted on the central shaft of the register for activating a photo-diode sensor. Output definition: Flowrate output. Output type: EF. The sensor is installed and hermetically sealed within a transparent plastic cover. The high number of teeth and the r ...

... A 3 pointer register with a serrated wheel mounted on the central shaft of the register for activating a photo-diode sensor. Output definition: Flowrate output. Output type: EF. The sensor is installed and hermetically sealed within a transparent plastic cover. The high number of teeth and the r ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.