AD9726 数据手册DataSheet 下载

... This reduces system complexity and simplifies timing requirements. An LVDS clock output is also available to drive an external data pump in either single data rate (SDR) or double data rate (DDR) mode. All device operation is fully programmable using the flexible serial port interface (SPI). The AD9 ...

... This reduces system complexity and simplifies timing requirements. An LVDS clock output is also available to drive an external data pump in either single data rate (SDR) or double data rate (DDR) mode. All device operation is fully programmable using the flexible serial port interface (SPI). The AD9 ...

Lionel E-Unit 00-0103-00 Theory of Operation

... This section (see Figure 1 and Figure 3) consists primarily of a two-bit binary counter (4 condition state machine) implemented in a Dual D-Type Flip/Flop (U1). Each Flip/Flop is configured as a digital Toggle Flip/Flop. The Flip/Flops are powered by VCC (which remains constant even during AC input ...

... This section (see Figure 1 and Figure 3) consists primarily of a two-bit binary counter (4 condition state machine) implemented in a Dual D-Type Flip/Flop (U1). Each Flip/Flop is configured as a digital Toggle Flip/Flop. The Flip/Flops are powered by VCC (which remains constant even during AC input ...

High Speed, ESD-Protected, Full-Duplex, ADM2490E i

... TxD pin and referenced to logic ground (GND1), is coupled across an isolation barrier to appear at the transceiver section referenced to isolated ground (GND2). Similarly, the receiver input, which is referenced to isolated ground in the transceiver section, is coupled across the isolation barrier t ...

... TxD pin and referenced to logic ground (GND1), is coupled across an isolation barrier to appear at the transceiver section referenced to isolated ground (GND2). Similarly, the receiver input, which is referenced to isolated ground in the transceiver section, is coupled across the isolation barrier t ...

Physical Implementation - Inst.eecs.berkeley.edu

... roved from early test-chip hardware, which showed much as 70 ps skew from across-chip channel-length ations [19]. Detailed waveforms at the input and put of each global clock buffer were also measured compared with simulation to verify the specialized deling used to design the clock grid. Good agree ...

... roved from early test-chip hardware, which showed much as 70 ps skew from across-chip channel-length ations [19]. Detailed waveforms at the input and put of each global clock buffer were also measured compared with simulation to verify the specialized deling used to design the clock grid. Good agree ...

- Texas Instruments

... B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. C. All input pulses are supplied by generators ...

... B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control. C. All input pulses are supplied by generators ...

Rev D - AMETEK Programmable Power

... protective cover and allow the internal capacitors to fully discharge (minimum of 15 mins) before removing any cover.) See Figure 2-2 for details. No wiring for AC input connections is provided with the MX Series and must be provided by the end user or installer. Input wiring should be entered throu ...

... protective cover and allow the internal capacitors to fully discharge (minimum of 15 mins) before removing any cover.) See Figure 2-2 for details. No wiring for AC input connections is provided with the MX Series and must be provided by the end user or installer. Input wiring should be entered throu ...

ADM202 数据手册DataSheet 下载

... The ADM202/ADM203 is an RS-232 drivers/receivers designed to solve interface problems by meeting the EIA-232E specifications while using a single digital 5 V supply. The EIA standard requires transmitters that will deliver ± 5 V minimum on the transmission channel and receivers that can accept signa ...

... The ADM202/ADM203 is an RS-232 drivers/receivers designed to solve interface problems by meeting the EIA-232E specifications while using a single digital 5 V supply. The EIA standard requires transmitters that will deliver ± 5 V minimum on the transmission channel and receivers that can accept signa ...

AD9709 数据手册DataSheet 下载

... communications applications. The digital interface consists of two double-buffered latches as well as control logic. Separate write inputs allow data to be written to the two DAC ports independent of one another. Separate clocks control the update rate of the DACs. A mode control pin allows the AD97 ...

... communications applications. The digital interface consists of two double-buffered latches as well as control logic. Separate write inputs allow data to be written to the two DAC ports independent of one another. Separate clocks control the update rate of the DACs. A mode control pin allows the AD97 ...

MAX132 - Maxim

... analog-to-digital converter (ADC). Multi-slope integration provides high-resolution conversions in less time than standard integrating ADCs, allowing operation up to 100 conversions per second. Low conversion noise provides guaranteed operation with ±512mV full-scale input range (2µV/LSB). A simple ...

... analog-to-digital converter (ADC). Multi-slope integration provides high-resolution conversions in less time than standard integrating ADCs, allowing operation up to 100 conversions per second. Low conversion noise provides guaranteed operation with ±512mV full-scale input range (2µV/LSB). A simple ...

MAX5188/MAX5191 Dual, 8-Bit, 40MHz, Current/Voltage, Alternate-Phase Output DACs General Description

... Detailed Description The MAX5188/MAX5191 are dual 8-bit digital-to-analog converters (DACs) capable of operating with clock speeds up to 40MHz. Each of these dual converters consists of separate input and DAC registers, followed by a current-source array capable of generating up to 1.5mA full-scale ...

... Detailed Description The MAX5188/MAX5191 are dual 8-bit digital-to-analog converters (DACs) capable of operating with clock speeds up to 40MHz. Each of these dual converters consists of separate input and DAC registers, followed by a current-source array capable of generating up to 1.5mA full-scale ...

WizFi210/220 User Manual (Version 1.11) ©2011 WIZnet Co., Ltd. All Rights Reserved.

... INFORMATION TO THE USER These equipments have been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment gene ...

... INFORMATION TO THE USER These equipments have been tested and found to comply with the limits for a Class B digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment gene ...

a high-drive fully differential current mode operational

... B. Simulation results of the COA-based filter The following values are selected to realize a COA based band-stop filter. Quality factor (Q) is 1/4, center frequency is ≈ 400 kHz and element values in the circuit are chosen as R2 = R1/2 = 10 kΩ, C1 = C2/2= 20 pF. As shown in Figure 7, simulated and ...

... B. Simulation results of the COA-based filter The following values are selected to realize a COA based band-stop filter. Quality factor (Q) is 1/4, center frequency is ≈ 400 kHz and element values in the circuit are chosen as R2 = R1/2 = 10 kΩ, C1 = C2/2= 20 pF. As shown in Figure 7, simulated and ...

Software Design and Hardware Realisation of Single Phase

... Zero crossing detector: In the non-inverting comparator mode, the same ac input is given to non-inverting input of op-amp and inverting input is grounded. A positive square pulse during the positive half cycle of ac input is obtained. In inverting comparator mode, the ac input is given to inverting ...

... Zero crossing detector: In the non-inverting comparator mode, the same ac input is given to non-inverting input of op-amp and inverting input is grounded. A positive square pulse during the positive half cycle of ac input is obtained. In inverting comparator mode, the ac input is given to inverting ...

DAC-HF - DATEL

... inherently reduces the amplitude and duration of large transient spikes at the output (“glitches”). The most severe glitches occur at half-scale, the major carry transition from 011 … 1 to 100 … 0 or vice versa. At this time, a skewing of the input codes can create a transition state code of 111 … 1 ...

... inherently reduces the amplitude and duration of large transient spikes at the output (“glitches”). The most severe glitches occur at half-scale, the major carry transition from 011 … 1 to 100 … 0 or vice versa. At this time, a skewing of the input codes can create a transition state code of 111 … 1 ...

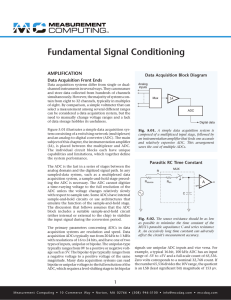

Fundamental Signal Conditioning

... analog domain and the digitized signal path. In any sampled-data system, such as a multiplexed data acquisition system, a sample-and-hold stage preceding the ADC is necessary. The ADC cannot digitize a time-varying voltage to the full resolution of the ADC unless the voltage changes relatively slowl ...

... analog domain and the digitized signal path. In any sampled-data system, such as a multiplexed data acquisition system, a sample-and-hold stage preceding the ADC is necessary. The ADC cannot digitize a time-varying voltage to the full resolution of the ADC unless the voltage changes relatively slowl ...

MAX221 +5V, 1µA, Single RS-232 Transceiver with AutoShutdown General Description

... based on the receiver input level. Figures 2a, 2b, and 3a depict valid and invalid RS-232 receiver levels. Figure 3 shows the input levels and timing diagram for AutoShutdown operation. A device or another system with AutoShutdown connected to the MAX221 may need time to wake up. Figure 4 shows a ci ...

... based on the receiver input level. Figures 2a, 2b, and 3a depict valid and invalid RS-232 receiver levels. Figure 3 shows the input levels and timing diagram for AutoShutdown operation. A device or another system with AutoShutdown connected to the MAX221 may need time to wake up. Figure 4 shows a ci ...

10-Bit, 40 MSPS, 3 V, 74 mW A/D Converter AD9203

... An external resistor can be used to reduce power consumption when operating at lower sampling rates. This yields power savings for users who do not require the maximum sample rate. This feature is especially useful at sample rates far below 40 MSPS. Excellent performance is still achieved at reduced ...

... An external resistor can be used to reduce power consumption when operating at lower sampling rates. This yields power savings for users who do not require the maximum sample rate. This feature is especially useful at sample rates far below 40 MSPS. Excellent performance is still achieved at reduced ...

Digital Circuitry

... Typical Propagation delay time is 1nS Fanout is typically about 25. Low Impedance emitter-follower outputs 5.4: ECL Advantages The transistors never saturate and so switching speed is very high., which makes ECL a little faster than advanced Schottky TTL An ECL logic block usually produces an ...

... Typical Propagation delay time is 1nS Fanout is typically about 25. Low Impedance emitter-follower outputs 5.4: ECL Advantages The transistors never saturate and so switching speed is very high., which makes ECL a little faster than advanced Schottky TTL An ECL logic block usually produces an ...

AN88 - Ceramic Input Capacitors Can Cause Overvoltage Transients

... A recent trend in the design of portable devices has been to use ceramic capacitors to filter DC/DC converter inputs. Ceramic capacitors are often chosen because of their small size, low equivalent series resistance (ESR) and high RMS current capability. Also, recently, designers have been looking t ...

... A recent trend in the design of portable devices has been to use ceramic capacitors to filter DC/DC converter inputs. Ceramic capacitors are often chosen because of their small size, low equivalent series resistance (ESR) and high RMS current capability. Also, recently, designers have been looking t ...

ADM2491E 数据手册DataSheet 下载

... communication on multipoint transmission lines. For halfduplex operation, the transmitter outputs and the receiver inputs share the same transmission line. Transmitter output Pin Y is linked externally to receiver input Pin A, and transmitter output Pin Z is linked to receiver input Pin B. The ADM24 ...

... communication on multipoint transmission lines. For halfduplex operation, the transmitter outputs and the receiver inputs share the same transmission line. Transmitter output Pin Y is linked externally to receiver input Pin A, and transmitter output Pin Z is linked to receiver input Pin B. The ADM24 ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.