MAX9317/MAX9317A/MAX9317B/MAX9317C Dual 1:5 Differential Clock Drivers with LVPECL Inputs and LVDS Outputs

... Note 1: Measurements are made with the device in thermal equilibrium. Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative. Note 3: DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterization over the full operating ...

... Note 1: Measurements are made with the device in thermal equilibrium. Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative. Note 3: DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterization over the full operating ...

Potentiometer input signal conditioner

... to remote PID controllers or interfacing position sensors to data acquisition and control systems. The DRG-SC-PT's high density DIN rail mounting offers an extremely compact solution for saving valuable panel space. ...

... to remote PID controllers or interfacing position sensors to data acquisition and control systems. The DRG-SC-PT's high density DIN rail mounting offers an extremely compact solution for saving valuable panel space. ...

DAC102S085 10-Bit Micro Pwr DUAL DAC w

... When the input voltage at any pin exceeds 5.5 V or is less than GND, the current at that pin should be limited to 10 mA. The 20-mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two. The maximum allowable pow ...

... When the input voltage at any pin exceeds 5.5 V or is less than GND, the current at that pin should be limited to 10 mA. The 20-mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two. The maximum allowable pow ...

LT6552 - 3.3V Single Supply Video Difference Amplifier

... On a single 3.3V supply, the input voltage range extends from ground to 1.3V and the output swings from ground to 2.9V while driving a 150Ω load. The LT6552 features 75MHz – 3dB bandwidth, 600V/µs slew rate, and ±70mA output current making it ideal for driving cables directly. The LT6552 maintains i ...

... On a single 3.3V supply, the input voltage range extends from ground to 1.3V and the output swings from ground to 2.9V while driving a 150Ω load. The LT6552 features 75MHz – 3dB bandwidth, 600V/µs slew rate, and ±70mA output current making it ideal for driving cables directly. The LT6552 maintains i ...

DS1843 Fast Sample-and-Hold Circuit General Description Features

... designed to operate in fiber optic burst-mode systems; however, it can be used in other applications requiring a fast sample-and-hold circuit. The output can be configured for single-ended operations. ...

... designed to operate in fiber optic burst-mode systems; however, it can be used in other applications requiring a fast sample-and-hold circuit. The output can be configured for single-ended operations. ...

MAX4528 Low-Voltage, Phase-Reversal Analog Switch ________________General Description

... The MAX4528’s construction is typical of most CMOS analog switches. It has three supply pins: V+, V-, and GND. V+ and V- drive the internal CMOS switches and set the analog-voltage limits on any switch. Reverse ESD-protection diodes are internally connected between each analog-signal pin and both V+ ...

... The MAX4528’s construction is typical of most CMOS analog switches. It has three supply pins: V+, V-, and GND. V+ and V- drive the internal CMOS switches and set the analog-voltage limits on any switch. Reverse ESD-protection diodes are internally connected between each analog-signal pin and both V+ ...

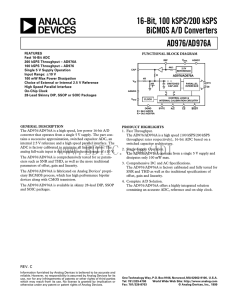

AD976 数据手册DataSheet下载

... Data Bit 0. Least significant bit of conversion result. High impedance state when CS is HIGH or when R/C is LOW. Byte Select. With BYTE LOW, data will be output as indicated above; Pin 6 (D15) is the MSB, Pin 22 (D0) is the LSB. With BYTE HIGH, the top and bottom 8 bits of data will be switched; D15 ...

... Data Bit 0. Least significant bit of conversion result. High impedance state when CS is HIGH or when R/C is LOW. Byte Select. With BYTE LOW, data will be output as indicated above; Pin 6 (D15) is the MSB, Pin 22 (D0) is the LSB. With BYTE HIGH, the top and bottom 8 bits of data will be switched; D15 ...

SN65LVCP204 数据资料 dataSheet 下载

... The SN65LVCP204 is a 4×4 non-blocking crosspoint switch in a flow-through pinout that allows for ease in PCB layout. VML signaling is used to achieve a high-speed data throughput while using low power. Each of the output drivers includes a 4:1 multiplexer to allow any input to be routed to any outpu ...

... The SN65LVCP204 is a 4×4 non-blocking crosspoint switch in a flow-through pinout that allows for ease in PCB layout. VML signaling is used to achieve a high-speed data throughput while using low power. Each of the output drivers includes a 4:1 multiplexer to allow any input to be routed to any outpu ...

AD7782 数据手册DataSheet下载

... Chip Select Input. CS is an active low logic input used to select the AD7782. When CS is low, the PLL establishes lock and allows the AD7782 to initiate a conversion on the selected channel. When CS is high, the conversion is aborted, DOUT and SCLK are three-stated, the AD7782 enters standby mode an ...

... Chip Select Input. CS is an active low logic input used to select the AD7782. When CS is low, the PLL establishes lock and allows the AD7782 to initiate a conversion on the selected channel. When CS is high, the conversion is aborted, DOUT and SCLK are three-stated, the AD7782 enters standby mode an ...

ACPL-K33T: Automotive 2.5 A Peak High Output Current SiC

... Drive Optocoupler contains an AlGaAs LED, which is optically coupled to an integrated circuit with a power output stage. The ACPL-K33T features fast propagation delay and tight timing skew, is ideally designed for driving SiC MOSFET and IGBTs used in AC-DC and DC-DC converters. The high operating vo ...

... Drive Optocoupler contains an AlGaAs LED, which is optically coupled to an integrated circuit with a power output stage. The ACPL-K33T features fast propagation delay and tight timing skew, is ideally designed for driving SiC MOSFET and IGBTs used in AC-DC and DC-DC converters. The high operating vo ...

AD9726 数据手册DataSheet 下载

... This reduces system complexity and simplifies timing requirements. An LVDS clock output is also available to drive an external data pump in either single data rate (SDR) or double data rate (DDR) mode. All device operation is fully programmable using the flexible serial port interface (SPI). The AD9 ...

... This reduces system complexity and simplifies timing requirements. An LVDS clock output is also available to drive an external data pump in either single data rate (SDR) or double data rate (DDR) mode. All device operation is fully programmable using the flexible serial port interface (SPI). The AD9 ...

AD8564 数据手册DataSheet 下载

... negative supply rail to within 2.2 V of the positive supply rail. The input common-mode voltage can be found as the average of the voltage at the two inputs of the device. To ensure the fastest response time, care should be taken to not allow the input common-mode voltage to exceed this voltage. The ...

... negative supply rail to within 2.2 V of the positive supply rail. The input common-mode voltage can be found as the average of the voltage at the two inputs of the device. To ensure the fastest response time, care should be taken to not allow the input common-mode voltage to exceed this voltage. The ...

Two-electrode non-differential biopotential amplifier

... The operational amplifier U2 was selected for a low input bias current (MOSFET or JFET input stage) and a high open-loop gain, to minimise the input error voltage. In this case, the popular TL072 is used. The amplifier inputs InP and InN can tolerate serial resistors, for protection and=or as part o ...

... The operational amplifier U2 was selected for a low input bias current (MOSFET or JFET input stage) and a high open-loop gain, to minimise the input error voltage. In this case, the popular TL072 is used. The amplifier inputs InP and InN can tolerate serial resistors, for protection and=or as part o ...

Evaluation Board EVAL-1EDI60I12AF

... The gate driver evaluation board EVAL-1EDI60I12AF was developed to demonstrate the functionalities and key features of Infineon’s IGBT gate driver 1EDI60I12AF. The board is available from Infineon in sampling quantities. Main features of this board are described in the datasheet chapter of this docu ...

... The gate driver evaluation board EVAL-1EDI60I12AF was developed to demonstrate the functionalities and key features of Infineon’s IGBT gate driver 1EDI60I12AF. The board is available from Infineon in sampling quantities. Main features of this board are described in the datasheet chapter of this docu ...

Lionel E-Unit 00-0103-00 Theory of Operation

... This section (see Figure 1 and Figure 3) consists primarily of a two-bit binary counter (4 condition state machine) implemented in a Dual D-Type Flip/Flop (U1). Each Flip/Flop is configured as a digital Toggle Flip/Flop. The Flip/Flops are powered by VCC (which remains constant even during AC input ...

... This section (see Figure 1 and Figure 3) consists primarily of a two-bit binary counter (4 condition state machine) implemented in a Dual D-Type Flip/Flop (U1). Each Flip/Flop is configured as a digital Toggle Flip/Flop. The Flip/Flops are powered by VCC (which remains constant even during AC input ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.