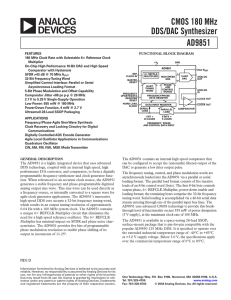

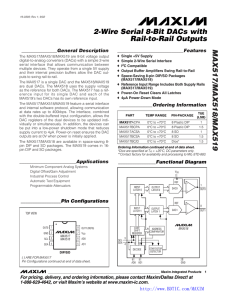

MAX517/MAX518/MAX519 2-Wire Serial 8-Bit DACs with Rail-to-Rail Outputs _______________General Description

... the timing diagram for signals on the 2-wire bus. Figure 3 shows a typical application. The 2-wire bus can have several devices (in addition to the MAX517/ MAX518/MAX519) attached. The two bus lines (SDA and SCL) must be high when the bus is not in use. When in use, the port bits are toggled to gene ...

... the timing diagram for signals on the 2-wire bus. Figure 3 shows a typical application. The 2-wire bus can have several devices (in addition to the MAX517/ MAX518/MAX519) attached. The two bus lines (SDA and SCL) must be high when the bus is not in use. When in use, the port bits are toggled to gene ...

Spartan-3 FPGA Family - start [kondor.etf.rs]

... data into robust static memory cells that collectively control all functional elements and routing resources. Before powering on the FPGA, configuration data is stored externally in a PROM or some other nonvolatile medium either on or off the board. After applying power, the configuration data is wr ...

... data into robust static memory cells that collectively control all functional elements and routing resources. Before powering on the FPGA, configuration data is stored externally in a PROM or some other nonvolatile medium either on or off the board. After applying power, the configuration data is wr ...

Chapter 10: Operational Amplifiers

... An op-amp is a wide-bandwidth amplifier. The following affect the bandwidth of the op-amp: • Gain ...

... An op-amp is a wide-bandwidth amplifier. The following affect the bandwidth of the op-amp: • Gain ...

doc - CERN

... Before we are able to solve our task we have to specify our electronic. The task of this internship was to examine the different possibilities to measure the particle loss rate. Preliminary studies of the ionization chamber show that an output current of 1 mA corresponds to 1013 proton losses/m/s. S ...

... Before we are able to solve our task we have to specify our electronic. The task of this internship was to examine the different possibilities to measure the particle loss rate. Preliminary studies of the ionization chamber show that an output current of 1 mA corresponds to 1013 proton losses/m/s. S ...

Extending the Common-Mode Range of

... connection, VX. The circuits in Figure 1 or 3 will not work with zero differential input. Since the difference amp reference pin is connected to V–, the output of the difference amp would saturate to its negative swing limit in an attempt to swing to V–. For the circuit to work, the differential inp ...

... connection, VX. The circuits in Figure 1 or 3 will not work with zero differential input. Since the difference amp reference pin is connected to V–, the output of the difference amp would saturate to its negative swing limit in an attempt to swing to V–. For the circuit to work, the differential inp ...

AD7484 数据手册DataSheet下载

... Analog Input. Single ended analog input channel. Reference Output. REFOUT connects to the output of the internal 2.5 V reference buffer. A 470 nF capacitor must be placed between this pin and AGND. Reference Input. A 470 nF capacitor must be placed between this pin and AGND. When using an external v ...

... Analog Input. Single ended analog input channel. Reference Output. REFOUT connects to the output of the internal 2.5 V reference buffer. A 470 nF capacitor must be placed between this pin and AGND. Reference Input. A 470 nF capacitor must be placed between this pin and AGND. When using an external v ...

CMOS 180 MHz DDS/DAC Synthesizer AD9851

... +VS collectively refers to the positive voltages applied to DVDD, PVCC, and AVDD. Voltages applied to these pins should be of the same potential. ...

... +VS collectively refers to the positive voltages applied to DVDD, PVCC, and AVDD. Voltages applied to these pins should be of the same potential. ...

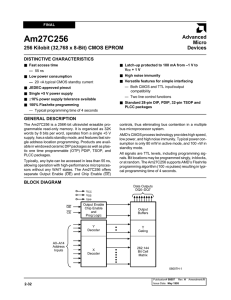

Am27C256

... During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1-µF ceramic capacitor (high fr ...

... During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1-µF ceramic capacitor (high fr ...

Vocal Harmonizer and Vocoder

... The final design is a simple, fourth-order, "multiple-feedback" bandpass filter. The design was taken from Don Lancaster's Active Filter Cookbook on page 154. The transfer function for a single stage of this filter is straightforward to compute, albeit tedious. The result is -1/R1/C2 * s / (s^2+2/R3 ...

... The final design is a simple, fourth-order, "multiple-feedback" bandpass filter. The design was taken from Don Lancaster's Active Filter Cookbook on page 154. The transfer function for a single stage of this filter is straightforward to compute, albeit tedious. The result is -1/R1/C2 * s / (s^2+2/R3 ...

High Speed, ESD-Protected, Full-Duplex, ADM2490E i

... iCoupler® technology to combine a 2-channel isolator, a threestate differential line driver, and a differential input receiver into a single package. The differential transmitter outputs and receiver inputs feature electrostatic discharge circuitry that provides protection to ±8 kV ...

... iCoupler® technology to combine a 2-channel isolator, a threestate differential line driver, and a differential input receiver into a single package. The differential transmitter outputs and receiver inputs feature electrostatic discharge circuitry that provides protection to ±8 kV ...

AD7621 数据手册DataSheet下载

... Serial/Parallel Selection Input. When high, the serial interface is selected and some bits of the data bus are used as a serial port; the remaining data bits are high impedance outputs. When SER/PAR = low, the parallel port is selected. Bit 0 and Bit 1 of the Parallel Port Data Output Bus. When SER/ ...

... Serial/Parallel Selection Input. When high, the serial interface is selected and some bits of the data bus are used as a serial port; the remaining data bits are high impedance outputs. When SER/PAR = low, the parallel port is selected. Bit 0 and Bit 1 of the Parallel Port Data Output Bus. When SER/ ...

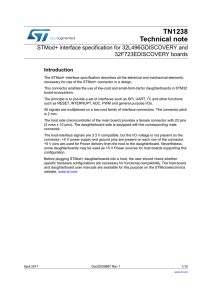

TN1238 - STMicroelectronics

... users shall plug very carefully the connectors together. In case of misalignment of pins or row inversions, it is possible to damage boards definitively. ...

... users shall plug very carefully the connectors together. In case of misalignment of pins or row inversions, it is possible to damage boards definitively. ...

FOD060L_FOD260L - 3.3V/5V High Speed

... of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein ...

... of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein ...

Aitech A175 Datasheet

... With its high variety of I/O interfaces, small form factor, low power dissipation, and standard MIL-STD-1553B avionics bus interface (RT), the A175 handily meets these requirements. It can be used to expand the I/O capabilities of any avionics computer with a standard MIL-STD-1553B interface. For se ...

... With its high variety of I/O interfaces, small form factor, low power dissipation, and standard MIL-STD-1553B avionics bus interface (RT), the A175 handily meets these requirements. It can be used to expand the I/O capabilities of any avionics computer with a standard MIL-STD-1553B interface. For se ...

W

... 10. Multiple O/P Domino Logic Hwang and Fisher formally introduced MODL in 1989, and it has been shown to provide considerable hardware savings. In domino CMOS logic, as well as other non complementary MOS logic styles, there is only one output available from a given logic gate. However, it is a fa ...

... 10. Multiple O/P Domino Logic Hwang and Fisher formally introduced MODL in 1989, and it has been shown to provide considerable hardware savings. In domino CMOS logic, as well as other non complementary MOS logic styles, there is only one output available from a given logic gate. However, it is a fa ...

AD7482 数据手册DataSheet下载

... Analog Input. Single ended analog input channel. Reference Output. REFOUT connects to the output of the internal 2.5 V reference buffer. A 470 nF capacitor must be placed between this pin and AGND. Reference Input. A 470 nF capacitor must be placed between this pin and AGND. When using an external v ...

... Analog Input. Single ended analog input channel. Reference Output. REFOUT connects to the output of the internal 2.5 V reference buffer. A 470 nF capacitor must be placed between this pin and AGND. Reference Input. A 470 nF capacitor must be placed between this pin and AGND. When using an external v ...

Balanced Modulator/Demodulator AD630

... independent differential input stages and a precision comparator which is used to select the active front end. The rapid response time of this comparator coupled with the high slew rate and fast settling of the linear amplifiers minimize switching distortion. In addition, the AD630 has extremely low ...

... independent differential input stages and a precision comparator which is used to select the active front end. The rapid response time of this comparator coupled with the high slew rate and fast settling of the linear amplifiers minimize switching distortion. In addition, the AD630 has extremely low ...

SH24C-177 - Potter Electric Signal Company, LLC

... • Mounts to 4” square, single gang, double gang, or octagonal back box; SPC-1 (retrofit plate) and RBX-1 (back box skirt) are optional • Polarized strobes with wide operating voltage range using filtered DC or unfiltered FWR input voltage • Synchronization requires SMD10-3A Sync module • ...

... • Mounts to 4” square, single gang, double gang, or octagonal back box; SPC-1 (retrofit plate) and RBX-1 (back box skirt) are optional • Polarized strobes with wide operating voltage range using filtered DC or unfiltered FWR input voltage • Synchronization requires SMD10-3A Sync module • ...

STUSB03E

... controller. Internal circuitry provides translation between the USB and system voltage domains. VIF will typically be the main supply voltage rail for the controller. In addition, a 3.3V, 10% termination supply voltage, VPU, is provided to support speed selection. VPU can be disabled or enabled unde ...

... controller. Internal circuitry provides translation between the USB and system voltage domains. VIF will typically be the main supply voltage rail for the controller. In addition, a 3.3V, 10% termination supply voltage, VPU, is provided to support speed selection. VPU can be disabled or enabled unde ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.

![Spartan-3 FPGA Family - start [kondor.etf.rs]](http://s1.studyres.com/store/data/006500847_1-986be0be37a885f32642aebba00b9157-300x300.png)