5.2.3 Analogue to Digital Converters Word Document | GCE

... Notice that, in this case, the analogue input signal is connected directly to the inverting inputs of the eight comparators. Their non-inverting inputs are connected to various points on a resistor chain. This chain creates a different reference voltage for each comparator. Each comparator compares ...

... Notice that, in this case, the analogue input signal is connected directly to the inverting inputs of the eight comparators. Their non-inverting inputs are connected to various points on a resistor chain. This chain creates a different reference voltage for each comparator. Each comparator compares ...

i. introduction

... dynamic node enough to switch output buffer .The addition of the output inverter makes domino gates non-inverting. One can often design around this limitation, but some circuits cannot be implemented solely. In existing literature, 256-bit CLA & MCC adder circuit was designed using domino logic.To m ...

... dynamic node enough to switch output buffer .The addition of the output inverter makes domino gates non-inverting. One can often design around this limitation, but some circuits cannot be implemented solely. In existing literature, 256-bit CLA & MCC adder circuit was designed using domino logic.To m ...

MAX2691 L2 Band GPS Low

... These values are optimized for the best simultaneous gain, noise figure, and return loss performance. Reducing the input coupling capacitor results in a lower IIP3. The device integrates an on-chip output matching to 50I at the output, eliminating the need for external matching components. Table 1 l ...

... These values are optimized for the best simultaneous gain, noise figure, and return loss performance. Reducing the input coupling capacitor results in a lower IIP3. The device integrates an on-chip output matching to 50I at the output, eliminating the need for external matching components. Table 1 l ...

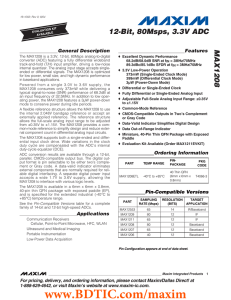

_______________General Description ____________________________Features

... a reference-buffer amplifier that simplifies gain trim. It also has a VL pin that supplies power to the digital outputs. Output logic levels (3V, 3.3V, or 5V) are determined by the value of the voltage applied to this pin. A hard-wired SHDN pin and two software-selectable power-down modes are provid ...

... a reference-buffer amplifier that simplifies gain trim. It also has a VL pin that supplies power to the digital outputs. Output logic levels (3V, 3.3V, or 5V) are determined by the value of the voltage applied to this pin. A hard-wired SHDN pin and two software-selectable power-down modes are provid ...

лабораторная работа №7 - Томский политехнический университет

... converters. The digital word is presented in a variety of codes, the most common being pure binary or binary-coded-decimal. Two types of DAC are distinguished: binary-weighted resistor DAC and DAC using R-2R ladder network. Often DAC is used as a part of ADC. There are many different ways to do an a ...

... converters. The digital word is presented in a variety of codes, the most common being pure binary or binary-coded-decimal. Two types of DAC are distinguished: binary-weighted resistor DAC and DAC using R-2R ladder network. Often DAC is used as a part of ADC. There are many different ways to do an a ...

ADM209 数据手册DataSheet 下载

... EIA-232-E and V.28 communications interfaces, especially in applications where ±12 V is not available. The ADM206, ADM211, and ADM213 feature a low power shutdown mode that reduces power dissipation to less than 5 µW, making them ideally suited for battery-powered equipment. The ADM213 has an active ...

... EIA-232-E and V.28 communications interfaces, especially in applications where ±12 V is not available. The ADM206, ADM211, and ADM213 feature a low power shutdown mode that reduces power dissipation to less than 5 µW, making them ideally suited for battery-powered equipment. The ADM213 has an active ...

UM1470

... Description of the schematic The input part of converter consists of an input single-wave rectifier, EMI/EMC filter and bulk capacitor. The input rectifier is based on two 1 A/1 kV general purpose diodes (D1, D2). The 2 kV blocking voltage is selected to increase robustness against input surge pulse ...

... Description of the schematic The input part of converter consists of an input single-wave rectifier, EMI/EMC filter and bulk capacitor. The input rectifier is based on two 1 A/1 kV general purpose diodes (D1, D2). The 2 kV blocking voltage is selected to increase robustness against input surge pulse ...

DS1813 5V EconoReset with Pushbutton GENERAL DESCRIPTION

... The DS1813 EconoReset uses a precision temperature reference and comparator circuit to monitor the status of the power supply (VCC). When an out-of-tolerance condition is detected, an internal power-fail signal is generated which forces reset to the active state. When VCC returns to an in-tolerance ...

... The DS1813 EconoReset uses a precision temperature reference and comparator circuit to monitor the status of the power supply (VCC). When an out-of-tolerance condition is detected, an internal power-fail signal is generated which forces reset to the active state. When VCC returns to an in-tolerance ...

SA612A Double-balanced mixer and oscillator

... -119dBm signals with a 12dB S/N ratio. Third-order intercept is typically -15dBm (that’s approximately +5dBm output intercept because of the RF gain). The system designer must be cognizant of this large signal limitation. When designing LANs or other closed systems where transmission levels are high ...

... -119dBm signals with a 12dB S/N ratio. Third-order intercept is typically -15dBm (that’s approximately +5dBm output intercept because of the RF gain). The system designer must be cognizant of this large signal limitation. When designing LANs or other closed systems where transmission levels are high ...

1 Introduction and Bioamplifier Requirements Full

... fabrication process give rise to large fluctuations in the amplifying properties of the devices used to construct the amplifier. This gives rise to varition in the amplifer gain, A, which can only be overcome by more advanced design techniques such as the use of negative feedback. VDD ...

... fabrication process give rise to large fluctuations in the amplifying properties of the devices used to construct the amplifier. This gives rise to varition in the amplifer gain, A, which can only be overcome by more advanced design techniques such as the use of negative feedback. VDD ...

MAX5168 32-Channel Sample/Hold Amplifier with a Single Multiplexed Input General Description

... The MAX5168 contains an output buffer for each multiplexer channel (32 total), so the hold capacitor sees a high-impedance input that reduces the droop rate. The capacitor droops at 1mV/s (typ) while in hold mode. The buffer also provides a low output impedance; however, the device contains output r ...

... The MAX5168 contains an output buffer for each multiplexer channel (32 total), so the hold capacitor sees a high-impedance input that reduces the droop rate. The capacitor droops at 1mV/s (typ) while in hold mode. The buffer also provides a low output impedance; however, the device contains output r ...

service manual - Audio Lab of Ga

... The driver circuit consists of Q1 through Q12 and is located on the Filter/Driver board. The driver circuit has a DC offset adjustment, R50, which should be set at 0 Vdc +/- 50mVdc. This can be measured across the + and - output wires (white & black respectively) from the amp with power on and no si ...

... The driver circuit consists of Q1 through Q12 and is located on the Filter/Driver board. The driver circuit has a DC offset adjustment, R50, which should be set at 0 Vdc +/- 50mVdc. This can be measured across the + and - output wires (white & black respectively) from the amp with power on and no si ...

LT1187 - Low Power Video Difference Amplifier

... and Q1 (or Q2) turns off. Therefore the maximum input swing is 380mVP or 760mVP-P. The second differential pair, Q3 and Q4, is running at slightly larger current so that when the first input stage limits, the second stage remains biased to maintain the feedback. Occasionally it is necessary to handle ...

... and Q1 (or Q2) turns off. Therefore the maximum input swing is 380mVP or 760mVP-P. The second differential pair, Q3 and Q4, is running at slightly larger current so that when the first input stage limits, the second stage remains biased to maintain the feedback. Occasionally it is necessary to handle ...

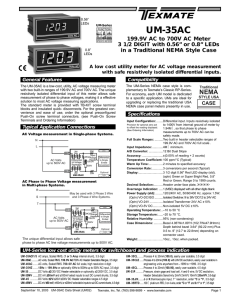

NEMA

... CN-PUSH/UM04 . . Connector: Push-on Terminal Block, 9 to 36V DC/12 to 24V AC . . . $18 CN-PUSH/UM05 . Connector: Push-on Terminal Block, 5V DC . . . . . . . . . . . . . . . $18 CN-UM/ANLGC . . Connector: Pinout Changer to match Analogic AN20M02 etc . . $30 OP-N4SEAL/UM . NEMA 4 lens cover for UM Ser ...

... CN-PUSH/UM04 . . Connector: Push-on Terminal Block, 9 to 36V DC/12 to 24V AC . . . $18 CN-PUSH/UM05 . Connector: Push-on Terminal Block, 5V DC . . . . . . . . . . . . . . . $18 CN-UM/ANLGC . . Connector: Pinout Changer to match Analogic AN20M02 etc . . $30 OP-N4SEAL/UM . NEMA 4 lens cover for UM Ser ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.