IOSR Journal of Electronics and Communication Engineering (IOSR-JECE) ISSN: , PP: 55-59 www.iosrjournals.org

... and construction. They can be studied and discussed easily, yet they still display the characteristics of multivalued elements. 2. Since 3 is the digit nearest to e = 2.718, ternary circuits will be more economical according to this measure. 3. Since 3 is not an integral power of 2, research on tern ...

... and construction. They can be studied and discussed easily, yet they still display the characteristics of multivalued elements. 2. Since 3 is the digit nearest to e = 2.718, ternary circuits will be more economical according to this measure. 3. Since 3 is not an integral power of 2, research on tern ...

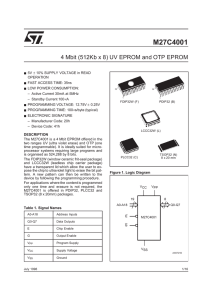

M27C4001 - EECS Instructional Support Group Home Page

... week to cause erasure when exposed to direct sunlight. If the M27C4001 is to be exposed to these types of lighting conditions for extended periods of time, it is suggested that opaque labels be put over the M27C4001 window to prevent unintentional erasure. The recommended erasure procedure for the M ...

... week to cause erasure when exposed to direct sunlight. If the M27C4001 is to be exposed to these types of lighting conditions for extended periods of time, it is suggested that opaque labels be put over the M27C4001 window to prevent unintentional erasure. The recommended erasure procedure for the M ...

AN-533: Applying 5B Series Backplanes and Mounting Cards

... ignored. Moving the jumpers to any other position in the two blocks enables decoding of the full six address bits; the exact position of the jumper determines address position for the backplane as shown in Table I. To use multiple backplanes in this manner, connect the corresponding I/O connector pi ...

... ignored. Moving the jumpers to any other position in the two blocks enables decoding of the full six address bits; the exact position of the jumper determines address position for the backplane as shown in Table I. To use multiple backplanes in this manner, connect the corresponding I/O connector pi ...

AD9748 数据手册DataSheet 下载

... Edge-triggered input latches and a 1.2 V temperaturecompensated band gap reference have been integrated to provide a complete monolithic DAC solution. The digital inputs support 3 V CMOS logic families. ...

... Edge-triggered input latches and a 1.2 V temperaturecompensated band gap reference have been integrated to provide a complete monolithic DAC solution. The digital inputs support 3 V CMOS logic families. ...

Anna University (Syllabus) V Semester (EEE) LINEAR

... The difference between the two preset input frequencies of Frequency Shift Keying (FSK) demodulator is called frequency shift. 21. What is frequency shift keying demodulation? The binary data which is shifted by a carrier frequency between two preset frequencies are retrieved by using Frequency Shif ...

... The difference between the two preset input frequencies of Frequency Shift Keying (FSK) demodulator is called frequency shift. 21. What is frequency shift keying demodulation? The binary data which is shifted by a carrier frequency between two preset frequencies are retrieved by using Frequency Shif ...

ADS5272 数据资料 dataSheet 下载

... Analog Input Common-Mode Range Differential Full-Scale Input Voltage Range ...

... Analog Input Common-Mode Range Differential Full-Scale Input Voltage Range ...

MAX7322 I C Port Expander with 4 Push-Pull Outputs and 4 Inputs

... address inputs AD2 and AD0 fully until the first I2C transmission. AD0 and AD2 initially appear to be connected to V+ or GND. This is important because the address selection determines the power-up logic state, and whether pullups are enabled. However, at powerup, the I2C SDA and SCL bus interface l ...

... address inputs AD2 and AD0 fully until the first I2C transmission. AD0 and AD2 initially appear to be connected to V+ or GND. This is important because the address selection determines the power-up logic state, and whether pullups are enabled. However, at powerup, the I2C SDA and SCL bus interface l ...

AD823 Dual 16 MHz, Rail-to-Rail FET Input Amplifier Data Sheet

... The AD823 is fabricated on the Analog Devices proprietary complementary bipolar (CB) process that enables the construction of PNP and NPN transistors with similar fTs in the 600 MHz to 800 MHz region. In addition, the process also features N-Channel JFETs, which are used in the input stage of the AD ...

... The AD823 is fabricated on the Analog Devices proprietary complementary bipolar (CB) process that enables the construction of PNP and NPN transistors with similar fTs in the 600 MHz to 800 MHz region. In addition, the process also features N-Channel JFETs, which are used in the input stage of the AD ...

DS92LV1224 30-66 MHz 10 Bit Bus LVDS

... or a data stream. The SYNC pattern sent by the Serializer consists of six ones and six zeros switching at the input clock rate. Note that the Deserializer LOCK output will remain high while its PLL locks to the incoming data or to SYNC patterns on the input. Step 2: The Deserializer PLL must synchro ...

... or a data stream. The SYNC pattern sent by the Serializer consists of six ones and six zeros switching at the input clock rate. Note that the Deserializer LOCK output will remain high while its PLL locks to the incoming data or to SYNC patterns on the input. Step 2: The Deserializer PLL must synchro ...

to this file: /unr15-25w

... maximum rating (10A) by 40% (typical) to 80% (maximum), the internal overcurrent detection circuit automatically shuts down the converter by discharging the soft-start circuit of the pulse width modulator (PWM). In this off state, which is similar to that achieved by pulling the On/Off Control low, ...

... maximum rating (10A) by 40% (typical) to 80% (maximum), the internal overcurrent detection circuit automatically shuts down the converter by discharging the soft-start circuit of the pulse width modulator (PWM). In this off state, which is similar to that achieved by pulling the On/Off Control low, ...

eg_op_guide - Center for Detectors

... registers. VDD_RST, VSS_RST, VDD_SEL, and VSS_SEL are the high and low rail supply lines for the reset and select (also referred to as “access” in this document) FETs. VTUB provides connection to the n-wells in the logic circuitry, as well as the high rail of the gate-protection circuitry, and must ...

... registers. VDD_RST, VSS_RST, VDD_SEL, and VSS_SEL are the high and low rail supply lines for the reset and select (also referred to as “access” in this document) FETs. VTUB provides connection to the n-wells in the logic circuitry, as well as the high rail of the gate-protection circuitry, and must ...

Digital Panel Meters Modular Indicator and Controller Type UDM40

... AC 1: 5A, 250VAC DC 12: 3A, 24VDC AC 15: 1,5A, 250VAC DC 13: 1,5A, 24VDC 4000 VRMS output to measuring input, 4000 VRMS output to power supply input. NPN transistor type VON 1.2 VDC/ max. 100 mA VOFF 30 VDC max. By means of opto-couplers 4000 VRMS output to measuring input 4000 VRMS output to power ...

... AC 1: 5A, 250VAC DC 12: 3A, 24VDC AC 15: 1,5A, 250VAC DC 13: 1,5A, 24VDC 4000 VRMS output to measuring input, 4000 VRMS output to power supply input. NPN transistor type VON 1.2 VDC/ max. 100 mA VOFF 30 VDC max. By means of opto-couplers 4000 VRMS output to measuring input 4000 VRMS output to power ...

ADS5273 数据资料 dataSheet 下载

... An integrated phase lock loop (PLL) multiplies the incoming ADC sampling clock by a factor of 12. This high-frequency LVDS clock is used in the data serialization and transmission process. The word output of each internal ADC is serialized and transmitted either MSB or LSB first. In addition to the ...

... An integrated phase lock loop (PLL) multiplies the incoming ADC sampling clock by a factor of 12. This high-frequency LVDS clock is used in the data serialization and transmission process. The word output of each internal ADC is serialized and transmitted either MSB or LSB first. In addition to the ...

Inverter Design Report

... Components placed on the sheet start with common default values. While these will often work well, they can be modified if the design requires. Transistors are defined by their channel widthto-length ratio, or W/L. Both transistors start with a W/L of 5/2. The pmos transistor is changed to a W/L of ...

... Components placed on the sheet start with common default values. While these will often work well, they can be modified if the design requires. Transistors are defined by their channel widthto-length ratio, or W/L. Both transistors start with a W/L of 5/2. The pmos transistor is changed to a W/L of ...

TS-64WDS - Communications Specialists

... radio set. This information is used by the TS-64WDS to determine transmit status. The PTT Output line is a FET that pulls to ground to key the transmitter during CTCSS transmission. To Install the PTT Input and PTT Output lines, cut the PTT line in the radio set at the microphone connector, and inse ...

... radio set. This information is used by the TS-64WDS to determine transmit status. The PTT Output line is a FET that pulls to ground to key the transmitter during CTCSS transmission. To Install the PTT Input and PTT Output lines, cut the PTT line in the radio set at the microphone connector, and inse ...

MAX113/MAX117 +3V, 400ksps, 4/8-Channel, 8-Bit ADCs with 1µA Power-Down _______________General Description

... In read mode, conversions and data access are controlled by the RD input (Figure 3). The comparator inputs track the analog input voltage for the duration of tACQ. A conversion is initiated by driving CS and RD low. With µPs that can be forced into a wait state, hold RD low until output data appears ...

... In read mode, conversions and data access are controlled by the RD input (Figure 3). The comparator inputs track the analog input voltage for the duration of tACQ. A conversion is initiated by driving CS and RD low. With µPs that can be forced into a wait state, hold RD low until output data appears ...

PCA9516A 1. General description 5-channel I

... It can also be used to run different buses at 5 V and 3.3 V or 400 kHz and 100 kHz buses where the 100 kHz bus is isolated when 400 kHz operation of the other bus is required. Two or more PCA9516As cannot be put in series. The PCA9516A design does not allow this configuration. Since there is no dire ...

... It can also be used to run different buses at 5 V and 3.3 V or 400 kHz and 100 kHz buses where the 100 kHz bus is isolated when 400 kHz operation of the other bus is required. Two or more PCA9516As cannot be put in series. The PCA9516A design does not allow this configuration. Since there is no dire ...

AD831 数据手册DataSheet 下载

... An integral low noise amplifier provides a single-ended voltage output and can drive such low impedance loads as filters, 50 amplifier inputs, and A/D converters. Its small signal bandwidth exceeds 200 MHz. A single resistor connected between pins OUT and FB sets its gain. The amplifier’s low dc o ...

... An integral low noise amplifier provides a single-ended voltage output and can drive such low impedance loads as filters, 50 amplifier inputs, and A/D converters. Its small signal bandwidth exceeds 200 MHz. A single resistor connected between pins OUT and FB sets its gain. The amplifier’s low dc o ...

MAX9632 36V, Precision, Low-Noise, Wide-Band Amplifier EVALUATION KIT AVAILABLE

... that is transformed into a short current pulse once it discharges through the device. The built-in protection circuit provides a current path around the op amp that prevents it from being damaged. The energy absorbed by the protection circuit is dissipated as heat. ESD protection is guaranteed up to ...

... that is transformed into a short current pulse once it discharges through the device. The built-in protection circuit provides a current path around the op amp that prevents it from being damaged. The energy absorbed by the protection circuit is dissipated as heat. ESD protection is guaranteed up to ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.