* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Inverter Design Report

Buck converter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Ground (electricity) wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Control system wikipedia , lookup

Two-port network wikipedia , lookup

Opto-isolator wikipedia , lookup

Power inverter wikipedia , lookup

Solar micro-inverter wikipedia , lookup

History of the transistor wikipedia , lookup

Current mirror wikipedia , lookup

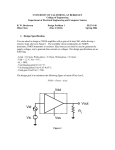

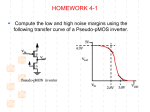

Inverter Design Report By Stan McVay Homework #5 Mentor Graphics #1 October 14, 2002 Table of Contents Introduction ......................................................................................................... 3 Inverter Theory of Operation.............................................................................. 3 Schematic Design with Design Architect ......................................................... 3 Digital Simulation with QuickSim II ................................................................... 5 Layout Design with IC Station ........................................................................... 5 Parameter Extraction .......................................................................................... 7 Analog Analysis with Accusim .......................................................................... 8 Conclusion .......................................................................................................... 9 Introduction The purpose of this project is to design an inverter circuit. This begins with a schematic level design and proceeds through layout and design verification. The software tools used are part of Mentor Graphics. An inverter is perhaps the simplest digital device. It has one input and one output. Whatever value is placed on the input, the opposite value is placed on the output. For example, a logic 1 on the input results in a logic 0 on the output. The reverse is also true: a logic 0 on the input results in a logic 1 on the output. A number of abbreviations and jargon will be used in this report. “VDD” refers to the power source of the circuit, and is analogous to logic 1. “Ground” is usually considered zero volts, and is also logic 0. The input and output ports are denoted “IN” and “OUT”, respectively. When discussing transistors, “nmos” may be used to mean “nmos transistor”. “Pmos” may be used similarly. Inverter Theory of Operation An inverter can be built using two transistors: one nmos transistor and one pmos transistor. The pmos is used to “pull up” the output port to a logic 1 when the input is a logic 0. Similarly, the nmos is used to “pull down” the output to a logic 0 when the input is a logic 1. The pmos transistor has four ports. The source and substrate are tied to the power connection, denoted VDD. The gate is connected to IN. The drain is tied to the drain of the nmos transistor and to OUT. With the source connected to VDD, the transistor is ready to turn on and supply current. The only other requirement is that the gate must be grounded, or logic 0. When the pmos turns on, current flows from VDD to OUT, with minimal resistance from the transistor. This causes OUT to be virtually the same voltage as VDD, or logic 1, but only when the gate is logic 0. When the gate is logic 1, the transistor is turned off, and appears as an open circuit. This means it has no meaningful effect on OUT. The nmos transistor also has four ports, but behaves in a different way. The source and substrate are tied to ground. The gate goes to IN, and the drain connects to the pmos drain and OUT. With the source grounded, the nmos is also ready to conduct current. Unlike the pmos, however, the nmos will only conduct current when the gate is logic 1. When this happens, current can flow from OUT to ground through the nmos. Since an open transistor has only minimal resistance, the voltage at OUT becomes close to ground, or logic 0. When the gate is logic 1, the nmos becomes as an open circuit. This pairing of nmos and pmos allows an inverter to function. When the gate is logic 1, the pmos turns off and the nmos ties OUT to ground, causing logic 0. Similarly, when the gate is logic 0, the nmos turns off and the pmos ties OUT to VDD, causing logic 1. Schematic Design with Design Architect The first step in the design process is to create a schematic-level representation of the circuit. This involves selecting the appropriate type and number of transistors, providing power and ground connections, and denoting all input and output ports. This inverter circuit design was created using a tool called Design Architect (DA). This is part of the Mentor Graphics suite. DA allows the user to select components from convenient libraries and arrange them graphically to create the circuit. Once created, this circuit design can be used in other Mentor Graphics applications to confirm the circuit’s performance and serve as a guide for layout. The design begins by creating a “sheet” in DA. This appears as a blank grid on the screen. Components can be dragged onto this sheet to form the circuit. For the inverter, components from the “ADK” library are used. These include the nmos and pmos transistors, power and ground connections, and the input and output ports. Once these six components are placed on the sheet, they can be arranged to suit the design. In this case, the power connection is placed on top. Moving downward, the pmos is next, followed by the nmos and ground. The input is placed to the left of the two transistors, and the output is placed to the right. When the components are arranged correctly, they are wired together using a tool in DA. This creates virtual connections used in the circuit simulations. The pmos source and substrate pins are thus wired to VDD, and the drain wired to the nmos drain and OUT. The nmos source and substrate are wired to ground. IN is wired to the gates of both transistors. Figure 1 - Completed Inverter Schematic Components placed on the sheet start with common default values. While these will often work well, they can be modified if the design requires. Transistors are defined by their channel widthto-length ratio, or W/L. Both transistors start with a W/L of 5/2. The pmos transistor is changed to a W/L of 10/2. This widens the transistor channel so that more current can flow. This is useful for powering, or driving, whatever might be connected to the output of the inverter. Design Architect provides another useful function by checking the finished schematic for any errors, such as unconnected pins. The check passed for this circuit. When this step is complete, the schematic design is done, though a couple of followup steps remain. The first is the creation of a symbol for the circuit. When using inverters in a higher-level logic design, it would be inconvenient to repeat the above steps for every inverter. Instead, a symbol can be created to represent the circuit design. This symbol can then be used repeatedly throughout future designs. The second is the creation of a viewpoint. This is a description of the circuit that will be used by other programs to simulate the circuit design. This is done from the terminal window after the design is completed and checked. Digital Simulation with QuickSim II After the schematic design is completed, the circuit functionality can be tested using QuickSim II. This allows direct manipulation of the inputs, and tracking of the resulting outputs, of a circuit previously designed in Design Architect. Once QuickSim had started, a copy of the design schematic was displayed. A test signal was then applied to the input, IN. This was done by selecting IN from the schematic and using the “Add Force” command from the Stimulus menu. A short square wave was added to the input pin. This signal tested the output for both input values, 0 and 1. Next, the value of OUT was observed. Both the input and output pins were selected and the Trace function was chosen from the main Quicksim palette. This opened a new window in Quicksim that displayed both signals on the Y-axis and time on the X-axis. Finally, the Run command was chosen from the palette, and a time interval of 50 ns was specified. The Trace window now showed the square wave applied to IN. Also shown was the response on OUT. As expected, the value of OUT was the inverse of IN. This confirmed the basic digital operation of the circuit. The collected data was saved as “inv_results_1”. Figure 2 - Successful Trace Layout Design with IC Station Since the same layout could be used to produce silicon using any number of technologies, the dimensions in the layout are in terms of L. L is defined as one-half the minimum polysilicon gate width. By default, IC Station uses a grid size of 1Lx1L. This doesn’t allow centering of objects of even and odd dimensions, so the grid size was changed to 0.5Lx0.5L. In its arrangement of parts, the layout for this circuit is similar to the schematic. From top to bottom it contains VDD, the pmos transistor, the nmos transistor, and ground. In between the two transistors and set to each side are the input and output ports. The layout, however, contains a number of elements that were not present in the schematic. The nmos transistor was drawn first. An active region layer of size 15Lx5L was defined, situated horizontally. Next a 2Lx9L polysilicon layer was drawn, bisecting and overlapping the active region. Two contact-to-active points of 2Lx2L were then drawn on either side of the active region. The left contact was the source, the right contact the drain. A 1.5L width of active region surrounded these contacts on their outer 3 sides, and a 3L gap was present between the contacts and poly layer. Finally, a 19Lx9L N-Plus-Select layer was drawn around the active region with a separation of 2L. The transistor’s W/L ratio is determined by its active region height and gate width. In this case the ratio is 5/2, just as specified in the schematic. Next came the nmos substrate tap. A second active region of 5Lx5L was drawn, and surrounded by a 19Lx9L P-Plus-Select layer. Another 2Lx2L contact-to-active was centered inside the active region. The active region was placed to the left of the P-Plus-Select area, with 2L spacing on three sides. This entire group was then moved below the nmos, with the select regions aligned. This put the tap contact directly below the nmos source contact. The space between the two select regions was 0.5L. Metal layers were then added to provide connections. A 19Lx5L strip of Metal1 was placed across the length of the substrate tap P-Plus-Select region. This would act as the ground connection for the circuit. A 4L-wide strip of Metal1 was then placed between the nmos source contact and the first Metal1 layer. A 1L overlap was provided around the source contact. With the nmos transistor and substrate tap complete, next came the pmos transistor. With a W/L ratio of 10/2, the pmos active region was 15Lx10L. Four contact-to-active layers were added, of 2Lx2L each. One was placed in each corner of the active region, with 1.5L spacing between the contact and active region edge. Then a 2Lx14L polysilicon layer was added, bisecting and overlapping the active region. A P-Plus-Select area was then drawn around the pmos active region, with 2L spacing on each side. Pmos transistors need to be placed in an N-Well, so instead of a substrate tap it requires a well tap. This is a mirror image of the substrate tap described above, except that it has a N-PlusSelect region instead of P-Plus-Select. This well tap was situated above the pmos, with 0.5L spacing between the select regions. A Metal1 layer 19Lx5L in size was placed across the NPlus-Select region, with another connecting to the two source contacts of the pmos. This acts as the VDD connection. Finally, a N-Well layer was created surrounding the pmos and well tap, with 6L spacing between the N-Well edge and the active regions. The contents of the N-Well were then placed above the nmos group, with the poly gates of the transistors aligned. Space was left to create a distance of 50L between the upper edge of the VDD metal and the lower edge of the ground metal. A new poly layer was then added to connect the two gate polys, with a wider area to contain a contact-to-poly of 2Lx2L. This was then surrounded by a Metal1 layer with 1L spacing on each side. This contact would become the IN port. The OUT port is created by placing a Metal 1 layer over the two pmos drain contacts and the nmos drain contact. Some finishing steps were then required. To define IN and OUT in terms of the schematic design, the Connectivity>Port>Make Port toolbar item is used. These provide the virtual connection between the schematic and the layout. Similarly, the VDD and ground rails are defined using the Objects>Make>Port toolbar item. To make the layout easier to read at a glance, text is added labelling IN, OUT, VDD, and ground. The cell origin was then redefined to the lower-left corner of the ground rail. Figure 3 - Completed Inverter Layout Finally, two checks are required to ensure the layout was done properly. The first, Design Rules Checker (DRC), is used to verify that the various spacing and size rules are followed in the layout. This was run several times as the layout design progressed, to catch mistakes as they were made. Once the layout was complete, the Layout Vs Schematic (LVS) check was run to compare the layout with the source schematic. Both of these checks passed, so the layout was complete. Parameter Extraction Quicksim was able to verify basic digital functionality, but did not provide detailed analog information about the circuit. IC Station is capable of deriving parasitic values for the layout, enabling an in-depth analog simulation to be performed later by Accusim. The first operation is the “lumped extraction”, which averages the varying parasitics throughout a given node. This was done through the IC Extract(M) pallet item. The window options were entered as specified in the tutorial. The results were very close to the example given in the tutorial. This seems reasonable, as there will no doubt be slight variations in this layout. The second extraction if for distributed parameters. Also done using the IC Extract (M) pallet, the results again were close if not exactly the same as in the tutorial. Analog Analysis with Accusim Once the lumped and distributed extractions are complete, Accusim can be used to perform an analog analysis of the circuit. This provides another confirmation of the basic functionality, but more importantly such data as rise and fall times for the inverter output. The analog trace is shown below. Like the trace in Quicksim, it shows the correct operation of the inverter. It also hints at the non-ideal characteristic of the device. Rather than sharp edges at the transitions, the change in state is clearly gradual. Figure 4 - Analog Trace Accusim also determines rise and fall times for the inverter, which are shown below. These values are considerably different from the values given in the tutorial. The design steps were reviewed, but no discrepancies were found. The values found for this circuit were roughly ¼ the value found in the tutorial. Figure 5 - Rise and Fall Times for OUT Conclusion With the exception of the final rise and fall times, the design of this inverter conformed well to the tutorial. A number of problems arose, but most of these were due to user error and a significant learning curve with Mentor Graphics software. Despite the rise/fall time discrepancy, the inverter does appear to perform as required. The rise and fall times are actually better than in the tutorial, though what caused the difference is unknown.