Triggering on MIL-STD 1553 Signals

... Signal transitions may or may not occur near bit time boundaries. ...

... Signal transitions may or may not occur near bit time boundaries. ...

NPIC6C595 1. General description Power logic 8-bit shift register; open-drain outputs

... Fig 13. Test circuit and waveform for measuring reverse recovery current ...

... Fig 13. Test circuit and waveform for measuring reverse recovery current ...

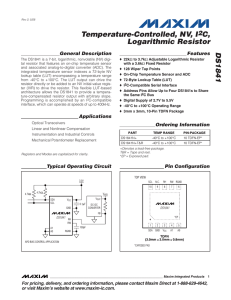

DS1841 - Maxim Part Number Search

... slave address. Conversely, address pins tied to VCC result in a 1 in the corresponding bit positions. For example, the DS1841’s slave address byte is 50h when A0 and A1 pins are grounded. I2C communication is described in detail in the I 2 C Serial Interface Description section. ...

... slave address. Conversely, address pins tied to VCC result in a 1 in the corresponding bit positions. For example, the DS1841’s slave address byte is 50h when A0 and A1 pins are grounded. I2C communication is described in detail in the I 2 C Serial Interface Description section. ...

73S8010C Smart Card Interface DATA SHEET

... can be externally adjusted True over-current detection (150 mA max.) 1 card detection input Auxiliary I/O lines, for C4 / C8 contact signals ...

... can be externally adjusted True over-current detection (150 mA max.) 1 card detection input Auxiliary I/O lines, for C4 / C8 contact signals ...

ch4

... • Addresses: 6 bytes • if adapter receives frame with matching destination address, or with broadcast address (e.g. ARP packet), it passes data in frame to network layer protocol • otherwise, adapter discards frame • Type: indicates higher layer protocol (mostly IP but others possible, e.g., Novell ...

... • Addresses: 6 bytes • if adapter receives frame with matching destination address, or with broadcast address (e.g. ARP packet), it passes data in frame to network layer protocol • otherwise, adapter discards frame • Type: indicates higher layer protocol (mostly IP but others possible, e.g., Novell ...

ADS5270 数据资料 dataSheet 下载

... Analog Input Common-Mode Range Differential Full-Scale Input Voltage Range ...

... Analog Input Common-Mode Range Differential Full-Scale Input Voltage Range ...

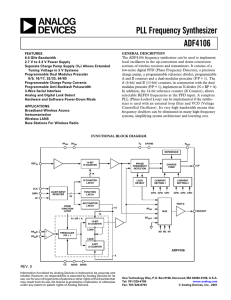

ADF4106

... Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise ...

... Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise ...

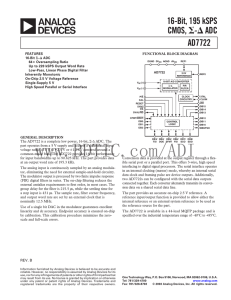

16-Bit, 195 kSPS CMOS, AD7722 -

... Conversion data is provided at the output register through a flexible serial port or a parallel port. This offers 3-wire, high speed interfacing to digital signal processors. The serial interface operates in an internal clocking (master) mode, whereby an internal serial data clock and framing pulse ...

... Conversion data is provided at the output register through a flexible serial port or a parallel port. This offers 3-wire, high speed interfacing to digital signal processors. The serial interface operates in an internal clocking (master) mode, whereby an internal serial data clock and framing pulse ...

CS610 Final term MAGA file.. all paperz are in 1 file..pages 1 to 42

... We want to TX the binary data unit 1100001 Adding together the number of 1’s gives us 3, an odd number Before TX, we pass the data unit through a parity generator, which counts the 1’s and appends the parity bit (1) to the end The total number of 1’s is now 4, an even number The system now transfers ...

... We want to TX the binary data unit 1100001 Adding together the number of 1’s gives us 3, an odd number Before TX, we pass the data unit through a parity generator, which counts the 1’s and appends the parity bit (1) to the end The total number of 1’s is now 4, an even number The system now transfers ...

MXL1543 +5V Multiprotocol, 3Tx/3Rx, Software- Selectable Clock/Data Transceivers General Description

... and the MXL1344A, form a complete software-selectable data terminal equipment (DTE) or data communication equipment (DCE) interface port that supports the V.28 (RS-232), V.10/V.11 (RS-449/V.36, EIA-530, EIA530A, X.21), and V.35 protocols. The MXL1543 transceivers carry the high-speed clock and data ...

... and the MXL1344A, form a complete software-selectable data terminal equipment (DTE) or data communication equipment (DCE) interface port that supports the V.28 (RS-232), V.10/V.11 (RS-449/V.36, EIA-530, EIA530A, X.21), and V.35 protocols. The MXL1543 transceivers carry the high-speed clock and data ...

Simulation of 3D Laser Radar Systems

... the three occurring simultaneously constitute a Poisson process with a mean rate of creating primary electrons given by the sum of the three individual mean rates. The APD is biased into Geiger mode for a particular time interval, or gate, on every laser pulse. The detector fires in response to the ...

... the three occurring simultaneously constitute a Poisson process with a mean rate of creating primary electrons given by the sum of the three individual mean rates. The APD is biased into Geiger mode for a particular time interval, or gate, on every laser pulse. The detector fires in response to the ...

Evaluates: DS1854/DS1857/DS1858/DS1859 Fiber Optic Monitor and Control Evaluation Kit General Description Features

... device, some of the pins will be analog inputs or outputs, so be advised that jumper settings should be monitored carefully to prevent connecting an output to VCC or GND, and to prevent the analog input from being connected to an invalid level. For example, the first jumper for a DS1854 is OUT1, whi ...

... device, some of the pins will be analog inputs or outputs, so be advised that jumper settings should be monitored carefully to prevent connecting an output to VCC or GND, and to prevent the analog input from being connected to an invalid level. For example, the first jumper for a DS1854 is OUT1, whi ...

International Technical Support Organization High

... When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you. Copyright International Business Machines Corporation 1992 1993 1995. All rights reserved. Note to U.S. Government ...

... When you send information to IBM, you grant IBM a non-exclusive right to use or distribute the information in any way it believes appropriate without incurring any obligation to you. Copyright International Business Machines Corporation 1992 1993 1995. All rights reserved. Note to U.S. Government ...

MAX11108 Tiny, 2.1mm x 1.6mm, 3Msps, Low-Power, Serial 12-Bit ADC EVALUATION KIT AVAILABLE

... full rate when driven by a 48MHz clock. The conversion result appears at DOUT, MSB first, with a leading zero followed by the 12-bit result. A 12-bit result is followed by two trailing zeros (see Figure 1). The device features a dedicated reference input (REF). The input signal range for AIN is defi ...

... full rate when driven by a 48MHz clock. The conversion result appears at DOUT, MSB first, with a leading zero followed by the 12-bit result. A 12-bit result is followed by two trailing zeros (see Figure 1). The device features a dedicated reference input (REF). The input signal range for AIN is defi ...

MAX3291/MAX3292 RS-485/RS-422 Transceivers with Preemphasis for High-Speed, Long-Distance Communication ________________General Description

... logic-high output if the input is open circuit. A 1/4-unitload receiver input impedance allows up to 128 transceivers on the bus. Inter-symbol interference (ISI) causes significant problems for UARTs if the total RS-485/RS-422 signal jitter becomes 10% or more of the baud period. ISI is caused by th ...

... logic-high output if the input is open circuit. A 1/4-unitload receiver input impedance allows up to 128 transceivers on the bus. Inter-symbol interference (ISI) causes significant problems for UARTs if the total RS-485/RS-422 signal jitter becomes 10% or more of the baud period. ISI is caused by th ...

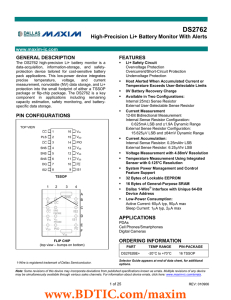

DS2762 High-Precision Li+ Battery Monitor With Alerts GENERAL DESCRIPTION FEATURES

... capacity estimation, safety monitoring, and battery-specific data storage. Through its 1-Wire interface, the DS2762 gives the host system read/write access to status and control registers, instrumentation registers, and general-purpose data storage. Each device has a unique factory-programmed 64-bit ...

... capacity estimation, safety monitoring, and battery-specific data storage. Through its 1-Wire interface, the DS2762 gives the host system read/write access to status and control registers, instrumentation registers, and general-purpose data storage. Each device has a unique factory-programmed 64-bit ...

MAX3040–MAX3045 ±10kV ESD-Protected

... IEC 1000-4-4 Electrical Fast Transient/Burst (EFT/B) is an immunity test for the evaluation of electrical and electronic systems during operating conditions. The test was adapted for evaluation of integrated circuits with power applied. Repetitive fast transients with severe pulsed EMI were applied ...

... IEC 1000-4-4 Electrical Fast Transient/Burst (EFT/B) is an immunity test for the evaluation of electrical and electronic systems during operating conditions. The test was adapted for evaluation of integrated circuits with power applied. Repetitive fast transients with severe pulsed EMI were applied ...

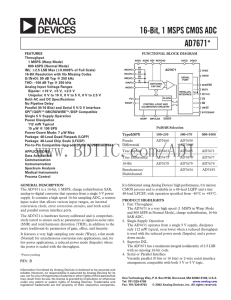

AD7671 数据手册DataSheet下载

... analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and both serial and parallel system interface ports. The AD7671 i ...

... analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and both serial and parallel system interface ports. The AD7671 i ...

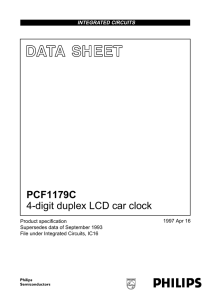

PCF1179CT

... is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Where application information is given, it is advisory and does not form part of the specification. LIFE SUPPORT APPLICATIONS These products are not designed for use in life suppor ...

... is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Where application information is given, it is advisory and does not form part of the specification. LIFE SUPPORT APPLICATIONS These products are not designed for use in life suppor ...

4-digit duplex LCD car clock

... is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Where application information is given, it is advisory and does not form part of the specification. LIFE SUPPORT APPLICATIONS These products are not designed for use in life suppor ...

... is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Where application information is given, it is advisory and does not form part of the specification. LIFE SUPPORT APPLICATIONS These products are not designed for use in life suppor ...

Dual 10-Bit TxDAC+ with 2 AD9761 ®

... CMOS DAC. The AD9761 has been developed specifically for use in wide bandwidth communication applications (e.g., spread spectrum) where digital I and Q information is being processed during transmit operations. It integrates two 10-bit, 40 MSPS DACs, dual 2 interpolation filters, a voltage referenc ...

... CMOS DAC. The AD9761 has been developed specifically for use in wide bandwidth communication applications (e.g., spread spectrum) where digital I and Q information is being processed during transmit operations. It integrates two 10-bit, 40 MSPS DACs, dual 2 interpolation filters, a voltage referenc ...

c. omflip - PALMS - Princeton University

... The CROSS instruction defined in [6] is based on the Benes network. A Benes network consists of a butterfly network followed by an inverse butterfly network. An n-bit butterfly network consists of log(n) stages. In each stage, n bits are divided into n/2 pairs. Two bits in a pair can go to the same ...

... The CROSS instruction defined in [6] is based on the Benes network. A Benes network consists of a butterfly network followed by an inverse butterfly network. An n-bit butterfly network consists of log(n) stages. In each stage, n bits are divided into n/2 pairs. Two bits in a pair can go to the same ...

BDTIC www.BDTIC.com/infineon Application Note No. 018

... Improved stabilization behaviour versus temperature and reduced variation in amplifier performance due to the device‘s Beta (current gain) distribution can be achieved by using an active bias circuit. Such a circuit is available as a single device from Infineon - BCR400. For further information plea ...

... Improved stabilization behaviour versus temperature and reduced variation in amplifier performance due to the device‘s Beta (current gain) distribution can be achieved by using an active bias circuit. Such a circuit is available as a single device from Infineon - BCR400. For further information plea ...