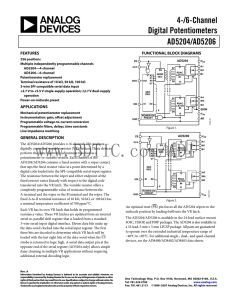

AD5204: 数据手册DataSheet 下载

... Each VR has its own VR latch that holds its programmed resistance value. These VR latches are updated from an internal serial-to-parallel shift register that is loaded from a standard 3-wire serial-input digital interface. Eleven data bits make up the data-word clocked into the serial input register ...

... Each VR has its own VR latch that holds its programmed resistance value. These VR latches are updated from an internal serial-to-parallel shift register that is loaded from a standard 3-wire serial-input digital interface. Eleven data bits make up the data-word clocked into the serial input register ...

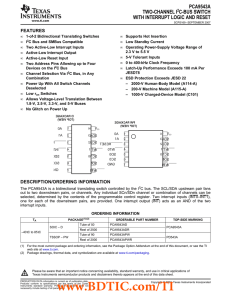

PCA9543A 数据资料 dataSheet 下载

... Bit 4 and Bit 5 of the control register correspond to the INT0 and INT1 inputs of the PCA9543A, respectively. Therefore, if an interrupt is generated by any device connected to channel 1, the state of the interrupt inputs is loaded into the control register when a read is accomplished. Likewise, an ...

... Bit 4 and Bit 5 of the control register correspond to the INT0 and INT1 inputs of the PCA9543A, respectively. Therefore, if an interrupt is generated by any device connected to channel 1, the state of the interrupt inputs is loaded into the control register when a read is accomplished. Likewise, an ...

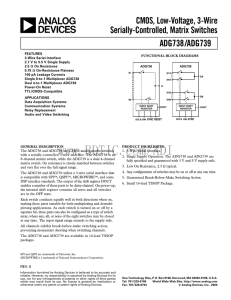

a CMOS, Low-Voltage, 3-Wire Serially-Controlled, Matrix Switches ADG738/ADG739

... GENERAL DESCRIPTION ...

... GENERAL DESCRIPTION ...

Capacitance - La Salle University

... plate, changing its capacitance, and hence changes the amount of charge the plates can hold for a given voltage. The keyboard circuitry detects this change and sends the appropriate information (interrupt request and ASCII code) to the CPU. PHY 202 (Blum) ...

... plate, changing its capacitance, and hence changes the amount of charge the plates can hold for a given voltage. The keyboard circuitry detects this change and sends the appropriate information (interrupt request and ASCII code) to the CPU. PHY 202 (Blum) ...

Risks Not Using IPSec

... VPN is more economical than traditional Intranet, while the tunneling and encryption technology of VPN guaranteed same level of integrity and security on data transmission among offices. The topological design of Intranet is more flexible with Intranet VPN. It is also easier and faster for a company ...

... VPN is more economical than traditional Intranet, while the tunneling and encryption technology of VPN guaranteed same level of integrity and security on data transmission among offices. The topological design of Intranet is more flexible with Intranet VPN. It is also easier and faster for a company ...

Big Picture Lab 4 - University of Massachusetts Amherst

... ECE 354 © Moritz 2009, some slides modified from Koren, Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 ...

... ECE 354 © Moritz 2009, some slides modified from Koren, Burleson, UMass and Wolf, Computers as Components, Morgan Kaufman, 2005 ...

电流检测放大器系列ADM1192 数据手册DataSheet 下载

... This is an absolute value to be used when converting ADC codes to current readings; any inaccuracy in this value is factored into absolute current accuracy values (see the specifications for the Current Sense Absolute Accuracy parameter). ...

... This is an absolute value to be used when converting ADC codes to current readings; any inaccuracy in this value is factored into absolute current accuracy values (see the specifications for the Current Sense Absolute Accuracy parameter). ...

Chapter 6: The Transport Layer

... CPU speed is more important than network speed Reduce packet count to reduce software overhead Minimize context switches Minimize copying You can buy more bandwidth but not lower delay Avoiding congestion is better than recovering from it – Avoid timeouts ...

... CPU speed is more important than network speed Reduce packet count to reduce software overhead Minimize context switches Minimize copying You can buy more bandwidth but not lower delay Avoiding congestion is better than recovering from it – Avoid timeouts ...

ADF4360-3 Integrated Synthesizer and VCO (Rev. D)

... The dual-modulus prescaler (P/P + 1), along with the A and B counters, enables the large division ratio, N, to be realized (N = BP + A). The dual-modulus prescaler, operating at CML levels, takes the clock from the VCO and divides it down to a manageable frequency for the CMOS A and B counters. The ...

... The dual-modulus prescaler (P/P + 1), along with the A and B counters, enables the large division ratio, N, to be realized (N = BP + A). The dual-modulus prescaler, operating at CML levels, takes the clock from the VCO and divides it down to a manageable frequency for the CMOS A and B counters. The ...

MAX13170E +5V Multiprotocol, 3Tx/3Rx, Software- Selectable Clock/Data Transceiver General Description

... Short-Circuit Duration to GND...............................Continuous ...

... Short-Circuit Duration to GND...............................Continuous ...

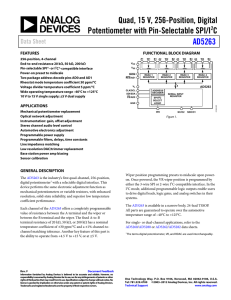

AD5263 (Rev. E)

... either the 3-wire SPI or 2-wire I2C-compatible interface. In the I2C mode, additional programmable logic outputs enable users to drive digital loads, logic gates, and analog switches in their systems. The AD5263 is available in a narrow body, 24-lead TSSOP. All parts are guaranteed to operate over t ...

... either the 3-wire SPI or 2-wire I2C-compatible interface. In the I2C mode, additional programmable logic outputs enable users to drive digital loads, logic gates, and analog switches in their systems. The AD5263 is available in a narrow body, 24-lead TSSOP. All parts are guaranteed to operate over t ...

PDF

... A Cold Load Pickup feature shall be provided for use in restoring service after an extended outage. This feature shall transfer operation from the normally programmed phase to ground TCC's to separately programmable TCC's for a programmable time of 1 to 60 seconds. The feature shall be programmable ...

... A Cold Load Pickup feature shall be provided for use in restoring service after an extended outage. This feature shall transfer operation from the normally programmed phase to ground TCC's to separately programmable TCC's for a programmable time of 1 to 60 seconds. The feature shall be programmable ...

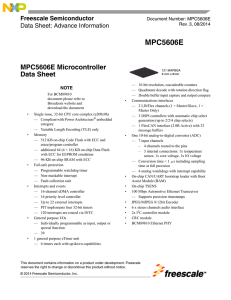

MPC5606E Microcontroller Data Sheet

... connecting a 25 MHz crystal between these two pins or by driving XTALI with an external 25 MHz clock. when using a crystal, connect a loading capacitor from each pin to GND. ...

... connecting a 25 MHz crystal between these two pins or by driving XTALI with an external 25 MHz clock. when using a crystal, connect a loading capacitor from each pin to GND. ...

Low Power, Buffered 24-Bit Sigma-Delta ADC AD7791

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

PI6C5946004

... It is suggested to add pull-up=4.7k and pull-down=1k for LVCMOS pins even though they have internal pull-up/down but with much higher value (>=50k) for higher design reliability. ...

... It is suggested to add pull-up=4.7k and pull-down=1k for LVCMOS pins even though they have internal pull-up/down but with much higher value (>=50k) for higher design reliability. ...

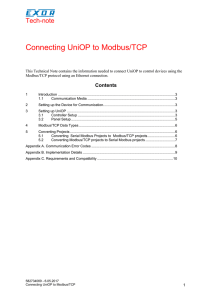

Connecting UniOP to Modbus/TCP

... to UniOP that it is allowed to access multiple data items at once resulting in greater display refresh ratio. Selecting the “Generic ModbusTCP - no data blocks” will force the UniOP to access single data item only per communication session. This will, of course, slow down the display refresh ratio, ...

... to UniOP that it is allowed to access multiple data items at once resulting in greater display refresh ratio. Selecting the “Generic ModbusTCP - no data blocks” will force the UniOP to access single data item only per communication session. This will, of course, slow down the display refresh ratio, ...

Collection Tree Protocol

... the timings for routing and forwarding packets. This paper describes and evaluates the algorithms and mechanisms that one particular implementation, called CTP Noe, uses. In addition to incorporating adaptive beaconing and datapath validation, CTP Noe includes additional mechanisms and algorithms to ...

... the timings for routing and forwarding packets. This paper describes and evaluates the algorithms and mechanisms that one particular implementation, called CTP Noe, uses. In addition to incorporating adaptive beaconing and datapath validation, CTP Noe includes additional mechanisms and algorithms to ...

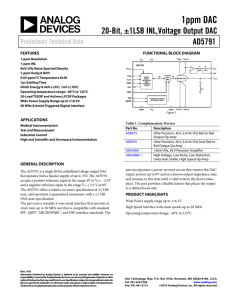

Rev. PrG

... Positive analog supply connection. A voltage in the range of 7.5 V to 16.5 V. can be connected VDD should be decoupled to AGND. Active Low Reset Pin. Asserting this pin will return the AD5791 to its power on status. Active Low input. Asserting this pin sets the DAC register to a user defined value ( ...

... Positive analog supply connection. A voltage in the range of 7.5 V to 16.5 V. can be connected VDD should be decoupled to AGND. Active Low Reset Pin. Asserting this pin will return the AD5791 to its power on status. Active Low input. Asserting this pin sets the DAC register to a user defined value ( ...

Underground Sensor Networks: Research Challenges

... Metrics, like energy, delay etc., form a cost function which is then minimized in previous work. Choice of the weights for these metrics are done heuristically; However, they are subject to dynamic network conditions, thus, more research is needed!! IFA’2007 ...

... Metrics, like energy, delay etc., form a cost function which is then minimized in previous work. Choice of the weights for these metrics are done heuristically; However, they are subject to dynamic network conditions, thus, more research is needed!! IFA’2007 ...

4.2 TCP Handoff implementation - The Linux Virtual Server Project

... packet is modified by FE, then is forwarded to BE. In BE, this connection is reconstructed. BE will send ACK directly to client, bypassing FE. The successive packets will be forwarded to BE in IP layer by FE. Responses will be sent directly to client by BE. The system process of 0.3 release is rough ...

... packet is modified by FE, then is forwarded to BE. In BE, this connection is reconstructed. BE will send ACK directly to client, bypassing FE. The successive packets will be forwarded to BE in IP layer by FE. Responses will be sent directly to client by BE. The system process of 0.3 release is rough ...