ERROR DETECTION AND CORRECTION

... decimal value of C gives the position of the bit in error. The error can then be corrected by complementing the corresponding bit. Note that an error can occur in the data or in one of the parity bits. The Hamming code can be used for data words of any length. In general, for k check bits and n data ...

... decimal value of C gives the position of the bit in error. The error can then be corrected by complementing the corresponding bit. Note that an error can occur in the data or in one of the parity bits. The Hamming code can be used for data words of any length. In general, for k check bits and n data ...

16-, 14-, 12-Bit, Six-Channel, Simultaneous

... The ADS855x contains six low-power, 16-, 14-, or 12bit, successive approximation register (SAR) based analog-to-digital converters (ADCs) with true bipolar inputs. Each channel contains a sample-and-hold circuit that allows simultaneous high-speed multichannel signal acquisition. The ADS855x support ...

... The ADS855x contains six low-power, 16-, 14-, or 12bit, successive approximation register (SAR) based analog-to-digital converters (ADCs) with true bipolar inputs. Each channel contains a sample-and-hold circuit that allows simultaneous high-speed multichannel signal acquisition. The ADS855x support ...

4.2 TCP Handoff implementation - The Linux Virtual Server Project

... packet is modified by FE, then is forwarded to BE. In BE, this connection is reconstructed. BE will send ACK directly to client, bypassing FE. The successive packets will be forwarded to BE in IP layer by FE. Responses will be sent directly to client by BE. The system process of 0.3 release is rough ...

... packet is modified by FE, then is forwarded to BE. In BE, this connection is reconstructed. BE will send ACK directly to client, bypassing FE. The successive packets will be forwarded to BE in IP layer by FE. Responses will be sent directly to client by BE. The system process of 0.3 release is rough ...

74LVT244A; 74LVTH244A 1. General description 3.3 V octal buffer/line driver; 3-state

... The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com. ...

... The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com. ...

DAC7811 数据资料 dataSheet 下载

... The DAC7811 has a 3-wire serial interface (SYNC, SCLK, and SDIN), which is compatible with SPI, QSPI, and MICROWIRE interface standards as well as most Digital Signal Processor (DSP) devices. See the Serial Write Operation timing diagram (Figure 28) for an example of a typical write sequence. The wr ...

... The DAC7811 has a 3-wire serial interface (SYNC, SCLK, and SDIN), which is compatible with SPI, QSPI, and MICROWIRE interface standards as well as most Digital Signal Processor (DSP) devices. See the Serial Write Operation timing diagram (Figure 28) for an example of a typical write sequence. The wr ...

ADN8102 - Analog Devices

... The ADN8102 is controlled through toggle pins, an I2C® control interface that provides more flexible control, or a combination of both. Every channel implements an asynchronous path supporting dc to 3.75 Gbps NRZ data, fully independent of other channels. The ADN8102 has low latency and very low cha ...

... The ADN8102 is controlled through toggle pins, an I2C® control interface that provides more flexible control, or a combination of both. Every channel implements an asynchronous path supporting dc to 3.75 Gbps NRZ data, fully independent of other channels. The ADN8102 has low latency and very low cha ...

Review, Performance Metrics, Cont…

... monitors signal of a user from multiple base stations and chooses best version of signal at any time Self-jamming is a problem: because spreading sequences of different users are not exactly orthogonal —When despreading, other users can Contribute significantly to receiver decision statistic EETS 8 ...

... monitors signal of a user from multiple base stations and chooses best version of signal at any time Self-jamming is a problem: because spreading sequences of different users are not exactly orthogonal —When despreading, other users can Contribute significantly to receiver decision statistic EETS 8 ...

Institutionen för systemteknik Department of Electrical Engineering Implementation of a VBR MPEG-stream

... header with the value 0x47. Following are a number of flags and the Packet Identifier (PID). When using CBR streams, empty packets are included as described earlier; such an empty packet has the PID set to 0x1FFF, which is reserved for null packets. This way CBR streams can easily be converted to VB ...

... header with the value 0x47. Following are a number of flags and the Packet Identifier (PID). When using CBR streams, empty packets are included as described earlier; such an empty packet has the PID set to 0x1FFF, which is reserved for null packets. This way CBR streams can easily be converted to VB ...

Support for IEEE 1588™ Protocol in PowerQUICC and QorIQ

... The lower level driver interacts with the hardware on one end and higher level applications at the other. The higher level application, in this case, implements precision time protocol (PTP). This section discusses the IOCTLs implemented by a low level driver in Linux-based board support packages (B ...

... The lower level driver interacts with the hardware on one end and higher level applications at the other. The higher level application, in this case, implements precision time protocol (PTP). This section discusses the IOCTLs implemented by a low level driver in Linux-based board support packages (B ...

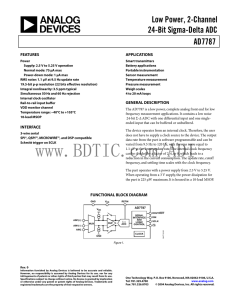

AD7895 5 V, 12-Bit, Serial 3.8 s, ADC in 8

... SOIC. The part contains a 3.8 µs successive approximation A/D converter, an on-chip track/hold amplifier, an on-chip clock and a high speed serial interface. Output data from the AD7895 is provided via a high speed, serial interface port. This two-wire serial interface has a serial clock input and a ...

... SOIC. The part contains a 3.8 µs successive approximation A/D converter, an on-chip track/hold amplifier, an on-chip clock and a high speed serial interface. Output data from the AD7895 is provided via a high speed, serial interface port. This two-wire serial interface has a serial clock input and a ...

Dynamic Flip-Flop Conversion to Tolerate

... To evaluate the efficiency of DFFC method, five benchmark circuits of ITC’99 [13] were synthesized using Nangate open cell library [14]. This library uses 45 nm, low threshold voltage, predictive models. After synthesis, the Spice netlist of the most critical path of each benchmark was extracted and ...

... To evaluate the efficiency of DFFC method, five benchmark circuits of ITC’99 [13] were synthesized using Nangate open cell library [14]. This library uses 45 nm, low threshold voltage, predictive models. After synthesis, the Spice netlist of the most critical path of each benchmark was extracted and ...

ADS7862 数据资料 dataSheet 下载

... converter that operates from a single +5V supply. The input channels are fully differential with a typical common-mode rejection of 80dB. The part contains dual 2µs successive approximation A/Ds, two differential sample-and-hold amplifiers, an internal +2.5V reference with REFIN and REFOUT pins and ...

... converter that operates from a single +5V supply. The input channels are fully differential with a typical common-mode rejection of 80dB. The part contains dual 2µs successive approximation A/Ds, two differential sample-and-hold amplifiers, an internal +2.5V reference with REFIN and REFOUT pins and ...

Wireless Components ASK/FSK 915MHz Single Conversion Receiver TDA 5212 Version 1.3

... 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that lifesupport device or system, or to affect its safety or effectiveness of that device or system. 2 Life support devices or systems are intended (a) to b ...

... 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that lifesupport device or system, or to affect its safety or effectiveness of that device or system. 2 Life support devices or systems are intended (a) to b ...

simplified block diagram

... latches are regenerating the analog residues into logical data before entering an error correction circuitry and a ...

... latches are regenerating the analog residues into logical data before entering an error correction circuitry and a ...

PI6C5946002

... It is suggested to add pull-up=4.7k and pull-down=1k for LVCMOS pins even though they have internal pull-up/down but with much higher value (>=50k) for higher design reliability. ...

... It is suggested to add pull-up=4.7k and pull-down=1k for LVCMOS pins even though they have internal pull-up/down but with much higher value (>=50k) for higher design reliability. ...

AD7490 数据手册DataSheet下载

... Reference Input for the AD7490. An external reference must be applied to this input. The voltage range for the external reference is 2.5 V ± 1% for specified performance. Power Supply Input. The VDD range for the AD7490 is from 2.7 V to 5.25 V. For the 0 V to 2 × REFIN range, VDD should be from 4.75 ...

... Reference Input for the AD7490. An external reference must be applied to this input. The voltage range for the external reference is 2.5 V ± 1% for specified performance. Power Supply Input. The VDD range for the AD7490 is from 2.7 V to 5.25 V. For the 0 V to 2 × REFIN range, VDD should be from 4.75 ...

a 200 MHz Clock Generator PLL ADF4001

... Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input. Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control ...

... Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input. Serial Data Input. The serial data is loaded MSB first with the two LSBs being the control ...

AN136 - Linear Technology

... and electrolytic capacitors should not block the air flow to the low profile, surface mount semiconductor components such as power MOSFETs, PWM controller, etc. To prevent the switching noise from upsetting other analog signals in the system, avoid routing sensitive signal traces underneath the supp ...

... and electrolytic capacitors should not block the air flow to the low profile, surface mount semiconductor components such as power MOSFETs, PWM controller, etc. To prevent the switching noise from upsetting other analog signals in the system, avoid routing sensitive signal traces underneath the supp ...