CMOS - Sites at Penn State

... For now, we can see that an AND gate requires both inputs to be ON for the output to be ON, while for an OR, the output is ON if either or both inputs are ON. Now to review the CMOS inverter device. As shown to the right, the CMOS device is made up of two stages in conjunction, a p channel MOSFET an ...

... For now, we can see that an AND gate requires both inputs to be ON for the output to be ON, while for an OR, the output is ON if either or both inputs are ON. Now to review the CMOS inverter device. As shown to the right, the CMOS device is made up of two stages in conjunction, a p channel MOSFET an ...

Chapter 4 – Ohm`s Law, Power and Energy

... Chapter 4 – Ohm’s Law, Power and Energy Introductory Circuit Analysis Robert L. Boylestad ...

... Chapter 4 – Ohm’s Law, Power and Energy Introductory Circuit Analysis Robert L. Boylestad ...

Power supply require..

... could decide to jump over the edge of it. To test for this, a capacitor was mounted on a circuit board similar to the one used in the LNA and a voltage was applied over it. At 210 V no sign of breakdown was evident. Our power supply limited us to apply higher voltages. The rated voltage of this capa ...

... could decide to jump over the edge of it. To test for this, a capacitor was mounted on a circuit board similar to the one used in the LNA and a voltage was applied over it. At 210 V no sign of breakdown was evident. Our power supply limited us to apply higher voltages. The rated voltage of this capa ...

The Field Effect Transistor

... (JFET), type 2N5458 and then continues with op amps using the TL082/084 dual/quad op amp chips. Details of these devices, including pin-out, can be found on the data sheets in the supplementary reading section on your web page. The links can be found on the Assignment Schedule. ...

... (JFET), type 2N5458 and then continues with op amps using the TL082/084 dual/quad op amp chips. Details of these devices, including pin-out, can be found on the data sheets in the supplementary reading section on your web page. The links can be found on the Assignment Schedule. ...

Slide 1

... CMOS devices have very high input resistance & even a small static charge flowing can develop a dangerously high voltage. This may damage insulation layer of the device & person handling it. Therefore CMOS IC pins should not be left un connected Even for storage Aluminium foil should be used so that ...

... CMOS devices have very high input resistance & even a small static charge flowing can develop a dangerously high voltage. This may damage insulation layer of the device & person handling it. Therefore CMOS IC pins should not be left un connected Even for storage Aluminium foil should be used so that ...

03_5_FPLD_methodology

... Total FPGA delay as a function of LUT size includes the routing delay Recent trends in commercial architectures have indeed moved toward larger LUT sizes to capture these gains: − Altera Stratix III, IV − Xilinx Virtex 5, 6 ...

... Total FPGA delay as a function of LUT size includes the routing delay Recent trends in commercial architectures have indeed moved toward larger LUT sizes to capture these gains: − Altera Stratix III, IV − Xilinx Virtex 5, 6 ...

A Brief Introduction to Single Electron Transistors

... technology already being tested in its laboratories. Whereas in research departments there can be several different methods which may enable building nanostructures in the 5 nm resolution and even lower [2], the current state of the art lies in the high fidelity fabrication technologies. The technol ...

... technology already being tested in its laboratories. Whereas in research departments there can be several different methods which may enable building nanostructures in the 5 nm resolution and even lower [2], the current state of the art lies in the high fidelity fabrication technologies. The technol ...

View File

... inputs of 5 V and 0.2 V to X and Y in any combination ,and find the output voltage for each combination . • Tabulate your results. How many input combinations are there? (4 Marks) •What happens when any input is high? (3 Marks) • What happens when both inputs are low? (3 Marks) ...

... inputs of 5 V and 0.2 V to X and Y in any combination ,and find the output voltage for each combination . • Tabulate your results. How many input combinations are there? (4 Marks) •What happens when any input is high? (3 Marks) • What happens when both inputs are low? (3 Marks) ...

Design of Low Voltage CMOS OTA Using Bulk

... Circuit diagram of the proposed bulk-driven OTA circuit is shown in Figure 2. The proposed OTA consists with two differential pairs. The input signal is given on the body of the PMOS in the first differential pair. It consists of four p-type transistors. The four transistors are represented as M1a, ...

... Circuit diagram of the proposed bulk-driven OTA circuit is shown in Figure 2. The proposed OTA consists with two differential pairs. The input signal is given on the body of the PMOS in the first differential pair. It consists of four p-type transistors. The four transistors are represented as M1a, ...

Lab06 - Weber State University

... L7: What is the measured value of AV and GV? How does it compare with your calculations and simulation? Note that the biggest source of variations from your simulation results will be due to the variation in β. Q1: What is the maximum gain that you can achieve without distorting the output signal? Q ...

... L7: What is the measured value of AV and GV? How does it compare with your calculations and simulation? Note that the biggest source of variations from your simulation results will be due to the variation in β. Q1: What is the maximum gain that you can achieve without distorting the output signal? Q ...

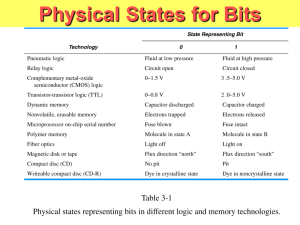

CMOS

Complementary metal–oxide–semiconductor (CMOS) /ˈsiːmɒs/ is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication. In 1963, while working for Fairchild Semiconductor, Frank Wanlass patented CMOS (US patent 3,356,858).CMOS is also sometimes referred to as complementary-symmetry metal–oxide–semiconductor (or COS-MOS).The words ""complementary-symmetry"" refer to the fact that the typical design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions.Two important characteristics of CMOS devices are high noise immunity and low static power consumption.Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor–transistor logic (TTL) or NMOS logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.The phrase ""metal–oxide–semiconductor"" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Aluminium was once used but now the material is polysilicon. Other metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond.