Dual Gate MOSFET Methodology to Design PASTA

... processors/circuits. Asynchronous circuits are those which do not assume any quantization of time. Therefore, they hold a great potential for logic design as they are free from several problems from clocked (synchronous) circuits. In general, logic flow in asynchronous circuits is controlled by a re ...

... processors/circuits. Asynchronous circuits are those which do not assume any quantization of time. Therefore, they hold a great potential for logic design as they are free from several problems from clocked (synchronous) circuits. In general, logic flow in asynchronous circuits is controlled by a re ...

DS2460 - Part Number Search

... must pull SDA LOW during the acknowledge clock pulse in such a way that SDA is stable LOW during the HIGH period of the acknowledge-related clock pulse plus the required setup and hold time (tHD:DAT after the falling edge of SCL and tSU:DAT before the rising edge of SCL). Not Acknowledged by Slave A ...

... must pull SDA LOW during the acknowledge clock pulse in such a way that SDA is stable LOW during the HIGH period of the acknowledge-related clock pulse plus the required setup and hold time (tHD:DAT after the falling edge of SCL and tSU:DAT before the rising edge of SCL). Not Acknowledged by Slave A ...

Electronics for Analog Signal Processing

... regular intervals whereas the amplitude could be any continuous value but taken only during these intervals of time, so this is the sample data. We can do a sort of processing for sample data that is called sample data processing; it also belongs to a certain extent to another analog signal processi ...

... regular intervals whereas the amplitude could be any continuous value but taken only during these intervals of time, so this is the sample data. We can do a sort of processing for sample data that is called sample data processing; it also belongs to a certain extent to another analog signal processi ...

Memristive model of amoeba`s learning

... this case, the LC contour is damped and excited oscillations decay fast. Fig. 3(a) demonstrates that when a non-periodic sequence of pulses is applied to the scheme, the circuit learning ability (or change of M ) is small and oscillations in the contour are strongly damped. In the opposite case, whe ...

... this case, the LC contour is damped and excited oscillations decay fast. Fig. 3(a) demonstrates that when a non-periodic sequence of pulses is applied to the scheme, the circuit learning ability (or change of M ) is small and oscillations in the contour are strongly damped. In the opposite case, whe ...

Ultrasound Physics Volume I

... slide, the basic angles between 0 and 90 degrees (inclusively) are shown, but the cosine values are also given in the table for angles greater than 90 degrees. From this table it should be evident that 45 degrees is basically the “same” angle as 135 degrees, 225 degrees, and 315 degrees (not shown), ...

... slide, the basic angles between 0 and 90 degrees (inclusively) are shown, but the cosine values are also given in the table for angles greater than 90 degrees. From this table it should be evident that 45 degrees is basically the “same” angle as 135 degrees, 225 degrees, and 315 degrees (not shown), ...

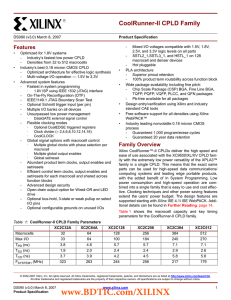

Features

... is extremely flexible, and very robust when compared to fixed or cascaded product term function blocks. ...

... is extremely flexible, and very robust when compared to fixed or cascaded product term function blocks. ...

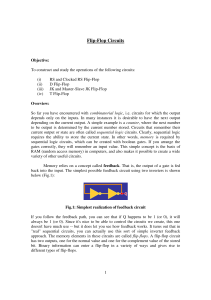

Flip-Flop Circuits

... It is sometimes desirable in sequential logic circuits to have a bistable RS flip-flop that only changes state when certain conditions are met regardless of the condition of either the Set or the Reset inputs. By connecting a 2-input AND gate in series with each input terminal of the RS NOR Flip-flo ...

... It is sometimes desirable in sequential logic circuits to have a bistable RS flip-flop that only changes state when certain conditions are met regardless of the condition of either the Set or the Reset inputs. By connecting a 2-input AND gate in series with each input terminal of the RS NOR Flip-flo ...

Tettex_TD_102_Simultaneous Dissipation Factor and Partial

... by PD arm (Ck and AKV) is removed. On the other hand there are several disadvantages and issues. The error of filter, which seems to be dominant (it will be shown in following chapters) remains. The over voltage protection provided by surge arrester is not directly grounded (in fact it is grounded v ...

... by PD arm (Ck and AKV) is removed. On the other hand there are several disadvantages and issues. The error of filter, which seems to be dominant (it will be shown in following chapters) remains. The over voltage protection provided by surge arrester is not directly grounded (in fact it is grounded v ...

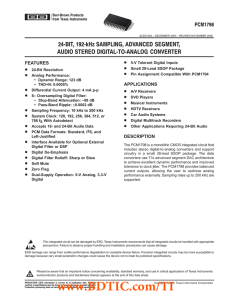

PCM1798 数据资料 dataSheet 下载

... The PCM1798 includes a power-on reset function. Figure 19 shows the operation of this function. With VDD > 2 V, the power-on reset function is enabled. The initialization sequence requires 1024 system clocks from the time VDD > 2 V. The PCM1798 also includes an external reset capability using the RS ...

... The PCM1798 includes a power-on reset function. Figure 19 shows the operation of this function. With VDD > 2 V, the power-on reset function is enabled. The initialization sequence requires 1024 system clocks from the time VDD > 2 V. The PCM1798 also includes an external reset capability using the RS ...

a 10-Bit, 125 MSPS High Performance TxDAC D/A Converter

... member of the TxDAC series of high performance, low power CMOS digital-to-analog-converters (DACs). The TxDAC family, which consists of pin compatible 8-, 10-, 12-, and 14-bit DACs, is specifically optimized for the transmit signal path of communication systems. All of the devices share the same int ...

... member of the TxDAC series of high performance, low power CMOS digital-to-analog-converters (DACs). The TxDAC family, which consists of pin compatible 8-, 10-, 12-, and 14-bit DACs, is specifically optimized for the transmit signal path of communication systems. All of the devices share the same int ...

5 V, 64 Kbit (8 Kb x 8) TIMEKEEPER® SRAM

... enable 1) is low, and E2 (chip enable 2) is high. The device architecture allows ripplethrough access of data from eight of 65,536 locations in the static storage array. Thus, the unique address specified by the 13 address inputs defines which one of the 8,192 bytes of data is to be accessed. Valid ...

... enable 1) is low, and E2 (chip enable 2) is high. The device architecture allows ripplethrough access of data from eight of 65,536 locations in the static storage array. Thus, the unique address specified by the 13 address inputs defines which one of the 8,192 bytes of data is to be accessed. Valid ...

Concepts Addressed in Lesson - Union

... Lesson 7.2 J-K Flip-Flops Concepts Addressed in Lesson 1. The J-K Flip-flop is known as the Universal Flip-flop having features of all the other flip-flops. 2. The J-K flip-flop can be used synchronously or asynchronously. 3. The J-K flip-flop is used for many applications which include, but are not ...

... Lesson 7.2 J-K Flip-Flops Concepts Addressed in Lesson 1. The J-K Flip-flop is known as the Universal Flip-flop having features of all the other flip-flops. 2. The J-K flip-flop can be used synchronously or asynchronously. 3. The J-K flip-flop is used for many applications which include, but are not ...

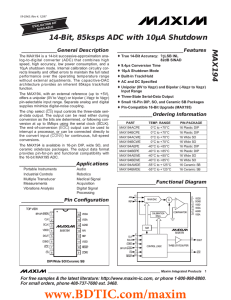

MAX194 14-Bit, 85ksps ADC with 10µA Shutdown _______________General Description ____________________________Features

... signal must be synchronized with CLK. The falling edge of CONV must occur during the period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start sig ...

... signal must be synchronized with CLK. The falling edge of CONV must occur during the period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the conversion-start sig ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.