THS1215 数据资料 dataSheet 下载

... The THS1215 is a CMOS, low-power, 12-bit, 15 MSPS analog-to-digital converter (ADC) that operates with a 3.3-V supply. The THS1215 gives circuit developers complete flexibility. The analog input to the THS1215 is differential with a gain of 1.0 in Mode 1 and 0.5 in Mode 2. The THS1215 provides a wid ...

... The THS1215 is a CMOS, low-power, 12-bit, 15 MSPS analog-to-digital converter (ADC) that operates with a 3.3-V supply. The THS1215 gives circuit developers complete flexibility. The analog input to the THS1215 is differential with a gain of 1.0 in Mode 1 and 0.5 in Mode 2. The THS1215 provides a wid ...

AN1571, Digital Blood Pressure Meter

... supply; this yields a system that is ratiometric. By nature of this ratiometric system, variations in the voltage of the power supplied to the system will have no effect on the system accuracy. The liquid crystal display (LCD) is directly driven from I/O ports A, B, and C on the microcontroller. Th ...

... supply; this yields a system that is ratiometric. By nature of this ratiometric system, variations in the voltage of the power supplied to the system will have no effect on the system accuracy. The liquid crystal display (LCD) is directly driven from I/O ports A, B, and C on the microcontroller. Th ...

12.2 switched-capacitor circuits

... As discussed in some detail in Chapter 6, resistors occupy inordinately large amounts of area in integrated circuits, particularly compared to MOS transistors. Switched-capacitor (SC) circuits are an elegant way to eliminate the resistors required in filters by replacing those elements with capacito ...

... As discussed in some detail in Chapter 6, resistors occupy inordinately large amounts of area in integrated circuits, particularly compared to MOS transistors. Switched-capacitor (SC) circuits are an elegant way to eliminate the resistors required in filters by replacing those elements with capacito ...

AD9755 数据手册DataSheet 下载

... Figure 3 shows a simplified block diagram of the AD9755. The AD9755 consists of a PMOS current source array capable of providing up to 20 mA of full-scale current, IOUTFS. The array is divided into 31 equal sources that make up the five most significant bits (MSBs). The next four bits, or middle bit ...

... Figure 3 shows a simplified block diagram of the AD9755. The AD9755 consists of a PMOS current source array capable of providing up to 20 mA of full-scale current, IOUTFS. The array is divided into 31 equal sources that make up the five most significant bits (MSBs). The next four bits, or middle bit ...

SFH 7050 - Photoplethysmography Sensor

... LED drivers used in solid state lighting or backlighting applications). Strong smoothing of the LED current during the pulse is advised. Using the approach of driving the LEDs to achieve equal DC - signal level at the receiving side (e.g. 2 V) for the red and IR signal LED drivers with a wider dynam ...

... LED drivers used in solid state lighting or backlighting applications). Strong smoothing of the LED current during the pulse is advised. Using the approach of driving the LEDs to achieve equal DC - signal level at the receiving side (e.g. 2 V) for the red and IR signal LED drivers with a wider dynam ...

Electrochemical Techniques 1

... – Measurements at around 1 Hz are quite easy – Measurements above 1kHz are rather more difficult – Measurements at around 50 Hz are difficult (due to mains frequency interference). ...

... – Measurements at around 1 Hz are quite easy – Measurements above 1kHz are rather more difficult – Measurements at around 50 Hz are difficult (due to mains frequency interference). ...

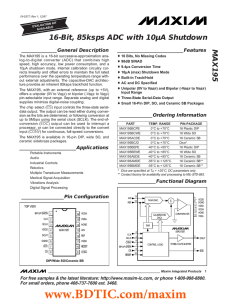

MAX195 16-Bit, 85ksps ADC with 10µA Shutdown _______________General Description ____________________________Features

... ignored. The convert signal must be synchronized with CLK. The falling edge of CONV must occur during the period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the ...

... ignored. The convert signal must be synchronized with CLK. The falling edge of CONV must occur during the period shown in Figures 3 and 4. When CLK is not directly controlled by your processor, two methods of ensuring synchronization are to drive CONV from EOC (continuous conversions) or to gate the ...

RF and Microwave Control Products in Silicon

... similar characteristics, but is designed using the silicon process. The GaAs product, due to the gate-lag effect, takes ~8 μs to settle to final RF power level. The silicon product settles to the same RF level in less than ~1 μs. The GaAs process has integration limitations due to the device charact ...

... similar characteristics, but is designed using the silicon process. The GaAs product, due to the gate-lag effect, takes ~8 μs to settle to final RF power level. The silicon product settles to the same RF level in less than ~1 μs. The GaAs process has integration limitations due to the device charact ...

MAX19538 12-Bit, 95Msps, 3.3V ADC General Description Features

... The MAX19538 is a 3.3V, 12-bit, 95Msps analog-to-digital converter (ADC) featuring a fully differential wideband track-and-hold (T/H) input amplifier, driving a low-noise internal quantizer. The analog input accepts single-ended or differential signals. The MAX19538 is optimized for low power, small ...

... The MAX19538 is a 3.3V, 12-bit, 95Msps analog-to-digital converter (ADC) featuring a fully differential wideband track-and-hold (T/H) input amplifier, driving a low-noise internal quantizer. The analog input accepts single-ended or differential signals. The MAX19538 is optimized for low power, small ...

Designing interface electronics for zirconium dioxide oxygen

... The time values (t1, t2, t4 and t5) are obtained during the signal processing routine. Therefore td only needs to recalculated after every new t value. It is recommended td is put into a rolling average filter to reduce noise and stabilise the td output. We recommend a buffer size of between 4 to 40 ...

... The time values (t1, t2, t4 and t5) are obtained during the signal processing routine. Therefore td only needs to recalculated after every new t value. It is recommended td is put into a rolling average filter to reduce noise and stabilise the td output. We recommend a buffer size of between 4 to 40 ...

Lecture 3

... that passes the D input to the Q output when the clock signal is high. This latch is said to be in transparent mode. When the clock is low, the input data sampled on the falling edge of the clock is held stable at the output for the entire phase, and the latch is in hold mode. The inputs must be ...

... that passes the D input to the Q output when the clock signal is high. This latch is said to be in transparent mode. When the clock is low, the input data sampled on the falling edge of the clock is held stable at the output for the entire phase, and the latch is in hold mode. The inputs must be ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.