M48T35AV

... user can be assured the memory will be in a write protected state, provided the VCC fall time is not less than tF. The M48T35AV may respond to transient noise spikes on VCC that reach into the deselect window during the time the device is sampling VCC. Therefore, decoupling of the power supply lines ...

... user can be assured the memory will be in a write protected state, provided the VCC fall time is not less than tF. The M48T35AV may respond to transient noise spikes on VCC that reach into the deselect window during the time the device is sampling VCC. Therefore, decoupling of the power supply lines ...

12-Bit Input-Buffered 80 MSPS ADC with JESD204A Output Interface

... Analog section power down, JESD interface still active. This is referred to as fast recovery powerdown ...

... Analog section power down, JESD interface still active. This is referred to as fast recovery powerdown ...

MAX11108 Tiny, 2.1mm x 1.6mm, 3Msps, Low-Power, Serial 12-Bit ADC EVALUATION KIT AVAILABLE

... high-speed, low-power, successive approximation analog-to-digital converter (ADC). This high-performance ADC includes a high-dynamic range sample-and-hold and a high-speed serial interface. This ADC accepts a full-scale input from 0V to the power supply or to the reference voltage. The MAX11108 feat ...

... high-speed, low-power, successive approximation analog-to-digital converter (ADC). This high-performance ADC includes a high-dynamic range sample-and-hold and a high-speed serial interface. This ADC accepts a full-scale input from 0V to the power supply or to the reference voltage. The MAX11108 feat ...

DS4M125/DS4M133/DS4M200 3.3V Margining Clock Oscillator with LVPECL/LVDS Output General Description

... The DS4M125/DS4M133/DS4M200 are margining clock oscillators with LVPECL or LVDS outputs. They are designed to fit in a 5mm x 3.2mm ceramic package with an AT-cut fundamental-mode crystal to form a complete clock oscillator. The circuit can generate the following frequencies and their ±5% frequency d ...

... The DS4M125/DS4M133/DS4M200 are margining clock oscillators with LVPECL or LVDS outputs. They are designed to fit in a 5mm x 3.2mm ceramic package with an AT-cut fundamental-mode crystal to form a complete clock oscillator. The circuit can generate the following frequencies and their ±5% frequency d ...

The Synthesizer

... range 46 to 78 MHz. Whilst this may appear to be a 32 MHz range and therefore capable of covering the whole of the HF spectrum, remember that there is a divide by 2 in the mixer – so for a 30 MHz range we would require a VCO swing of 60 MHz. This is avoided by using a programmable divider in the VCO ...

... range 46 to 78 MHz. Whilst this may appear to be a 32 MHz range and therefore capable of covering the whole of the HF spectrum, remember that there is a divide by 2 in the mixer – so for a 30 MHz range we would require a VCO swing of 60 MHz. This is avoided by using a programmable divider in the VCO ...

AD9754 数据手册DataSheet 下载

... The AD9754 is a current-output DAC with a nominal full-scale output current of 20 mA and > 100 kΩ output impedance. Differential current outputs are provided to support singleended or differential applications. Matching between the two current outputs ensures enhanced dynamic performance in a differ ...

... The AD9754 is a current-output DAC with a nominal full-scale output current of 20 mA and > 100 kΩ output impedance. Differential current outputs are provided to support singleended or differential applications. Matching between the two current outputs ensures enhanced dynamic performance in a differ ...

Capacitor unbalance protection for blocks in double

... double star connection This version of the capacitor unbalance protection can be applied if the capacitors are arranged in two parallel stars (ungrounded) with a current transformer between the neutrals. The stars do not have to be equal in size. An unbalance in the bank will cause current to flow i ...

... double star connection This version of the capacitor unbalance protection can be applied if the capacitors are arranged in two parallel stars (ungrounded) with a current transformer between the neutrals. The stars do not have to be equal in size. An unbalance in the bank will cause current to flow i ...

Jitter Analysis: A Brief Guide to Jitter

... We need to use a bit of detective work. Using real-time oscilloscopes we can measure sequences of adjacent periods. By measuring the differences from one period to the next period we can begin to see how the timing changes in any one instance of a period. A clock period that changes over one period ...

... We need to use a bit of detective work. Using real-time oscilloscopes we can measure sequences of adjacent periods. By measuring the differences from one period to the next period we can begin to see how the timing changes in any one instance of a period. A clock period that changes over one period ...

AD9726 数据手册DataSheet 下载

... The AD9726 is a 16-bit digital-to-analog converter (DAC) that offers leading edge performance at conversion rates up to 400 MSPS. The device uses low voltage differential signaling (LVDS) inputs and includes internal 100 Ω terminations. The analog output can be single-ended or differential current. ...

... The AD9726 is a 16-bit digital-to-analog converter (DAC) that offers leading edge performance at conversion rates up to 400 MSPS. The device uses low voltage differential signaling (LVDS) inputs and includes internal 100 Ω terminations. The analog output can be single-ended or differential current. ...

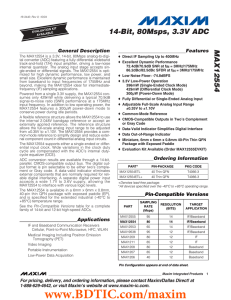

MAX12554 14-Bit, 80Msps, 3.3V ADC General Description Features

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.10V. The MAX12554 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX12554 supports either a single-ended or differential input clock. Wide var ...

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.10V. The MAX12554 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX12554 supports either a single-ended or differential input clock. Wide var ...

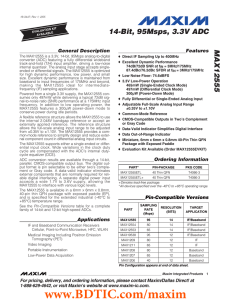

MAX12555 14-Bit, 95Msps, 3.3V ADC General Description Features

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.10V. The MAX12555 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX12555 supports either a single-ended or differential input clock. Wide var ...

... allows the full-scale analog input range to be adjusted from ±0.35V to ±1.10V. The MAX12555 provides a common-mode reference to simplify design and reduce external component count in differential analog input circuits. The MAX12555 supports either a single-ended or differential input clock. Wide var ...

PG2325382543

... we argued that scalable and energy-efficient WSN time synchronization should be achieved by closely matching the application requirements along axes such as scope, lifetime, and precision. We have also seen a number of techniques that provide service in different parts of this space. However, applic ...

... we argued that scalable and energy-efficient WSN time synchronization should be achieved by closely matching the application requirements along axes such as scope, lifetime, and precision. We have also seen a number of techniques that provide service in different parts of this space. However, applic ...

Aalborg Universitet A 3-10 GHz IR

... the generated UWB pulse signal at a PRR of 250 MHz. It can be seen that the PSD has a -10 dB bandwidth (BW) of 6.75 GHz (3.75-10.5 GHz) with a maximum magnitude of -40 dBm/MHz, which fulfills FCC’s UWB mask. An added benefit of the pulse generator is that as the PRR increases, the time slot T0 avail ...

... the generated UWB pulse signal at a PRR of 250 MHz. It can be seen that the PSD has a -10 dB bandwidth (BW) of 6.75 GHz (3.75-10.5 GHz) with a maximum magnitude of -40 dBm/MHz, which fulfills FCC’s UWB mask. An added benefit of the pulse generator is that as the PRR increases, the time slot T0 avail ...

AD9748 数据手册DataSheet 下载

... to full scale, associated with a 1 LSB change in digital input code. ...

... to full scale, associated with a 1 LSB change in digital input code. ...

Aalborg Universitet A Slow-Charge Fast-Discharge Technique

... the generated UWB pulse signal at a PRR of 250 MHz. It can be seen that the PSD has a -10 dB bandwidth (BW) of 6.75 GHz (3.75-10.5 GHz) with a maximum magnitude of -40 dBm/MHz, which fulfills FCC’s UWB mask. An added benefit of the pulse generator is that as the PRR increases, the time slot T0 avail ...

... the generated UWB pulse signal at a PRR of 250 MHz. It can be seen that the PSD has a -10 dB bandwidth (BW) of 6.75 GHz (3.75-10.5 GHz) with a maximum magnitude of -40 dBm/MHz, which fulfills FCC’s UWB mask. An added benefit of the pulse generator is that as the PRR increases, the time slot T0 avail ...

UM10301 User Manual for NXP Real Time Clocks PCF85x3, PCA8565

... supply voltage has reached a certain value upon power-up. The purpose is to ensure a defined behavior at start-up. This type of power-on reset is not present in these RTCs. The power-on reset circuit (POR) for these RTCs does not look at the supply voltage, but instead it is based on an internal res ...

... supply voltage has reached a certain value upon power-up. The purpose is to ensure a defined behavior at start-up. This type of power-on reset is not present in these RTCs. The power-on reset circuit (POR) for these RTCs does not look at the supply voltage, but instead it is based on an internal res ...

MAX127/MAX128 Multirange, +5V, 12-Bit DAS with 2-Wire Serial Interface General Description

... +5V supply for operation, yet accept signals at their analog inputs that may span above the power-supply rail and below ground. These systems provide eight analog input channels that are independently software programmable for a variety of ranges: ±10V, ±5V, 0 to +10V, 0 to +5V for the MAX127; and ± ...

... +5V supply for operation, yet accept signals at their analog inputs that may span above the power-supply rail and below ground. These systems provide eight analog input channels that are independently software programmable for a variety of ranges: ±10V, ±5V, 0 to +10V, 0 to +5V for the MAX127; and ± ...

ADS8324 数据资料 dataSheet 下载

... 500mV to VCC /2. There are several important implications of this. As the reference voltage is reduced, the analog voltage weight of each digital output code is reduced. This is often referred to as the Least Significant Bit (LSB) size and is equal to 2 • VREF divided by 16,384. This means that any ...

... 500mV to VCC /2. There are several important implications of this. As the reference voltage is reduced, the analog voltage weight of each digital output code is reduced. This is often referred to as the Least Significant Bit (LSB) size and is equal to 2 • VREF divided by 16,384. This means that any ...

Removal of Interferences from Partial Discharge Pulses

... performance for mean square error against an ideal procedure. The “minimax” principle is used in statistics in order to design estimators. Since the denoised signal can be assimilated to the estimator of an unknown regression function, the “minimax” estimator is the one that realizes the minimum of ...

... performance for mean square error against an ideal procedure. The “minimax” principle is used in statistics in order to design estimators. Since the denoised signal can be assimilated to the estimator of an unknown regression function, the “minimax” estimator is the one that realizes the minimum of ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.