Quad, 8-Bit, 100 MSPS Serial LVDS 1.8 V A/D Converter AD9287

... responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog ...

... responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog ...

NB3N3020DTGEVB Evaluation Board User's Manual EVAL BOARD USER’S MANUAL

... Clock amplitude signal from 2 MHz to 210 MHz which satisfies datasheet VIH and VIL to drive X1/CLK. Input tr/tf transition edges should be about 250 ps. Use a TTC (Time Transition Convertor) such as Agilent 14534 (250 ps) or equivalent, if needed to supply proper edges. Termination of a signal gener ...

... Clock amplitude signal from 2 MHz to 210 MHz which satisfies datasheet VIH and VIL to drive X1/CLK. Input tr/tf transition edges should be about 250 ps. Use a TTC (Time Transition Convertor) such as Agilent 14534 (250 ps) or equivalent, if needed to supply proper edges. Termination of a signal gener ...

C5-2 A 10Gb/s 10mm On-Chip Serial Link in 65nm CMOS Featuring

... On-chip serial links are attractive for high-speed point-to-point applications as they can achieve 10Gb/s or higher data rates without using power-hungry and floorplan-disrupting repeaters. Several circuit techniques have been proposed to improve the communication speed and energy-efficiency of on-c ...

... On-chip serial links are attractive for high-speed point-to-point applications as they can achieve 10Gb/s or higher data rates without using power-hungry and floorplan-disrupting repeaters. Several circuit techniques have been proposed to improve the communication speed and energy-efficiency of on-c ...

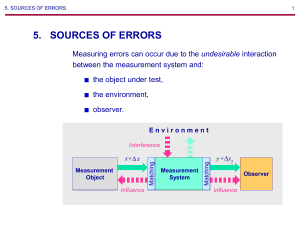

Measurement Theory Principles

... high-frequency measurement signals along transmission lines. If a transmission line is not terminated characteristically, reflections off the ends of the line will cause standing waves on the line; the line output signal is no longer a good measure for the line input ...

... high-frequency measurement signals along transmission lines. If a transmission line is not terminated characteristically, reflections off the ends of the line will cause standing waves on the line; the line output signal is no longer a good measure for the line input ...

FPGA Power Reduction Using Configurable Dual-Vdd

... Permanent Soft Error Rate Single-event upset (SEU) due to cosmic rays or high energy particles may affect configuration SRAMs in FPGAs and result in permanent soft error ...

... Permanent Soft Error Rate Single-event upset (SEU) due to cosmic rays or high energy particles may affect configuration SRAMs in FPGAs and result in permanent soft error ...

In situ testing of detector controllers

... • Counts per bin are proportional to voltage delta represented by each code. – Works just as well in the presence of noise ! – Need enough data for statistical errors to be negligible compared to fixed pattern. ...

... • Counts per bin are proportional to voltage delta represented by each code. – Works just as well in the presence of noise ! – Need enough data for statistical errors to be negligible compared to fixed pattern. ...

P5Z22V10 5V zero power, TotalCMOS™, universal PLD device

... User-defined functions are created by programming the connections of input signals into the array. User-configurable output structures in the form of I/O macrocells further increase logic flexibility. ...

... User-defined functions are created by programming the connections of input signals into the array. User-configurable output structures in the form of I/O macrocells further increase logic flexibility. ...

Sequential Logic Circuits - VLSI

... SR Latch Circuit Transient Analysis • For transient analysis, we have to consider an event which results in a state change, reset set, or set reset • In either case, we note that both of the output nodes undergo simultaneous voltage transitions. One is from logic-low to logichigh, and the other ...

... SR Latch Circuit Transient Analysis • For transient analysis, we have to consider an event which results in a state change, reset set, or set reset • In either case, we note that both of the output nodes undergo simultaneous voltage transitions. One is from logic-low to logichigh, and the other ...

FEATURES 2.5V ULTRA-PRECISION 1:4 LVDS Precision Edge FANOUT BUFFER/TRANSLATOR

... 10. Set-up and hold times apply to synchronous applications that intend to enable/disable before the next clock cycle. For asynchronous applications, set-up and hold times do not apply. 11. Random jitter is measured with a K28.7 pattern, measured at ≤fMAX. 12. Deterministic jitter is measured at 2.5 ...

... 10. Set-up and hold times apply to synchronous applications that intend to enable/disable before the next clock cycle. For asynchronous applications, set-up and hold times do not apply. 11. Random jitter is measured with a K28.7 pattern, measured at ≤fMAX. 12. Deterministic jitter is measured at 2.5 ...

Analog Oscilloscope Operation Manual

... 1. To maintain the precision and reliability of the product use it in the standard conditions(temperature 10℃~35℃ and humidity 45%~85%) 2. After turning on power, please allow a 15minute preheating warmup period before using. 3. Triple-line power cord is to be used for this product. But when you are ...

... 1. To maintain the precision and reliability of the product use it in the standard conditions(temperature 10℃~35℃ and humidity 45%~85%) 2. After turning on power, please allow a 15minute preheating warmup period before using. 3. Triple-line power cord is to be used for this product. But when you are ...

PPC2011-KlysModESS

... those of the bouncer inductor) will become bulky and costly as the pulse length and average power increases, with still poor performance (open loop compensation system). Note that in an optimal design [5], the oscillation period of the bouncer shall be around 6 times higher than the pulse length (= ...

... those of the bouncer inductor) will become bulky and costly as the pulse length and average power increases, with still poor performance (open loop compensation system). Note that in an optimal design [5], the oscillation period of the bouncer shall be around 6 times higher than the pulse length (= ...

NE555 SA555

... (pin 2) during the timing cycle discharges the external capacitor and causes the cycle to start over. The timing cycle now starts on the positive edge of the reset pulse. During the time the reset pulse in applied, the output is driven to its LOW state. When a negativetrigger pulse is applied to pin ...

... (pin 2) during the timing cycle discharges the external capacitor and causes the cycle to start over. The timing cycle now starts on the positive edge of the reset pulse. During the time the reset pulse in applied, the output is driven to its LOW state. When a negativetrigger pulse is applied to pin ...

TSA7887 - Silicon Labs

... Power Supply Voltage: The TSA7887’s VDD range +2.7V to +5.25V. In two-channel operation, the VDD pin also serves as the TSA7887’s voltage reference source during conversions. For optimal performance, the VDD pin should be bypassed to GND with a 10-µF tantalum capacitor in parallel with a 0.1µF ceram ...

... Power Supply Voltage: The TSA7887’s VDD range +2.7V to +5.25V. In two-channel operation, the VDD pin also serves as the TSA7887’s voltage reference source during conversions. For optimal performance, the VDD pin should be bypassed to GND with a 10-µF tantalum capacitor in parallel with a 0.1µF ceram ...

MAX1182 Dual 10-Bit, 65Msps, 3V, Low-Power ADC General Description

... The MAX1182 features parallel, CMOS-compatible three-state outputs. The digital output format is set to two’s complement or straight offset binary through a single control pin. The device provides for a separate output power supply of 1.7V to 3.6V for flexible interfacing. The MAX1182 is available i ...

... The MAX1182 features parallel, CMOS-compatible three-state outputs. The digital output format is set to two’s complement or straight offset binary through a single control pin. The device provides for a separate output power supply of 1.7V to 3.6V for flexible interfacing. The MAX1182 is available i ...

EMI EMC pt 4

... 0-V surface-mount resistor could be placed in series with the clock lands. • Later in the design, if problems are uncovered necessitating increasing the clock rise/falltimes, then the capacitor can be added and the value of the series resistor can be changed. • Why is this significant? The answer is ...

... 0-V surface-mount resistor could be placed in series with the clock lands. • Later in the design, if problems are uncovered necessitating increasing the clock rise/falltimes, then the capacitor can be added and the value of the series resistor can be changed. • Why is this significant? The answer is ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.