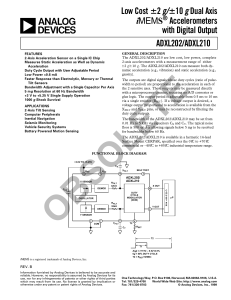

ADXL202/ADXL210 Low Cost 62 g/610 g Dual Axis iMEMS

... The ADXL202/ADXL210 were specifically designed to work with low cost microcontrollers. Specific code sets, reference designs, and application notes are available from the factory. This section will outline a general design procedure and discuss the various trade-offs that need to be considered. The ...

... The ADXL202/ADXL210 were specifically designed to work with low cost microcontrollers. Specific code sets, reference designs, and application notes are available from the factory. This section will outline a general design procedure and discuss the various trade-offs that need to be considered. The ...

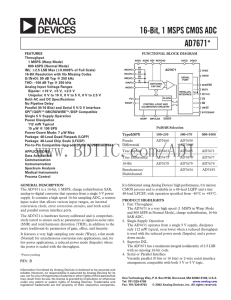

AD7671 数据手册DataSheet下载

... The AD7671 is a 16-bit, 1 MSPS, charge redistribution SAR, analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and bo ...

... The AD7671 is a 16-bit, 1 MSPS, charge redistribution SAR, analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and bo ...

Phase Jitter Application Note

... Figure 12: Standard Phase Noise Test Set Up. For this test set up, the reference clock is an ovenized crystal oscillator (OCXO), which is approximately an ideal sinewave when compared to a VCXO, while the other is the VCXO (DUT). The frequency of the two devices must be close enough to allow an exac ...

... Figure 12: Standard Phase Noise Test Set Up. For this test set up, the reference clock is an ovenized crystal oscillator (OCXO), which is approximately an ideal sinewave when compared to a VCXO, while the other is the VCXO (DUT). The frequency of the two devices must be close enough to allow an exac ...

AD7171 数据手册DataSheet下载

... The AD7171 has one differential analog input channel that is connected to the modulator; that is, the input is unbuffered. Note that this unbuffered input path provides a dynamic load to the driving source. Therefore, resistor/capacitor combinations on the input pins can cause dc gain errors, depend ...

... The AD7171 has one differential analog input channel that is connected to the modulator; that is, the input is unbuffered. Note that this unbuffered input path provides a dynamic load to the driving source. Therefore, resistor/capacitor combinations on the input pins can cause dc gain errors, depend ...

to get the file - Caltech Optical Observatories

... • Counts per bin are proportional to voltage delta represented by each code. – Works just as well in the presence of noise ! – Need enough data for statistical errors to be negligible compared to fixed pattern. ...

... • Counts per bin are proportional to voltage delta represented by each code. – Works just as well in the presence of noise ! – Need enough data for statistical errors to be negligible compared to fixed pattern. ...

AD7665 数据手册DataSheet下载

... The AD7665 is a 16-bit, 570 kSPS, charge redistribution SAR, analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and ...

... The AD7665 is a 16-bit, 570 kSPS, charge redistribution SAR, analog-to-digital converter that operates from a single 5 V power supply. It contains a high speed 16-bit sampling ADC, a resistor input scaler that allows various input ranges, an internal conversion clock, error correction circuits, and ...

Analog+digital phase and frequency detector for phase locking of

... The capture range of the APD, however, is on the order of the loop bandwidth f l which is typically 3 – 5 MHz, limited by the loop delay time and the phase lag in the diode laser frequency modulation response. If the beat note differs from the locking point by more than f l the APD error signal is a ...

... The capture range of the APD, however, is on the order of the loop bandwidth f l which is typically 3 – 5 MHz, limited by the loop delay time and the phase lag in the diode laser frequency modulation response. If the beat note differs from the locking point by more than f l the APD error signal is a ...

SN65MLVD040 数据资料 dataSheet 下载

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

A Two-Step A/D Conversion and Column Self

... other applications that require the image sensor to have frame rates faster than 30 fps. Many papers have reported attempts to improve the disadvantages of SS ADC [2–15]. Among them, cyclic ADC or Successive Approximation Register (SAR) ADC are well-known techniques for the high frame rate CIS. Howe ...

... other applications that require the image sensor to have frame rates faster than 30 fps. Many papers have reported attempts to improve the disadvantages of SS ADC [2–15]. Among them, cyclic ADC or Successive Approximation Register (SAR) ADC are well-known techniques for the high frame rate CIS. Howe ...

DS28CM00 - Maxim Part Number Search

... bus capacitance CB is 400pF. The maximum rise time must not exceed 300ns. Assuming maximum rise time, the maximum resistor value at any given capacitance CB is calculated as: RPMAX = 300ns/(CB*ln(7/3)). For a bus capacitance of 400pF the maximum pullup resistor would be 885Ω. Since a 885Ω pullup res ...

... bus capacitance CB is 400pF. The maximum rise time must not exceed 300ns. Assuming maximum rise time, the maximum resistor value at any given capacitance CB is calculated as: RPMAX = 300ns/(CB*ln(7/3)). For a bus capacitance of 400pF the maximum pullup resistor would be 885Ω. Since a 885Ω pullup res ...

SWITCHED CAPACITOR CIRCUITS

... Typically, no problems occur unless capacitance voltages are held for a long time. For example, vout(t) = vCH[1 - e-t/(RBulkCH)] If RBulk ≈ 109Ω and CH = 10pF, the time constant is 109·10-11 = 0.01seconds ...

... Typically, no problems occur unless capacitance voltages are held for a long time. For example, vout(t) = vCH[1 - e-t/(RBulkCH)] If RBulk ≈ 109Ω and CH = 10pF, the time constant is 109·10-11 = 0.01seconds ...

paper

... additional information allows one to find periodic structure in the noise, and better characterize its behavior. In order to achieve the sub-mV level resolution necessary to collect supply noise statistics with relatively simple circuitry, we used a voltage-controlled oscillator (VCO) to perform AID ...

... additional information allows one to find periodic structure in the noise, and better characterize its behavior. In order to achieve the sub-mV level resolution necessary to collect supply noise statistics with relatively simple circuitry, we used a voltage-controlled oscillator (VCO) to perform AID ...

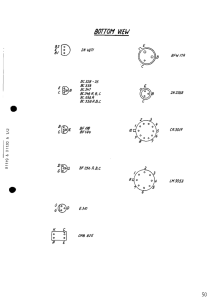

D1V2 Assembly Manual

... 17. Power up again and adjust Pot R1 until Point A to 10Vdc, Adjust Pot R2 until Point B is 0Vdc, Repeat adjustment on R1 and R2 when necessary. 18. Then adjust Pot R8 until voltage across R14 is 5Vdc. 19. Repeat to solder other Jfet IV section and adjust voltages as above. 20. Solder the LM317 and ...

... 17. Power up again and adjust Pot R1 until Point A to 10Vdc, Adjust Pot R2 until Point B is 0Vdc, Repeat adjustment on R1 and R2 when necessary. 18. Then adjust Pot R8 until voltage across R14 is 5Vdc. 19. Repeat to solder other Jfet IV section and adjust voltages as above. 20. Solder the LM317 and ...

The American University in Cairo School of Science and Engineering

... the maximum speed of the transistors. Designers kept increasing the operational frequency until that increase was stopped by the power barrier as shown in figure 1.1 (d) starting a new era, the Many-core era. In the Many-Core era, designers utilized the huge number of transistors that can be put on ...

... the maximum speed of the transistors. Designers kept increasing the operational frequency until that increase was stopped by the power barrier as shown in figure 1.1 (d) starting a new era, the Many-core era. In the Many-Core era, designers utilized the huge number of transistors that can be put on ...

DAC5662A 数据资料 dataSheet 下载

... Operating with update rates of up to 275 MSPS, the DAC5662A offers exceptional dynamic performance and tight-gain and offset matching, characteristics that make it suitable in either I/Q baseband or direct IF communication applications. Each DAC has a high-impedance differential current output, suit ...

... Operating with update rates of up to 275 MSPS, the DAC5662A offers exceptional dynamic performance and tight-gain and offset matching, characteristics that make it suitable in either I/Q baseband or direct IF communication applications. Each DAC has a high-impedance differential current output, suit ...

Measurement of Capacitance - STLCC.edu

... where C is the capacity in farads (multiply by 1 million or 106 for microfarads), A is the area of either plate in square meters, d is the plate separation in meters, εo is the permittivity of free space and κ is the dielectric constant of the material between the plates. Note that C varies directly ...

... where C is the capacity in farads (multiply by 1 million or 106 for microfarads), A is the area of either plate in square meters, d is the plate separation in meters, εo is the permittivity of free space and κ is the dielectric constant of the material between the plates. Note that C varies directly ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.