RTH050.pdf

... The clock source jitter and the aperture jitter combine in an rms manner to yield the total sampling jitter. See Definition of Terms. Device aperture jitter increases as the V(CLK1P) – V(CLK1N) slew rate at the zero crossing decreases. See Theory of Operation. The differential pedestal error is prop ...

... The clock source jitter and the aperture jitter combine in an rms manner to yield the total sampling jitter. See Definition of Terms. Device aperture jitter increases as the V(CLK1P) – V(CLK1N) slew rate at the zero crossing decreases. See Theory of Operation. The differential pedestal error is prop ...

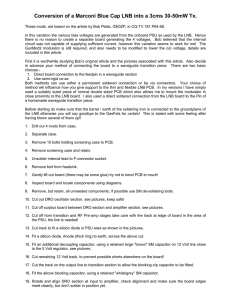

Conversion of a Marconi Blue Cap LNB into a 3cms 30

... 20. Cut diecast screening sections out, see diagrams. This is different from Bob’s original design as I use some additional screws to allow tuning of the lines. 21. Drill 3 2.5mm holes for 6BA adjusting screws, slightly enlarge, then self tap the bolts into the soft diecast material, use single loc ...

... 20. Cut diecast screening sections out, see diagrams. This is different from Bob’s original design as I use some additional screws to allow tuning of the lines. 21. Drill 3 2.5mm holes for 6BA adjusting screws, slightly enlarge, then self tap the bolts into the soft diecast material, use single loc ...

ICS850S1601I Advance Data Sheet.fm

... © 2008 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product nam ...

... © 2008 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product nam ...

Errata - Silicon Labs

... bypassing the APORT. Direct output connections can be enabled by programming MAINOUTEN=1 and/or ALTOUTEN=1 (while keeping APORTOUTEN=0) in the VDACn_OPAx_OUT register. The device data sheet lists the available main output and alternative output connections to pins per VDAC output or OPAMP. Resolutio ...

... bypassing the APORT. Direct output connections can be enabled by programming MAINOUTEN=1 and/or ALTOUTEN=1 (while keeping APORTOUTEN=0) in the VDACn_OPAx_OUT register. The device data sheet lists the available main output and alternative output connections to pins per VDAC output or OPAMP. Resolutio ...

101 p2 _A1_ IC Characterization

... The oscillation circuit is made up of an inverter or amplifier (inside the microcontroller) and an external ceramic resonator with load capacitors, CL1 and CL2, (see Figure 1). The oscillation frequency is calculated using the resonant frequency (Fr), static capacitance (C0), and motional capacitanc ...

... The oscillation circuit is made up of an inverter or amplifier (inside the microcontroller) and an external ceramic resonator with load capacitors, CL1 and CL2, (see Figure 1). The oscillation frequency is calculated using the resonant frequency (Fr), static capacitance (C0), and motional capacitanc ...

RMS, power, dB, PDF. Analogue-to

... • In air acoustics in which the sound pressure level is measured, the reference for the dB scale is the average lowest threshold of audibility, by convention taken as 20 Pa (2 x 10-5 Pa ) • This 20 Pa is the RMS of the reference signal • In other applications, however, the dB scale is used to comp ...

... • In air acoustics in which the sound pressure level is measured, the reference for the dB scale is the average lowest threshold of audibility, by convention taken as 20 Pa (2 x 10-5 Pa ) • This 20 Pa is the RMS of the reference signal • In other applications, however, the dB scale is used to comp ...

1.ddr sdram

... before incurring permanent damage, although they are not required to function correctly at that level. The main benefit of DDR3 comes from the higher bandwidth made possible by DDR3's 8-burst-deep prefetch buffer, in contrast to DDR2's 4-burst-deep or DDR's 2-burst-deep prefetch buffer. DDR3 modules ...

... before incurring permanent damage, although they are not required to function correctly at that level. The main benefit of DDR3 comes from the higher bandwidth made possible by DDR3's 8-burst-deep prefetch buffer, in contrast to DDR2's 4-burst-deep or DDR's 2-burst-deep prefetch buffer. DDR3 modules ...

PDF Data Sheet Rev. 0

... ability to reduce power consumption of individual functional blocks or power down unused blocks in half-duplex applications. A serial port interface (SPI) allows software programming of the various functional blocks. An on-chip PLL clock multiplier and synthesizer provide all the required internal c ...

... ability to reduce power consumption of individual functional blocks or power down unused blocks in half-duplex applications. A serial port interface (SPI) allows software programming of the various functional blocks. An on-chip PLL clock multiplier and synthesizer provide all the required internal c ...

AD7621 数据手册DataSheet下载

... 48-lead LQFP and 48-lead LFCSP_VQ packages Speed upgrade of the AD7677 ...

... 48-lead LQFP and 48-lead LFCSP_VQ packages Speed upgrade of the AD7677 ...

ADuM2200 数据手册DataSheet下载

... the supply voltage of either side ranging from 3.0 V to 5.5 V, providing compatibility with lower voltage systems as well as enabling voltage translation functionality across the isolation barrier. The ADuM220x isolators have a patented refresh feature that ensures dc correctness in the absence of i ...

... the supply voltage of either side ranging from 3.0 V to 5.5 V, providing compatibility with lower voltage systems as well as enabling voltage translation functionality across the isolation barrier. The ADuM220x isolators have a patented refresh feature that ensures dc correctness in the absence of i ...

1. Introduction - About the journal

... presented as an alternative to the current-mode circuit. CDTA seems to be a versatile component in the realization of analog signal processing circuits; especially analogue frequency filters [7-8]. However the parasitic resistances at the input ports cannot be electronically adjusted. So in some cir ...

... presented as an alternative to the current-mode circuit. CDTA seems to be a versatile component in the realization of analog signal processing circuits; especially analogue frequency filters [7-8]. However the parasitic resistances at the input ports cannot be electronically adjusted. So in some cir ...

Transistors and Logic Gates

... Propagation delay: The average transition delay time for a signal to propagate from input to output when the binary signals change in value ( in ns) Noise margin: is the maximum noise voltage added to the input signal of a digital circuit that doesn’t cause an undesirable change in the circuit out ...

... Propagation delay: The average transition delay time for a signal to propagate from input to output when the binary signals change in value ( in ns) Noise margin: is the maximum noise voltage added to the input signal of a digital circuit that doesn’t cause an undesirable change in the circuit out ...

ADS8481 - Texas Instruments

... Propagation delay time, BUSY falling edge to next RD (or CS for read cycle) falling ...

... Propagation delay time, BUSY falling edge to next RD (or CS for read cycle) falling ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.