Analog signal chain design considerations

... resistance is needed. Note that for those applications where very high accuracy is not needed, there is no need of gain error compensation and hence no external reference resistance is required. ...

... resistance is needed. Note that for those applications where very high accuracy is not needed, there is no need of gain error compensation and hence no external reference resistance is required. ...

General Description

... The Defense-Grade Virtex®-6Q family provides the most advanced features in the Aerospace & Defense FPGA market and represents the 3rd generation of secure silicon architecture products from Xilinx. Virtex-6Q FPGAs are the programmable silicon foundation for Targeted Design Platforms that deliver int ...

... The Defense-Grade Virtex®-6Q family provides the most advanced features in the Aerospace & Defense FPGA market and represents the 3rd generation of secure silicon architecture products from Xilinx. Virtex-6Q FPGAs are the programmable silicon foundation for Targeted Design Platforms that deliver int ...

PPT

... • What’s the current through each resistor at t=0? • What’s the current through each resistor after a long time? • How long is a long time? At t=0 replace capacitor with solid wire (open circuit) then use loop rule or Req series/parallel. Att>>0replacecapacitor withbreakinwire,i3=0,and use ...

... • What’s the current through each resistor at t=0? • What’s the current through each resistor after a long time? • How long is a long time? At t=0 replace capacitor with solid wire (open circuit) then use loop rule or Req series/parallel. Att>>0replacecapacitor withbreakinwire,i3=0,and use ...

ICS673-01 PLL Building Block Features Description

... The ICS673 is a PLL building block circuit that includes an integrated VCO with a wide operating range. While it can easily lock MHz frequencies to other MHz frequencies, it is especially designed for starting with a kHz frequency and generating a frequency-locked MHz clock. Refer to Figure 1 below ...

... The ICS673 is a PLL building block circuit that includes an integrated VCO with a wide operating range. While it can easily lock MHz frequencies to other MHz frequencies, it is especially designed for starting with a kHz frequency and generating a frequency-locked MHz clock. Refer to Figure 1 below ...

Encoder Products Company offers several index pulse gating

... These are comprised of a disc with the index pulse etched onto this disk in addition to the main count channels. This type of index is usually referenced to a particular count channel such as "A". It is normally not gated, however it can be done on occasions. By making this etched aperture a certain ...

... These are comprised of a disc with the index pulse etched onto this disk in addition to the main count channels. This type of index is usually referenced to a particular count channel such as "A". It is normally not gated, however it can be done on occasions. By making this etched aperture a certain ...

MAX1134/MAX1135 16-Bit ADCs, 150ksps, 3.3V Single Supply General Description Features

... (AVDD = DVDD = 3.3V ±5%, TA = TMIN to TMAX, unless otherwise noted.) Note 1: Tested at AVDD = DVDD = 3.3V, bipolar input mode. Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the gain error and offset error have been nullified. Note 3: Offs ...

... (AVDD = DVDD = 3.3V ±5%, TA = TMIN to TMAX, unless otherwise noted.) Note 1: Tested at AVDD = DVDD = 3.3V, bipolar input mode. Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the gain error and offset error have been nullified. Note 3: Offs ...

D.J. Perreault and J.G. Kassakian, Distributed Interleaving of Paralleled Power Converters, IEEE Transactions on Circuits and Systems I , Vol. 44, No. 8, Aug. 1997, pp. 728-734.

... The conventional approach is effective and simple for systems with a fixed number of cells. However, it becomes less practical if there is a varying number of cells in the system, especially if interleaving is to be maintained after failure of one or more cells, as is sometimes desired [2]. The diff ...

... The conventional approach is effective and simple for systems with a fixed number of cells. However, it becomes less practical if there is a varying number of cells in the system, especially if interleaving is to be maintained after failure of one or more cells, as is sometimes desired [2]. The diff ...

LTC3880 System Checklist

... o Must have a single base address for in system programming It is recommended that you use 0xXF (i.e. 0x4F) as the single, common base address ...

... o Must have a single base address for in system programming It is recommended that you use 0xXF (i.e. 0x4F) as the single, common base address ...

DS1080CL Spread-Spectrum Crystal Multiplier General Description Features

... low-power standby mode where the SSO output is high impedance. If the PDN pin is open, the SSO output is active but the spread-spectrum dithering is disabled. The spread-spectrum dither rate is fixed at fIN/512 to keep the dither rate above the audio frequency range. On power-up, the output clock (S ...

... low-power standby mode where the SSO output is high impedance. If the PDN pin is open, the SSO output is active but the spread-spectrum dithering is disabled. The spread-spectrum dither rate is fixed at fIN/512 to keep the dither rate above the audio frequency range. On power-up, the output clock (S ...

16-Bit, 1 MS/s High-Speed Data Acquisition Boards

... Digital I/O Transfer Rate (System Paced, Asynchronous): 33 to 4,000 port reads/ writes or single bit reads/writes per second typ; system dependent. Input High Voltage: 2.0 V min, 5.0 V absolute max Input Low Voltage: 0.8 V max, 0 V recommended min Output High Voltage: 4.4 V min (IOH = –50 µA), 3.76 ...

... Digital I/O Transfer Rate (System Paced, Asynchronous): 33 to 4,000 port reads/ writes or single bit reads/writes per second typ; system dependent. Input High Voltage: 2.0 V min, 5.0 V absolute max Input Low Voltage: 0.8 V max, 0 V recommended min Output High Voltage: 4.4 V min (IOH = –50 µA), 3.76 ...

OP4004B - Wireless | Murata Manufacturing

... High Power Supply Noise Immunity - the OP4004B uses both differential active devices and differential SAW technology to minimize the effects of power supply noise on jitter and phase noise, as shown in Figures 2 and 3. Optical data communications circuits must switch relatively high levels of curren ...

... High Power Supply Noise Immunity - the OP4004B uses both differential active devices and differential SAW technology to minimize the effects of power supply noise on jitter and phase noise, as shown in Figures 2 and 3. Optical data communications circuits must switch relatively high levels of curren ...

D. Other Pulse Shaping Methods

... pickup and may need to be kept at a distance from detectors and preamplifiers where signal levels are low A technique known as common mode rejection is sometimes helpful in reducing the effects of noise pickup on interconnecting cables. ...

... pickup and may need to be kept at a distance from detectors and preamplifiers where signal levels are low A technique known as common mode rejection is sometimes helpful in reducing the effects of noise pickup on interconnecting cables. ...

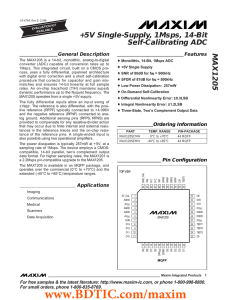

MAX1205 +5V Single-Supply, 1Msps, 14-Bit Self-Calibrating ADC General Description

... in the switched capacitor MDAC. Note that the pipeline introduces latency of four sampling periods between the input being sampled and the output appearing at D13–D0. While the device can handle both single-ended and differential inputs (see Requirements for Reference and Analog Signal Inputs), the ...

... in the switched capacitor MDAC. Note that the pipeline introduces latency of four sampling periods between the input being sampled and the output appearing at D13–D0. While the device can handle both single-ended and differential inputs (see Requirements for Reference and Analog Signal Inputs), the ...

Design of JK Flip-Flop using MODFET Technology

... Although JK flip-flop is an improvement on the clocked SR flip-flop it still suffers from timing problems called "race" if the output Q changes state before the timing pulse of the clock input has time to go "OFF", so the timing pulse period (T) must be kept as short as possible (high frequency). Th ...

... Although JK flip-flop is an improvement on the clocked SR flip-flop it still suffers from timing problems called "race" if the output Q changes state before the timing pulse of the clock input has time to go "OFF", so the timing pulse period (T) must be kept as short as possible (high frequency). Th ...

ics843011.pdf

... The aforementioned trademarks, HiPerClockS™ and FemtoClocks™ are a trademark of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Inc ...

... The aforementioned trademarks, HiPerClockS™ and FemtoClocks™ are a trademark of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Inc ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.