simplified block diagram

... The TS8388BFS features a full power input bandwidth of 1.5 GHz. Control pin GORB is provided to select either Gray or Binary data output format. Gain control pin is provided in order to adjust the ADC gain. A Data Ready output asynchronous reset (DRRB) is available on TS8388BFS. The TS8388BFS uses o ...

... The TS8388BFS features a full power input bandwidth of 1.5 GHz. Control pin GORB is provided to select either Gray or Binary data output format. Gain control pin is provided in order to adjust the ADC gain. A Data Ready output asynchronous reset (DRRB) is available on TS8388BFS. The TS8388BFS uses o ...

EDM-M - Duplomatic Oleodinamica

... ok OUTPUT”, located on pin 9 (referred to zero power supply, pin 15) with load resistance of 220 KΩ and max current 100 mA . When the card works normally, on this pin there is the same voltage as the power supply; when there is an anomaly, the output voltage is zero. The anomalies could be: - low vo ...

... ok OUTPUT”, located on pin 9 (referred to zero power supply, pin 15) with load resistance of 220 KΩ and max current 100 mA . When the card works normally, on this pin there is the same voltage as the power supply; when there is an anomaly, the output voltage is zero. The anomalies could be: - low vo ...

Slide 1

... Lower Limits 1. Must be at least 10 times higher than the control system frequency 2. Higher than 20kHz – audible frequency of sounds to avoid annoying sound disturbances, caused by magnetostriction 3. If too low the motor is pulsed, not continuous, because the motor’s inductance can not maintain th ...

... Lower Limits 1. Must be at least 10 times higher than the control system frequency 2. Higher than 20kHz – audible frequency of sounds to avoid annoying sound disturbances, caused by magnetostriction 3. If too low the motor is pulsed, not continuous, because the motor’s inductance can not maintain th ...

2011 ieee inTeRnaTional Solid-STaTe ciRcuiTS conFeRence 5

... equalizing filter code. According to our analysis, 3121 random samples are needed in order to achieve 2% variation in the largest histogram peak value with 99% confidence level using the approximation of normal distribution. Our prototype chip produces 4096 (12-bits) samples with the asynchronous cl ...

... equalizing filter code. According to our analysis, 3121 random samples are needed in order to achieve 2% variation in the largest histogram peak value with 99% confidence level using the approximation of normal distribution. Our prototype chip produces 4096 (12-bits) samples with the asynchronous cl ...

OpticalADC_Tutorial

... Structurally, the feedback loop in Figure 4 is identical to that of a conventional continuous-time (CT) ΔΣ ADC, except that the voltage-to-current conversion is accomplished by the optical modulator and photodiode pair, as opposed to a transconductance-C amplifier or an op-amp RC integrator. When th ...

... Structurally, the feedback loop in Figure 4 is identical to that of a conventional continuous-time (CT) ΔΣ ADC, except that the voltage-to-current conversion is accomplished by the optical modulator and photodiode pair, as opposed to a transconductance-C amplifier or an op-amp RC integrator. When th ...

MAX110/MAX111 Low-Cost, 2-Channel, ±14-Bit Serial ADCs General Description ____________________________Features

... The MAX110/MAX111 ADC converts low-frequency analog signals to a 16-bit serial digital output (14 data bits, a sign bit, and an overrange bit) using a first-order sigma-delta loop (Figure 1). The differential input voltage is internally connected to a precision voltage-tocurrent converter. The resul ...

... The MAX110/MAX111 ADC converts low-frequency analog signals to a 16-bit serial digital output (14 data bits, a sign bit, and an overrange bit) using a first-order sigma-delta loop (Figure 1). The differential input voltage is internally connected to a precision voltage-tocurrent converter. The resul ...

Pulse Width Mod A/D Conversion Techniques w

... Referring to the flow chart in Figure 3 , and the code listed in Figure 4 , the software counters Ton and TOTAL are first preloaded with the FF. The accumulator and register 0F1 are then loaded with 2 to provide for an initialization and final conversion cycle. Next, the L port is configured to comp ...

... Referring to the flow chart in Figure 3 , and the code listed in Figure 4 , the software counters Ton and TOTAL are first preloaded with the FF. The accumulator and register 0F1 are then loaded with 2 to provide for an initialization and final conversion cycle. Next, the L port is configured to comp ...

Engineer-to-Engineer Note EE-281

... signals should not be used as inputs when driven by an external device. HWAIT should not be used as an output if the value is critical during the booting phase of operation. GPIO signals used as outputs should have pullup or pull-down resistors to determine their state after reset. Outputs to be con ...

... signals should not be used as inputs when driven by an external device. HWAIT should not be used as an output if the value is critical during the booting phase of operation. GPIO signals used as outputs should have pullup or pull-down resistors to determine their state after reset. Outputs to be con ...

CMOS VLSI Design CMOS VLSI Design 4th Ed.

... Skew comes from differences in gate and wire delay – With right buffer sizing, clk1 and clk2 could ideally arrive at the same time. – But power supply noise changes buffer delays – clk2 and clk3 will always see RC skew ...

... Skew comes from differences in gate and wire delay – With right buffer sizing, clk1 and clk2 could ideally arrive at the same time. – But power supply noise changes buffer delays – clk2 and clk3 will always see RC skew ...

MAX11212 18-Bit, Single-Channel, Ultra-Low Power, Delta- Sigma ADC with 2-Wire Serial Interface

... interface with a clock input and data output. The output rate is predetermined based on the package option (MAX11212A at 120sps and MAX11212B at 13.75sps). 2-Wire Interface The MAX11212 is compatible with the 2-wire interface and uses SCLK and RDY/DOUT for serial communications. In this mode, all co ...

... interface with a clock input and data output. The output rate is predetermined based on the package option (MAX11212A at 120sps and MAX11212B at 13.75sps). 2-Wire Interface The MAX11212 is compatible with the 2-wire interface and uses SCLK and RDY/DOUT for serial communications. In this mode, all co ...

Adept Binary IO Reference Guide By Joel Malander Mechanical Engineering

... normal scan rate of signals by the software is 16 ms. This means if you are testing a object by moving the robot until a switch is activated, you should move the robot slowly to avoid smashing it into the object. In a case where one is trying to optimize this type of robot control, the first three s ...

... normal scan rate of signals by the software is 16 ms. This means if you are testing a object by moving the robot until a switch is activated, you should move the robot slowly to avoid smashing it into the object. In a case where one is trying to optimize this type of robot control, the first three s ...

Amptek Inc. Amptek Inc. 1 Activitity (of a radioisotope): The number

... Baseline (of a pulse): The instantaneous value that the voltage would have had at the time of the pulse peak in the absence of that pulse. In nuclear electronics, pulse heights are measured relative to the baseline, which is not necessarily zero. See Figure 1. Baseline restoration: A method used to ...

... Baseline (of a pulse): The instantaneous value that the voltage would have had at the time of the pulse peak in the absence of that pulse. In nuclear electronics, pulse heights are measured relative to the baseline, which is not necessarily zero. See Figure 1. Baseline restoration: A method used to ...

Evaluates: MAX5088/MAX5089 MAX5089 Evaluation Kit General Description Features

... power-good output signal of the MAX5089. The PGOOD output can be used as a system reset signal during power-up. PGOOD goes high after VOUT rises above 92.5% of the nominal set voltage. PGOOD is pulled up to VL (5.2V) using resistor R9. The PGOOD output is pulled low when VOUT drops below 92.5% of it ...

... power-good output signal of the MAX5089. The PGOOD output can be used as a system reset signal during power-up. PGOOD goes high after VOUT rises above 92.5% of the nominal set voltage. PGOOD is pulled up to VL (5.2V) using resistor R9. The PGOOD output is pulled low when VOUT drops below 92.5% of it ...

FINAL

... Masud Rizvi, Assistant professor, Faculty of Engineering, American International University- Bangladesh for his continuous support, patience and motivation. Without his support it would have been impossible for us to complete the whole work. We are also extremely indebted to our external supervisor ...

... Masud Rizvi, Assistant professor, Faculty of Engineering, American International University- Bangladesh for his continuous support, patience and motivation. Without his support it would have been impossible for us to complete the whole work. We are also extremely indebted to our external supervisor ...

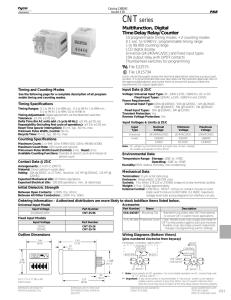

CNT series Multifunction, Digital Time Delay Relay/Counter

... duration equal to programmed time. Turning CONTROL off before accumulation of programmed time results in measured time total being held until CONTROL is again turned on and total programmed time value is reached. RESET input resets time value to zero and turns relay off if energized. Turning RESET o ...

... duration equal to programmed time. Turning CONTROL off before accumulation of programmed time results in measured time total being held until CONTROL is again turned on and total programmed time value is reached. RESET input resets time value to zero and turns relay off if energized. Turning RESET o ...

FD21972981

... however, even in these cases, the circuit is intended to be used within a larger system where some mechanism will drive the output, and they do not qualify as distinct from static logic. In contrast, in dynamic logic, there is not always a mechanism driving the output high or low. In the most common ...

... however, even in these cases, the circuit is intended to be used within a larger system where some mechanism will drive the output, and they do not qualify as distinct from static logic. In contrast, in dynamic logic, there is not always a mechanism driving the output high or low. In the most common ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.