ADF7010 - Searchdatasheet.Com

... Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, the latch being selected using the control bits. ...

... Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, the latch being selected using the control bits. ...

ADF7010 - Octopart

... Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, the latch being selected using the control bits. ...

... Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, the latch being selected using the control bits. ...

ADF7010 High Performance ISM Band ASK/FSK/GFSK Transmitter

... Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, the latch being selected using the control bits. ...

... Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches, the latch being selected using the control bits. ...

Chapter 11 - UNT College of Engineering

... • 54 series is manufactured to military specifications. • 74 series is manufactured to commercial specifications. • XX is the subfamily designation. • YY is the part designation. ...

... • 54 series is manufactured to military specifications. • 74 series is manufactured to commercial specifications. • XX is the subfamily designation. • YY is the part designation. ...

HMC679LC3C 数据资料DataSheet下载

... The HMC679LC3C is a T Flip-Flop w/Reset designed to support clock frequencies as high as 26 GHz. During normal operation, with the reset pin not asserted, the output toggles from its prior state on the positive edge of the clock. This results in a divide-bytwo function of the clock input. Asserting ...

... The HMC679LC3C is a T Flip-Flop w/Reset designed to support clock frequencies as high as 26 GHz. During normal operation, with the reset pin not asserted, the output toggles from its prior state on the positive edge of the clock. This results in a divide-bytwo function of the clock input. Asserting ...

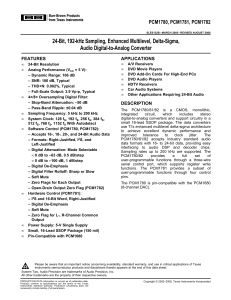

24-Bit, 192-kHz Sampling, Enhanced Multilevel

... system clock active and VCC > 3 V (typical, 2.2 V to 3.7 V), the power-on-reset function is enabled. The initialization sequence requires 3072 system clocks from the time VCC > 3 V (typical, 2.2 V to 3.7 V). After the initialization period, the PCM1780/82 is set to its reset default state, as descri ...

... system clock active and VCC > 3 V (typical, 2.2 V to 3.7 V), the power-on-reset function is enabled. The initialization sequence requires 3072 system clocks from the time VCC > 3 V (typical, 2.2 V to 3.7 V). After the initialization period, the PCM1780/82 is set to its reset default state, as descri ...

A low-power, blocking-capacitor-free, charge-balanced electrode-stimulator chip with less than 6nA DC error for 1mA full-scale stimulation

... the current transacted across a small series resistor, and feeding back finely discretized charge packets to equilibrate the charge. As mentioned, the success of this technique then depends on the ability to minimize the charge-injection, noise, mismatch, leakage and other sampling errors to achieve ...

... the current transacted across a small series resistor, and feeding back finely discretized charge packets to equilibrate the charge. As mentioned, the success of this technique then depends on the ability to minimize the charge-injection, noise, mismatch, leakage and other sampling errors to achieve ...

MAX196/MAX198 Multirange, Single +5V, 12-Bit DAS with 12-Bit Bus Interface _______________General Description

... ♦ 6µs Conversion Time, 100ksps Sampling Rate ...

... ♦ 6µs Conversion Time, 100ksps Sampling Rate ...

AD7870A: CMOS, Complete, 12-Bit, 100 kHz , Sampling ADC Data Sheet (Rev 0, 02/1992)

... Read. Active low logic input. This input is used in conjunction with CS low to enable the data outputs. Interrupt, Active low logic output indicating converter status. See timing diagrams. Clock input. An external TTL-compatible clock may be applied to this input pin. Alternatively, tying this pin t ...

... Read. Active low logic input. This input is used in conjunction with CS low to enable the data outputs. Interrupt, Active low logic output indicating converter status. See timing diagrams. Clock input. An external TTL-compatible clock may be applied to this input pin. Alternatively, tying this pin t ...

Buck Current/Voltage Fed Push-Pull PWM Controllers

... to Fig. 1, the synchronization threshold is 1.4V. The oscillator blanks any synchronization pulse that occurs when OSC is below 2.5V. This allows units, once they discharge below 2.5V, to continue through the current discharge and subsequent charge cycles whether or not other units on the CLKSYN bus ...

... to Fig. 1, the synchronization threshold is 1.4V. The oscillator blanks any synchronization pulse that occurs when OSC is below 2.5V. This allows units, once they discharge below 2.5V, to continue through the current discharge and subsequent charge cycles whether or not other units on the CLKSYN bus ...

Introduction to Fundamental Crystal Oscillators

... This capacitance is not related to any capacitance present in the crystals or the circuit but refers to the load capacitance used when crystals are measured in standard test sets. The preferred value of capacitance is 30 pF but crystals can be manufactured for other values. These circuits are design ...

... This capacitance is not related to any capacitance present in the crystals or the circuit but refers to the load capacitance used when crystals are measured in standard test sets. The preferred value of capacitance is 30 pF but crystals can be manufactured for other values. These circuits are design ...

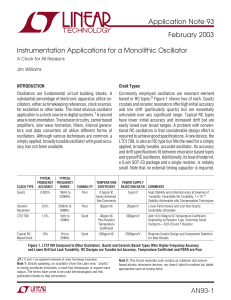

A Clock for All Reasons

... substantial percentage of electronic apparatus utilize oscillators, either as timekeeping references, clock sources, for excitation or other tasks. The most obvious oscillator application is a clock source in digital systems.1 A second area is instrumentation. Transducer circuitry, carrier based amp ...

... substantial percentage of electronic apparatus utilize oscillators, either as timekeeping references, clock sources, for excitation or other tasks. The most obvious oscillator application is a clock source in digital systems.1 A second area is instrumentation. Transducer circuitry, carrier based amp ...

Analog-Digital

... Conversion requires n clock cycles where n is the number of bits in the digital representation. ...

... Conversion requires n clock cycles where n is the number of bits in the digital representation. ...

Time-to-digital converter

In electronic instrumentation and signal processing, a time to digital converter (abbreviated TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases interpolating TDCs are also called time counters (TCs).TDCs are used in many different applications, where the time interval between two signal pulses (start and stop pulse) should be determined. Measurement is started and stopped, when either the rising or the falling edge of a signal pulse crosses a set threshold. These requirements are fulfilled in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.