* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download A Novel-Class AB Transconductor suitable for High Speed CMOS Operational Amplifier

Survey

Document related concepts

Mains electricity wikipedia , lookup

Current source wikipedia , lookup

Alternating current wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Negative feedback wikipedia , lookup

Buck converter wikipedia , lookup

Regenerative circuit wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Two-port network wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Transcript

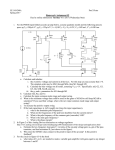

A Novel-Class AB Transconductor suitable for High Speed CMOS Operational Amplifier C. Sawigun and J. Mahattanakul Department of Electronics, Mahanakorn University of Technology 51 Chuem Samphan Rd. Nong-Chok Bangkok 10530 Thailand Tel: (662) 9883655 Ext. 211 Email: [email protected], [email protected] ABSTRACT A novel class-AB transconductance amplifier, suitable for the input stage of high slew rate CMOS operational amplifier is proposed. The proposed class-AB transconductor is realized from a differential pair of mixed translinear common-drain push-pull circuit. A high speed operational amplifier employing the proposed input stage and a complementary common –source high gain stage is presented. HSPICE simulation results of such an operational amplifier are given. structure, the output current of the proposed input stage can be many times higher than the bias current. Moreover, its symmetrical architecture allows the CMRR to be as high as that of the classical class-A differential pair. To verify the viability of the proposed input stage, a high speed op-amp comprising the proposed input stage and a simple complementary common-source high-gain stage is demonstrated. 2. PROPOSED INPUT STAGE Keyword: CMOS op-amp, High speed amplifier 1. INTRODUCTION It is commonly known that slew rate of an op-amp is limited by the current drive capability of its input stage [1-2]. For class-A circuit, a maximum output current is limited by bias current. On the contrary, class-AB input stage can provide the output current much higher than its bias current. So, in high speed application, the class-AB input stage has an advantage. Various structures of class-AB op-amps have been developed. In [3], comparison between three techniques for improving amplifier slew rate, namely dynamic frequency compensation, dynamic biasing [4] and non saturated input stage, have been reported. In the same year, the new class-AB principle [5] has been proposed. Although such an op-amp has high slew rate, it suffers from instability problem, which is caused by current feedback loop. Subsequently, a class-AB CMOS op-amp with novel self-biased input transistor was proposed in [6], its characteristics are almost identical to those of the op-amp proposed in [5], but the instability problem is eliminated. However, all of the reported high slew rate op-amps mentioned above are single stage. Thus their open-loop gains are not comparable to those of the traditional two stage op-amps and the miller compensation technique can not be applied. As a result, some close-loop performances such as accuracy, linearity, common mode rejection ratio (CMRR) and bandwidth of these class-AB op-amps are restricted. This paper proposes a novel input stage, which is intended for two-stage high speed CMOS op-amp. The input stage comprises a pair of a mixed CMOS translinear circuit and provides dual outputs. Thanks to its class-AB Io Io Vx Vin Iout1 Vin Ibias Io Io Iout2 Fig. 1: Input stage Figure 1 shows the proposed transconductor, comprising two mixed translinear loops, M1-M4 and M5M8 and two simple current mirrors M9-M10 and M11M12. In the following analysis, a symmetrical condition of transconductance parameter ( L) k N' W N ( L) = k P' W P =β (1) where kn' , p = 0.5µ n ' p Cox is assumed. For Vid = Vin + − Vin − and VE = I o β , it can be shown that when Vid < 2VE , M1-M8 are all in active mode (saturation), and Vx, the voltage at source terminals of M2, M4, M6 and M8, becomes input common mode voltage, i.e. Vx = Vic = 0.5 (Vin + + Vin − ) (2) According to (2), we find that for Vid < 2VE I D 2 = I D 8 = β ( 0.5Vid + VE ) 2 (3) and I D 4 = I D 6 = β ( 0.5Vid − VE ) 2 (4) Furthermore we can show that if Vid is increased so that Vid > 2VE , M4 and M6 will enter cut-off region. And if Vid is further increased so that ( Vid > Vtrn = 0.667 Vdd + Vtn − 2 Vtp - 2VE ) (5) M2 will move to triode mode. On the other hand, for Vid < −2VE , M2 and M8 will enter cut-off region and for ( Vid < Vtrp = 0.667 Vss + 2VE + 2Vtn − Vtp ) linear and the transconductance gain can be controlled by bias current Io. Now if Vid is increased so much that VG 2 ≥ Vdd - Veffb 2 , Mb2 will enter triode region and eventually Iout will be saturated when VG2 reaches Vdd (M1 is now cut-off). On the other hand, when Vid is decreased so that VG 3 ≤ Vss + Veffb 5 , Mb5 will enter triode region and eventually Iout will be saturated when VG3 reaches Vss (M7 is now cut-off). For single ended input, i.e. Vin + = Vid and Vin − = 0 the maximum output currents of the transconductor in Fig.1 can be shown to be ( ( I out max = β Vdd + VE − 2Vtn − Vtp )) 2 Vdd + VE − Vtp 1 + V + VE − 2Vtn − Vtp dd ( ) − 1 2 (11) By assuming that Vtn = Vtp = Vt , (11) can be simplified as I out max ≅ 0.172 β (Vdd + VE − Vt ) 2 (12) In a similar way, it can be shown that (6) I out min ≅ 0.172 β (VE − Vt − Vss ) 2 (13) M8 will move to triode mode. Summarily, it can be shown that I D 2 = I D8 2 Vid + β V E = 2 0 if - 2VE < Vid < Vtrn (7) if Vid ≤ −2VE and I D4 = I D6 if 0 2 = Vid − VE if β 2 2VE ≤ Vid Vtrp < Vid < 2VE (8) Assuming that M9-M10 and M11-M12 are ideal current mirrors, we have I out1 = I D 2 − I D 6 = I out 2 = I D 8 − I D 4 (9) From (7)-(9), we found that I out Gm1Vid if Vid < 2VE 2 (10) = Vid + VE if 2VE < Vid ≤ Vtr ( n , p ) sgn (Vid ) β 2 Where I out = I out1 = I out 2 and Gm1 = 2 β I o is a small signal transconductance gain of the input stage. It can be seen that when Vid < 2VE , i.e. I out < 4 I o , voltage-to-current transfer characteristic of the transconductor in Fig.1 is Fig. 2: I-V characteristics of the transconductor in Fig.1 for Vin+= Vid and Vin-= 0, Io = 10 µA, β ≅ 1000 µA/V2 and Vdd= Vss= 2.5V. Fig.2 shows HSPICE simulated I-V characteristics of the transconductor in Fig.1. The maximum output current can be seen to be 40 times higher than the bias current. 3. OP-AMP DESIGN EXAMPLE Fig.3 shows an op-amp, which is composed of the proposed transconductor as the input stage and a pushpull class-AB common-source M13 and M14 as a high gain stage. In order to maintain stability, compensation networks RA, CA and RB, CB are inserted across gate and drain terminals of M13 and M14, respectively [7-9]. It can be shown that the bias currents of the MOSFETs in the input stage, i.e. ID1-ID12 are b1Ibias where b1 = (W L )b 2,3 (W L )b5,6 = (W L )b1 (W L )b 4 (14) And the bias current of the MOSFETs in the high gain stage, i.e. ID3 = ID4 = b1b2Ibias where b2 = (W L )13 (W L )14 = (W L )10 (W L )12 (15) Vdd Mb2 Mb1 Mb3 M9 M13 M10 RA M1 M2 M6 Vx Vin+ Io M5 Vin- M3 M4 M8 M7 M11 M14 Mb6 Mb5 Vss Fig. 3: Op-amp circuit with proposed transconductor as the input stage ds ds id gs A A B B Gm1 C A, B (17) Simulation results of the op-amp in Fig.3 are shown in the next section 4. SIMULATION RESULTS Under ± 2.5V supply voltage, for RL = 25kΩ, CL= 5pF and, simulation results of the op-amp in Fig.3 were obtained by using HSPICE level 49 0.35 µm CMOS model parameter. Design parameters of the op-amp are shown in Table1. Simulated frequency response and transient response are shown in Fig.5 and Fig.6, respectively. Other simulation results are summarized in Table 2. Table 1: Design parameters Vout CB M12 ωu = CA RB Mb4 Where, RX = rds13 // rds14 // RL, R1 = rds10 // rds11 and R2 = rds8 // rds12. Using the miller approximation, the op-amp’s unity gain frequency can be found to be Design parameter M1, M2, M5, M6 M3, M4, M7, M8 M9, M10 M11, M12 M13 M14 Mb1 Mb4 Mb2, Mb3 Mb5, Mb6 R A / CA R B / CB Io Values 10µm / 1µm 30µm / 1µm 30µm / 1µm 10µm / 1µm 180µm / 1µm 60µm / 1µm 15µm /1µm 5µm /1µm 27µm /1µm 10µm /1µm 4kΩ / 0.35pF 3kΩ / 0.35pF 10µA out L ds ds ds ds L gs Fig. 4: Small signal equivalent circuit of the op-amp in Fig.3 Using the macro model in figure 4, the op-amp DC gain is found to be A0 = Gm1 RX ( gm13 R1 + gm14 R2 ) (16) Fig.5: Simulated frequency response of the op-amp in Fig. 5 where solid curve is magnitude response and dash curve is phase response. 5. CONCLUSION A novel class-AB transconductor, suitable for wide bandwidth, high speed CMOS op-amp is proposed. Such a transconductor is realized from a differential pair of a mixed translinear loop and thus its structure can be considered balance both vertically and horizontally. Consequently, when employed as an input stage on an opamp, not only high bandwidth and slew rate, but also high CMRR and low-offset can be achieved, as evident in simulation results. Furthermore due to its entire class-AB structure, the presented op-amp is also power efficient. (a) (b) Fig. 6: Simulated transient response of the op-amp in Fig. 5 when connected as unity gain buffer where dash curve is an input voltage and solid curve is an output voltage. (a) Step input voltage (b) 1V 5 MHz sinusoidal input voltage Table 2: Simulated results Characteristics DC open loop gain Common mode rejection ratio Unity gain frequency Phase margin Common mode input range Output swing Slew rate +/0.1% settling time +/Input offset voltage Power dissipation Values 87.6 dB 99.6 dB 73 MHz 66 degree -1.38V to 1.3 V -2.3 to 2.2 180 V/µs 116 V/µs 14.5 ns 16.3 ns -46 µV 0.625 mW 6. REFERENCES [1] P. R. Gray and R. G. Meyer, Analysis and design of analog integrated circuits, 3rd edition, John Wiley and Sons, 1993, ch. 9. [2] F. J. Lidgey and K. Hayathley, “Current feedback operational amplifier and application ,” Electronics and communication Journal, Aug., 1997, pp.178-182. [3] B. W. Lee and B. J. Shen, “A High Speed CMOS Amplifier with Dynamic Frequency Compensation,” Proc. IEEE Custom ICs Conference, 1990. [4] E. A. Vittoz, “The Design of High Performance Analog Circuits on Digital CMOS chips,” IEEE jour. Solid-State Circuits, vol. SC-20, No.3 June 1985. [5] G. A. Ludwig and W. Sansen, “Class AB CMOS Amplifiers with High Efficiency,” IEEE Jour. of Solid State Circuit, vol. 25, No. 3, June 1990, pp. 684-691. [6] F. Wang, R. Heineke and R. Harjani, “A Low Voltage Class AB CMOS Amplifier,” Proc. IEEE International Conference on Circuits and Systems, 1996, pp 392-396. [7] W. H. Ki, L. Der and S. Lam, “Re-Examination of pole splitting of a generic single stage amplifier,” IEEE Trans, Cir & Syst. I, vol.44, pp.70-74, Jan. 1997. [8] R. Hogervorst and J. H. Huijsing, Design of low power operational amplifier cells., Kluwer Acadamic Publisher, 1996. ch.5. [9] D. A. Johns and K. Matin, Analog integrated circuit design, John Wiley and Son, 1997, ch.5.