* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download PAPER

Wireless power transfer wikipedia , lookup

Ground (electricity) wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Utility frequency wikipedia , lookup

Power factor wikipedia , lookup

Electrification wikipedia , lookup

Electrical ballast wikipedia , lookup

Electric power system wikipedia , lookup

Audio power wikipedia , lookup

Power inverter wikipedia , lookup

Electrical substation wikipedia , lookup

Three-phase electric power wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Power engineering wikipedia , lookup

History of electric power transmission wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Current source wikipedia , lookup

Stray voltage wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Surge protector wikipedia , lookup

Schmitt trigger wikipedia , lookup

Voltage regulator wikipedia , lookup

Power MOSFET wikipedia , lookup

Voltage optimisation wikipedia , lookup

Power electronics wikipedia , lookup

Opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Alternating current wikipedia , lookup

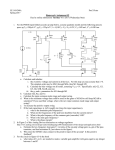

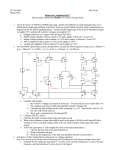

Power-Adaptive Operational Amplifier with PositiveFeedback Self Biasing Byungsub Kim, Soumyajit Mandal, Rahul Sarpeshkar Department of Electrical Engineering and Computer Science Massachusetts Institute of Technology Cambridge, USA [email protected] Abstract—This paper introduces a positive-feedback selfbiasing technique for operational amplifiers (op-amps) which enables their power consumption to adapt to their environment: The power consumption of one our op-amps scales almost linearly with load capacitance, input signal frequency, and output signal swing. A voltage follower built in the MOSIS/AMI 0.5µm process with our op-amp has a measured power consumption that varies between 1.38µW and 90µW, as the load capacitance varies from 1pF to 100pF. Our op-amp is primarily intended for low power switchedcapacitor applications. I. INTRODUCTION Increasing interest in distributed wireless systems, such as sensor networks [1] has created the demand for a low-power operational amplifier [2] which can adapt to various operating conditions. A traditional operational amplifier, because of its fixed bias current, consumes constant power regardless of the load capacitance, the input frequency, and the output voltage swing. However, many systems in the real world may have time-varying operating conditions [1, 3]. For example, the frequency and the amplitude of a sound signal may vary over a wide range. In a switched capacitor circuit, the load capacitance that an op-amp needs to drive changes between switching modes. A bias circuit blind to its varying environment will waste power. To eliminate unnecessary power consumption, an intelligent bias-control circuit must be able to adapt to its input and to its load capacitance. In this paper, an effective bias-control method for an op-amp using positive feedback is introduced. Measurements show that our technique is useful in circuits where the op-amp is used in a negative-feedback loop such as in voltage followers. The organization of this paper is as follows: In Section II, we discuss the time-varying nature of the power requirement for an op-amp. In Section III, we describe our op-amp’s design. In Section IV and V we present analysis and experimental results respectively. Section VI presents our conclusions. Figure 1. Example of operatation of S/H (a) in hold mode (b) and in sample mode (c). II. TIME-VARYING POWER REQUIREMENT Fig. 1 (a) shows a typical example of a sample-and-hold (S/H) circuit. In hold mode in Fig. 1 (b), the voltage across the feedback capacitor is stable, drawing no current from the op-amp. In sample mode in Fig. 1 (c), the differential input voltage of the op-amp changes abruptly with clock transitions and the op-amp conducts large amounts of current until its differential input voltage is near zero. If the output voltage changes by Vsw at every clock transition, we can easily derive that the ideal power consumption should be P= 1 T ∫ T 0 Vdd I out dt = Vdd CVsw f (1) where P, Vdd, C, Vsw, f (=1/T) and T are respectively the power consumption, the power supply voltage, the load capacitance, the output voltage swing, the switching frequency, and the clock period. Figure 2. Architecture of Positve Feedback Bias Control (a) and the voltage follower application (b). Traditionally, an op-amp’s bias current is fixed to meet maximum performance criteria and consumes worst case power given by Pmax = Vdd CmaxVsw max f max (2) In a real environment, if the load capacitance, the output voltage swing, and the switching frequency all decrease by a factor of 4, the op-amp will burn 64 times more power than is necessary. III. DESIGN A. Architecture Fig. 2 (a) shows the architecture of our positive feedback self-biasing op-amp. A positive-feedback bias controller measures the output current i1(t) of the op-amp and compares it with the bias current i2(t) of the op-amp. If |i1(t)| is larger than bi2(t) (b < 1), the bias controller decides that the bias i2(t) is too small, otherwise it decides that i2(t) is too large. Depending on this decision, the bias controller increases or decreases i2(t). This mechanism forms a positive-feedback loop since each increment of i1(t) raises i2(t) and thus the transconductance of the op-amp, further increasing i1(t). When our op-amp is used in negative-feedback configurations the technique is still potentially stable since negative-feedback attempts to reduce the voltage error vdiff(t) across the op-amp’s differential input terminals while the positive-feedback biasing modulates the rate-of-change of this reduction. Most op-amps operate in negative feedback, for example, the voltage follower in Fig. 2 (b). In this paper, we only discuss our idea for op-amps with capacitive load compensation. The dynamics for other configurations is beyond the scope of this paper. B. Circuit Implementation Fig. 3 shows the circuit implementation of Fig. 2 (a). The differential input stage of the op-amp has bias control transistors M1, M2, and M3. M1 is the control transistor which varies i2(t). M2 and M3 set maximum and minimum values Figure 3. Circuit implementation of Fig. 2 (a). imax and imin for i2(t), respectively. A current-replica circuit copies i1(t) and feeds it into a current rectifier which computes |i1(t)|. A current comparator compares |i1(t)| and b×{i2(t)-imin}+ib where ib is a very small amount of offset current (designed as 10nA) provided by M6. The currents imin and ib guarantee a minimum op-amp speed and a minimum comparator speed, respectively. The parameter b is set by adjusting the size of transistors of the current comparator and is 0.05 in this design. IV. ANALYSIS Because our bias current changes over a wide range, it is not easy to describe our op-amp with a simple linear model. We will use two models to describe our system. First, we will assume that i2(t) does not have the upper and lower bounds, imax and imin. Then, we will consider the effects of the upper and lower bounds. Fig. 4 shows a simplified model of Fig. 2(b) with the circuit of Fig. 3. By assuming that the parasitic capacitances are much smaller than the load capacitance, we can ignore the poles of the bias current controller and use constant gains A and b to model the current comparator, where A is the gain of the overall current comparator and b is the weight for i2(t). The transconductance of the transistors of the differential input stage in the strong inversion region, gm(i2(t)), can be expressed as g m (i2 (t )) = 2 µ Cox W i2 (t ) =γ i2 (t ). L (3) A. Without Bias Current Limiting By assuming that i2(t) is much larger than the offset currents imin and ib, we can derive the following equations. (4) i2 (t ) = A( vdiff (t ) γ i2 (t ) − bi2 (t )) Figure 4. System model of Fig. 2 (b) and Fig. 3. i2 (t ) = 1 2 γ vdiff (t ) 2 b2 ( Ab >> 1) (5) The square relationship between i2(t) and vdiff(t) in (5) shows that the bias current is very sensitive to the voltage error. A small voltage error in transition easily makes i2(t) reach a large value. From (5) and the system model, we can derive the following differential equation in which the polarity of the integrated term depends on the sign of i1(t). vin (t ) ± 1 t1 2 2 γ (vin (t ) − vout (t ) ) dt = vin (t ) − vout (t ) ∫ 0 C b (6) For a step input vin(t)=±Vswu(t), (6) gives us 1 vout (t ) = Vsw 1 − 2 for t > 0 ( Ab >> 1), γ Vsw t + 1 bC for t ≥ 0 ( Ab >> 1) . (7) (9) The power consumption is ∞ n P = f ∫ Vdd ni2 (t )dt = Vdd CVsw f 0 b n = 3.2 (i1 (t ) > 0 ) or n = 3.25 (i1 (t ) < 0 ) PSR = Vdd CmaxVsw max f max b Cmax Vsw max f max . = n / bVdd CVsw f n C Vsw f (11) B. With Bias Current Limittation In practical designs, i2(t) has upper and lower bounds imax and imin. The lower bound imin is either set by M3 or by M3 and the offset current of the current replica caused by mismatch. In measurements, imin=150nA. The upper bound imax is either set by current limiting transistors M2 and M5, or by the pull-up PMOS at the output stage due to mismatch. From (5), the values of voltage error vdiff(t) at the two bounds are (8) 1 1 for t > 0 ( Ab >> 1), i2 (t ) = 2 γ 2Vsw 2 2 2 b γ Vsw t + 1 bC i1 (t ) = bi2 (t ) Figure 4. Phases of op-amp operation with current limiting when a step input vin(t)=Vsw (Vsw > Vmax/b) is applied (10) where n is the ratio of the total power supply current to i2(t). Equation (10) shows that the power consumption of the voltage follower linearly depends on the load capacitance, the voltage swing, and the operating frequency. We define a power saving ratio compared to a fixed-bias ideal amplifier as: vmax = b γ imax , vmin = b γ imin . (12) Fig. 5 graphically shows four different phases of the operation of our op-amp when Vsw > vmax/b. During the t1 phase, i2(t) = imax, and the op-amp suffers from slew-rate limitations because gm×vdiff(t) is larger than imax. As vdiff(t) becomes less than vmax, the op-amp enters the t2 phase where i2(t) = imax and i1(t) < imax. Therefore, the voltage follower works as a normal first-order voltage follower. During t3, gm x vdiff(t) is between imin and imax, thus (6), (7), (8), and (9) are valid. Finally, vdiff(t) becomes less than vmin, resulting in i2(t) = imin. The voltage follower then returns to normal first-order dynamics with a small level of bias current imin. If the maximum allowable settling error is errVsw, then the total power consumed during the entire transition is i n 1 i 1 Ptot = nVdd CVsw 1 − min f + ln + min 2 − ln Vdd Cvmax f i b b i b max max n − 2 Vdd Cvmin f + nVdd imin b where f is limited by the maximum transition time tset: (13) Figure 5. Measured power consumption versus switching frequency with 0.5Vpp input voltage swing. Figure 7. Measured power consumption versus signal voltag swing with a 10 pF load. Figure 8. Measured input and output waveforms of the voltage follower. Figure 6. Measured power consumption versus the load capacitor with 0.5Vpp input voltage swing. t set V b = Cmax sw max + 2 γ vmax imax b 1 ln − 2 + 2 b γ vmin vmin + 1 . ln errVsw (14) Note that a large value for b results in power-efficient operation but reduces the maximum operating frequency because of the op-amp’s large settling time. Equation (13) shows that the power consumption is linear with signal frequency, load capacitance, and voltage swing. V. EXPERIMENTAL RESULTS We fabricated a voltage follower in the MOSIS/AMI 0.5µm process. The voltage follower has an on-chip load capacitor which can be configured as 1pF, 10pF, and 100pF by an external digital signal. Fig. 6 shows the measured power consumption versus frequency with three different load capacitance values. The linear relationship between the frequency and the measured power is clear in this figure. Fig. 7 shows the measured power consumption versus load capacitance. Fig. 8 shows the measured power consumption versus voltage swing. As expected, Ptot increases linearly with C, Vsw, f. However, Ptot is not accurately predicted by (13). This is because the assumption of no significant poles from the current comparator is not accurate. Fig. 9 shows an experimental waveform. It shows ringing because the comparator’s poles were not modeled. Finally, increasing b reduces Ptot at the cost of lowered bandwidth. VI. CONCLUSIONS In this paper, we have demonstrated the concept of positive-feedback self-biasing for operational amplifiers that adapts their power consumption to their environment. Measurements made on a test circuit show that the power consumption linearly depends on the signal frequency, load capacitance, and output voltage swing. Power-consumption scaling predicted by a theoretical analysis is in accord with experimental data. REFERENCES [1] [2] [3] A. P. Chandrakasan, R. Min, M. Bhardwaj, S. Cho, and A. Wang, "Power Aware Wireless Microsensor Systems," Keynote Paper ESSCIRC, Florence, Italy, September 2002. Jan Crols and Michel Steyaert, "Switcehd-Opamp: An Approach to Realize Full CMOS Switched-Capacitor Circuits at Very Low Power Supply Voltages," IEEE Journal of Solid-State Circuits, vol. 29, no. 8, Aug. 1004, pp. 936-942. Shih, E., S. Cho, F. S. Lee, B. H. Calhoun, A. P. Chandrakasan, "Design Considerations for Energy-Efficient Radios in Wireless Microsensor Networks," The Journal of VLSI Signal ProcessingSystems for Signal, Image, and Video Technology, vol. 37, no. 1, May 2004, pp. 77-94.