* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download FINAL08spb

Power inverter wikipedia , lookup

Scattering parameters wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Utility frequency wikipedia , lookup

Three-phase electric power wikipedia , lookup

Electrical ballast wikipedia , lookup

Stray voltage wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Negative feedback wikipedia , lookup

Voltage optimisation wikipedia , lookup

Two-port network wikipedia , lookup

Voltage regulator wikipedia , lookup

Mains electricity wikipedia , lookup

Alternating current wikipedia , lookup

Zobel network wikipedia , lookup

Regenerative circuit wikipedia , lookup

Power electronics wikipedia , lookup

Power MOSFET wikipedia , lookup

Current source wikipedia , lookup

Schmitt trigger wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

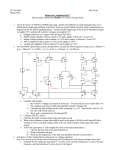

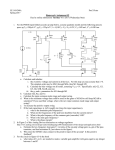

Prob. EECS140 Spring 2008 Final Name__________________________ SID___________________________ 1) Give a short answer for each of the following questions a) Why do we use a transistor as the tail current source on a differential pair instead of using a resistor? Score 1 /25 2 /50 3 /15 4 /50 5 /35 6 /25 Total /200 b) Give two benefits of using a current mirror as an active load of a single-ended output differential amplifier, instead of just supplying a DC bias voltage to the gates of the load transistors. c) You have a folded cascode op-amp with a total output capacitance of 200fF and a phase margin of 45 degrees. You’re happy with the performance of the amplifier, and have plenty of extra bandwidth, but you need to increase the phase margin to at least 80 degrees. What would you do? (be specific) d) Your friend from Stanford has designed a switched capacitor amplifer. You tell him that his op-amp gain is too low, and that he’ll never meet his gain accuracy spec. He says that he’ll just increase the switch period to give the amplifier longer to settle and it will be fine. Is he right? Why or why not? e) Your friend’s project in ee140 uses switches that are 5/0.5um and a feedback capacitor C1=1pF. The design is having problems with charge injection. What are two things that you can suggest to fix the problem, and why will they help? 2) For a folded cascode op-amp similar to the one used in class and driving a 10pF load, What is the effect of doubling the width of all devices? What is the effect of cutting the width and length of all devices in half (W/L remains constant). What is the effect of doubling Vdsat while keeping W and L constant? Assume the standard transistor model that we have used this semester, and that 10pF is large compared to all of the transistor capacitances. Example answers are 2x, no change, ½, etc. W--> 2W W,L --> W/2, L/2 Vdsat -->2Vdsat gm ro (transistors) Id Vdsat Ro (amplifier) Be careful! p1 u Av 2x 3) For battery operated devices it is common to put a small “sense resistor” in series with the positive terminal of the battery, and measure the millivolt-level signal across that sense resistor to keep track of current consumption. You need to design an amplifier to measure this voltage, and the topology will require your op-amp to connect at least one of its inputs to the sense resistor. Your amplifier will be powered from the same battery. It needs to have a closed loop gain of 100 from DC to 1kHz. The low frequency gain accuracy must be better than 2%. The load capacitance will vary from 0.1 to 10pF, and the amplifier must have a phase margin of 80 degrees when used in 100x feedback. a) Which of the following would work to implement the opamp? (circle the letters of those that would work) a) NMOS input folded cascode b) PMOS input folded cascode c) NMOS input 2 stage Miller compensated d) PMOS input 2 stage Miller compensated e) NMOS input telescopic cascode f) PMOS input telescopic cascode Why? b) What is the constraint on the unity gain frequency of your op-amp, u? c) What is the constraint on the low frequency gain of your op-amp, Av 4) For the circuit below, 1 and 2 are non-overlapping clocks and I2=2I1. You may assume that the op-amp is ideal. The diode has a saturation current IS. a) What is the voltage on the diode during 1? VDD What is its approximate temperature coefficient? I2 I1 2 b) What is the voltage difference between the voltage on the diode during 1 and 2? What is special about this voltage? What is it’s temperature coefficient? C1 C2 c) What is Vout during 1? d) What is the change in Vout from 1 to 2? e) Write an expression for Vout during 1. f) How would you pick the values of the capacitors to make Vout supply and temperature independent? Vout + - 1 g) Of the op-amp topologies listed in problem 3, which ones would work for this application? Write the letters: h) Implement this circuit in CMOS. Draw the entire circuit except the op-amp using at most 1 resistor and as many transistors as you want (and the diode and 2 capacitors). You can leave the op-amp itself as a triangle. i) Do you care if the resistor in part h has a bad temperature coefficient? Why/why not? 5) Given the cascode amplifier below, gm=1ms and ro=100k. Cgs=100fF and you may assume that all other capacitors are zero. CL=2pF. The current source has an output impedance of 10M. a. On the next page, plot the magnitude of the output impedance, Zout , vs. frequency. LABEL AXES CLEARLY b. What is the output pole frequency? I0 Zout c. What is the low frequency impedance seen looking into the source of M2? CL VBN M2 ZS2 d. What is the low frequency gain from Vin to the drain of M1? Vin M1 e. What is the low frequency input capacitance if Cgd=20fF? f. Plot the magnitude of the impedance looking into the source of M2, ZS2 , vs. frequency. LABEL AXES CLEARLY g. What is the second pole frequency? 6) In the switched-capacitor circuit below, all switches are NMOS devices with their bodies tied to ground. W/L for all devices is 10u/1u. C1=1pF. The clocks switch between Vdd and ground, and are non-overlapping. Assume our standard transistor model. Vdd=5V. a) what is the “on resistance” of switch M2? 1 C1 Vin b) If Vin=0, VA=0, and VB=1V just before 1, how long will it take from the rising edge of 1 until VB is less than 1mV? M1 2 VA 1 c) If Vin=VA=1V, what is the threshold voltage of M1? d) If Vin=VA=1V during 1, calculate Cgd1, and the voltage at node VA after the falling edge of 1. You may assume a very slow falling edge. e) What is the maximum voltage that VA can settle to during 1? How long will it take to settle to that value? Vout VB M2