* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Aatmesh_alicia_finalProject

Spark-gap transmitter wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Power engineering wikipedia , lookup

Electrical ballast wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Power inverter wikipedia , lookup

Utility frequency wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Current source wikipedia , lookup

Three-phase electric power wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Schmitt trigger wikipedia , lookup

Surge protector wikipedia , lookup

Stray voltage wikipedia , lookup

Voltage regulator wikipedia , lookup

Power MOSFET wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Integrating ADC wikipedia , lookup

Regenerative circuit wikipedia , lookup

Voltage optimisation wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Alternating current wikipedia , lookup

Mains electricity wikipedia , lookup

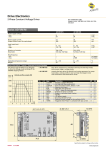

Wien bridge oscillator wikipedia , lookup

A Stable System Clock Generator Using Reference Clock Sampling Aatmesh Shrivastava Robust Low Power VLSI Group University of Virginia 23 May 2017 Alicia Klinefelter Robust Low Power VLSI Group University of Virginia 1 Outline • Motivation Crystal oscillator design and power consumption • Novel Circuit Architecture Three phases of operation viz calibration, conversion and retention phase • Circuit Design: Calibration Phase F to V converter Op-Amp VCO PTAT • Conversion and Retention Phase ADC Capacitive DAC R-2R DAC • Summary • References 23 May 2017 2 Motivation : Crystal Oscillator CRYSTAL • Almost all microprocessors, micro-controllers, PICs, and CPUs operate using a crystal oscillator. Crystal oscillator provides the reference clock. • Why?? Highest accuracy and frequency stability compared to any known oscillator. • Usually Fed to PLL to generate system clock, Sometimes can be used as is. • Frequency range from 10Khz-50Mhz CRYSTAL SYMBOL Board Hook-up 23 May 2017 Equivalent circuit Circuit Diagram of Xtal oscillator 3 Motivation : Crystal Oscillator Power • Crystal with Char. frequency of 32Khz to 50Mhz designed to obtain power. Most optimal point for oscillation. Crystal parameter obtained through vendor data-sheets. • Power dissipated ranges from 2.6uW @ 32Khz to 70mW @ 50Mhz. At 200Khz power ranges from 5uW to 30uW. • Crystal Oscillator consumes significant amount of power, critically impacts the power consumption of a system designed for lower power. 23 May 2017 4 Motivation : Proposed Circuit technique We propose a fully integrated reference/system clock circuit in CMOS. The circuit achieves a high frequency stability of +/-250ppm. We reduce the power consumption to a very low level < 2u Watts @ 200Khz Unlike a crystal oscillator the power consumption of proposed circuit does not scale up with the frequency because of the architecture. done Counter clock ADC Reg Block DAC done Clock coming from crystal or RF source F to V Converter 1 _ PTAT VCO 0 Op. Amp. Analog Mux + F to V Converter control out Proposed Circuit 23 May 2017 5 Circuit Operate in 3 Phases. • Calibration Phase. (done=0) A stable voltage is obtained at A, corresponding to reference frequency through crystal oscillator The amplifier controls the VCO. The VCO oscillation frequency is converted back to voltage using F to V converter. Feedback structure makes sure that A=E. (Need very done Counter Register Block done Clock coming from crystal or RF source F to_V Converter high gain amplifier to insure this) Calibration is completed once voltage at E becomes equal to A. DAC ADC 1 A PTAT Op. Amp. clock E + • Conversion Phase. • VCO 0 Analog Mux (done=0) Once E settles to value of A, Analog to Digital converter (ADC) and Digital to Analog Converter is enabled. These two blocks generates C which is equal to B with <1mV quantization error. Done signal goes high after conversion is done which causes MUX to select the DAC output. F to V Converter control out Retention Phase.(done=1) After done goes high, DAC is calibrated with desired o/p voltage for VCO. Clock can be turned off. The voltage at DAC can be maintained through bank of registers. All other blocks except DAC, PTAT and VCO can be disabled and are disabled. PTAT controls the temperature drift of VCO. 23 May 2017 6 Circuit Design: Frequency to Voltage converter[1] VDD 1 Is Clk T1 Clk MP1 MN1 2 T2 T1 C1 2 1 T2 1 MN2 C2 ClK 1 T1 2 T2 Circuit Diagram FVC Time • Figure shows Frequency to Voltage converter (FVC) schematic which is based on switching capacitors and current source. • F1 and F2 are pulse signals. F1 is generated after rising edge of Clock, while F2 is generated after falling edge of F1 23 May 2017 7 Functioning ClK 1 T1 2 T2 Time • When Clock is Low MP1 is on transmission gate T1 is off and MN2 is off. • C1 gets charged through Is. • When F1 goes high MP1 is off and MN2 is OFF. T1 is on and C1 and C2 Share charge as shown Is C1=C2 C1 C2 C2 • When F2 goes high T1 is off MP1 is off and MN2 is ON which discharges C1 to ground. • This process is repeated and eventually charges C2 to the maximum Voltage of C1. • A voltage thus inversely proportional to frequency is obtained at C2. 23 May 2017 8 Output waveforms Steady state internal net waveforms A OUT Out build-Up 23 May 2017 9 Circuit Design: Folded Cascode Operational Amplifier VDD VDD INN MP2 MP1 + _ OUT INP VDD VM Cp C OUT VDD M1 A B VM MN1 MN2 • • • • Gain of the amplifier gets multiplied through each stage. Very High gain. Quiescent current = 200nA Since Op-amp is used in feedback structure, stability of the system is achieved Cp. Compensating Cap VM=VDD/2 23 May 2017 10 Stability of the system Feedback path Proposed Circuit Because of the feedback, stability sims were done. 23 May 2017 11 Insuring Stability of the system Pole to replace VCO and F to V for stability analysis REF REF _ + A VCO F to V OUT _ A OUT + = Feedback portion of the system open-loop ac analysis reduction for the system. • As voltage at A changes, frequency of VCO changes and because frequency changes voltage at OUT will changes. In other words voltage at A changes voltage at OUT. • This means there is a phase difference b/w A and OUT or there is a pole b/w A and OUT. • OUT being feedback net so this pole impacts the stability. • We obtain the delay from A to OUT. Using the delay number we approximate the pole by RC and perform open loop AC analysis. 23 May 2017 12 Stability Analysis Phase Margin= 80 DC Gain= 100 dB 23 May 2017 13 Voltage Controlled Oscillator VP VP = MP _ IN VN OUT1 OUT5 INV BUF + VN OPAMP MN Current Mirror Delay Element in VCO Functioning • Current sources MP and MN determine the delay and hence frequency of VCO. • As Output of OPAMP increases, VN increases and VP decreases. • Current sources MP and MN drive increases, which increases frequency. • Five such delay elements are used. 23 May 2017 14 Voltage Controlled Oscillator Voltage Controlled Oscillator VCO VCOoutput outputatatVN=700mV VN=883mV f=200Khz Effect of Temperature variation on VCO • After the calibration phase, VCO input would remain at constant voltage. • Temperature will cause current source to vary. • This will change the frequency. Frequency changes from 220Khz to 200 Khz from 0 to 100oC Sweeping temperature for IN. • With increasing temperature IDRIVE of NMOS drops Removing effect of Temperature: PTAT[2] • Idrive reduces with temp. Use PTAT to control temperature drift. • Add current of MOS and PTAT to get zero temperature coefficient. (ZTC) MP1 Start-up IB • As Temperature increases, the Threshold voltage of transistor decreases. MP2 1 1 IB • Current in the circuit is given by MN1 MN2 1 M>1 • With temperature VT of MN1 drops hence VGS, consequently VB increases increasing IB. VGS RB 23 May 2017 VB 17 PTAT Output Sweeping temperature for IPTAT. 23 May 2017 18 Getting ZTC currents for VCO Variation of Current sources in VCO. • Current in VCO’s current source vary by 3nA over ~400nA over a temperature variation of 0 to 100oC 23 May 2017 19 VCO output at 0, 50 and 100 Degrees • With change is temperature frequency of oscillation changes from 200 Khz to 201 Khz. Frequency stability = +/-250ppm 23 May 2017 20 Clock coming from crystal or RF source F to V Converter FV1 _ VCO_in Op. Amp. Putting it together: Calibration Phase PTAT VCO + FV2 F to V Converter out control VCO_in FV1 FV2 FV2=FV1 Clock coming from crystal or RF source F to V Converter _ Op. Amp. Putting it together: Calibration Phase CLKIN PTAT VCO + VCO_OUT F to V Converter out control ADC Architectures Sigma Delta Successive Approximation High Accuracy Determined by DAC and Comparator Higher Lower Conversion Time Fast (due to oversampling) N*(cycle time) No pipeline delay Typical Bit Range > 10 bits < 15 bits High Low Accuracy Power Complexity 23 May 2017 23 Successive Approximation (SAR) ADC • Begins by making assumptions about bit values starting with the MSB and forcing 1000…00 (Vref/2)onto the DAC. • If this voltage is above the analog input, the assumed bit goes to 0, else it remains 1. • Then assumptions are made about all bits till the LSB and checked so the system “zeros in” on the result. 23 May 2017 24 SAR ADC Block Diagram [4] • Comparator: Compares assumption coming from DAC and input analog voltage. • DAC: Takes current assumption bits and turns them into analog voltage for comparison in next stage. • SAR Logic: Takes output of comparator (0 or 1) to determine the next bit value and set the next bit assumption. 23 May 2017 25 Comparator • Three op amps used (two P, one N) 23 May 2017 26 The Charge Scaling 10-bit DAC [3] Charge Scaling DAC Output 0.6 0.5 voltage (V) 0.4 0.3 0.2 0.1 0 -0.1 0 0.002 0.004 0.006 time (ms) 0.008 0.01 0.012 • Capacitor DAC acts as both DAC and sample-hold circuit. • Design consideration: base cap size, C. • Needs to be reset before use (discharge caps). 23 May 2017 27 ADC Converging with Comp. Output Analog Ref. Comp. Out DAC Out 1 voltage (V) 0.8 0.6 0.4 0.2 0 0 0.2 0.4 0.6 time (ms) 0.8 1 1.2 -3 x 10 • DAC makes series of guesses. – If (guess voltage) > (analog input) over-approximation. This bit is 0. – Else the guess is below the expected value. This bit is 1. 23 May 2017 28 The R-2R 10-bit DAC [3] R-2R Ladder DAC 0.5 0.45 0.4 voltage (V) 0.35 0.3 0.25 0.2 0.15 0.1 0.05 0 0 • • • 0.002 0.004 0.006 time (ms) 0.008 0.01 0.012 Simple voltage divider network. Does not require initialization signal and does not need to be periodically refreshed. Tradeoff: branch current vs. resistor size 23 May 2017 29 The ADC/DAC Network • Active Power consumption: 550nA • Technology: IBM 130nm • Supply Voltage: 1 V • Sampling Rate: 20 kHz • Future optimizations: – Low-power optimization for ADC 23 May 2017 30 Summary • Novel low power, high stability clock circuit is proposed. • The circuit achieves a frequency stability of +/-250ppm. • Power in calibration-phase = 5uW, retention-phase = 2uW. • Similar to crystal in stability (+/-100ppm) better than crystal in terms of power consumption. Power consumption does not scale up with frequency unlike crystal oscillator 23 May 2017 31 Questions? 23 May 2017 32 References [1] A Djemouai et al. “New Frequency Locked Loop based CMOS frequency to voltage converter: Design and Implementation” IEEE Transactions on Circuits and systme II: Analog and Digital Signal Processing. vol. 48 No-5, May 2001. [2] D. Liu et al. “A simple voltage reference circuit using transistor with ZTC point and PTAT current source” IEEE J Solid-State Circuits vol. 29 pp 663- 670, June 1994. [3] Allen E. and Holberg D. “CMOS Analog Circuit Design” Oxford University Press, New York, 2002. [4] Simone Gambini and Jan Rabaey. “Low-Power Succesive Approximation Converter with 0.5 V Supply in 90 nm CMOS” IEE Transactions of Solid-State Circuits. Vol. 42, no. 11, Nov. 2007. 23 May 2017 Aatmesh [email protected] 33 BACK UP 23 May 2017 Aaatmesh 34 Crystal Oscillator: Design RBIAS CL CL 23 May 2017 • During start-up phase RBIAS( extremely high value) keeps the Inverter at VM. • Oscillation builds up with noise. • The crystal passes only the resonant frequency voltage, which gets amplifier. • The amplified value gets passed through crystal which again gets amplified. • This goes on till Oscillation saturates. Aatmesh [email protected] 35 Pole to replace VCO and F to V for stability analysis REF _ + A VCO F to V REF OUT _ OUT A + = Feedback portion of the system Configuration for open-loop ac analysis of the system. A to OUT delay = 100uS So if R=10K C=100pF We choose R=50K and C=100pF for our ac analysis 23 May 2017 Aaatmesh 36 Addressing variability: Global variation • Global variation will cause the shift in the current in PTAT which can cause the temperature compensation to drift either in CTAT or PTAT direction. MP1 Start-up 1 MN2 1 MP2 1 MN1 M>1 IB • Vary RB through bit control to affect a good ztc point. RB 23 May 2017 37 Addressing variability: Local Mismatch • Local mismatch can cause an offset which can cause frequency of VCO to be different from Clock. done Counter clock ADC Reg Block DAC done Clock coming from crystal or RF source F to V Converter FV1 1 _ PTAT VCO 0 Op. Amp. Analog Mux + FV2 F to V Converter control out • If we bit control the current source of FV2, we can set f(Clock)=f(VCO). 23 May 2017 38 Solution for high frequency clocks • In order to get higher frequency output divide the VCO output by K just like a PLL. • This would have very little impact on over all power consumption of the system. done Counter ADC clock Reg Block DAC done Clock coming from crystal or RF source F to V Converter 1 _ PTAT Op. Amp. Analog Mux + Divide/K control 23 May 2017 VCO 0 F to V Converter out 39