* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download 7.5 Design the circuit in Fig. P7.5 to obtain a dc voltage of +0.2V at

Immunity-aware programming wikipedia , lookup

Power inverter wikipedia , lookup

Electrical ballast wikipedia , lookup

Pulse-width modulation wikipedia , lookup

History of electric power transmission wikipedia , lookup

Current source wikipedia , lookup

Electrical substation wikipedia , lookup

Regenerative circuit wikipedia , lookup

Power MOSFET wikipedia , lookup

Power electronics wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Buck converter wikipedia , lookup

Alternating current wikipedia , lookup

Stray voltage wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Surge protector wikipedia , lookup

Voltage regulator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Schmitt trigger wikipedia , lookup

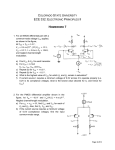

7.5 Design the circuit in Fig. P7.5 to obtain a dc voltage of +0.2V at each of the drains of Q1 and Q2 when vG1 = vG2 = 0V. Operate all transistors at Vov=0.2 V and assume that for the process technology in which the circuit is fabricated, Vtn= 0.5V and µn Cox = 250 µA/V2. Neglect channel-length modulation. Determine the values of R, RD, and the W/L ratios of Q1, Q2, Q3,and Q4. What is the input common-mode voltage range for your design?