* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Presentation Title Here

Electrical ballast wikipedia , lookup

Ground (electricity) wikipedia , lookup

Three-phase electric power wikipedia , lookup

Variable-frequency drive wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electromagnetic compatibility wikipedia , lookup

Power inverter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Electrical substation wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Current source wikipedia , lookup

Integrating ADC wikipedia , lookup

Stray voltage wikipedia , lookup

Two-port network wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Alternating current wikipedia , lookup

Power MOSFET wikipedia , lookup

Power electronics wikipedia , lookup

Voltage optimisation wikipedia , lookup

Voltage regulator wikipedia , lookup

Buck converter wikipedia , lookup

Surge protector wikipedia , lookup

Mains electricity wikipedia , lookup

Schmitt trigger wikipedia , lookup

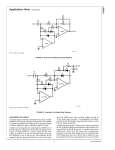

Understanding and Protecting Against Electrical Overstress (EOS) of Operational-Amplifiers By Thomas Kuehl – Senior Applications Engineer Precision Analog – Linear Applications Engineering This is your IC This could be your IC after an electrical overstress event! Presentation Subjects • ESD and EOS definitions • Amplifier input range • ESD models • Internal ESD and consequently EOS protection circuits • Amplifier EOS operating situations • External EOS protection ESD and EOS: What’s the difference? • Electrostatic Discharge (ESD) – The transfer of electrostatic charge between bodies or surfaces at different electrostatic potential. • Electrical Over Stress (EOS) – The exposure of an item to current or voltage beyond its maximum ratings. ESD High voltage (kV’s) Short duration event (1-100ns) Fast edges Low power Out of circuit event EOS Low voltage >Vs Longer duration event Low power In-circuit event Two very different environments Handling and assembly environments ESD PC Board EOS -5V bus V1 5 L1 50n C1 100n R2 10k R1 1k OP2 !OPAMP OP1 !OPAMP - - Vout 10V + + 0V + C2 100n + + VG1 R4 1k R3 1k L2 50n +5V bus V2 5 The TI data sheet Absolute Maximum Ratings is a good place to check and assure EOS problems are avoided Input voltage range of an op-amp + +2kV– +100V ESD protect region ≈ Safe with Rs +5.5V +5.0V Non-linear input In-circuit max positive Pos Safe Pos rail OPA735 low Drift CMOS Op-amp +3.5V U1 OPA735 - Rs 1k * 0V -0.1V -0.5V + Neg rail Neg safe + Input voltage CMV input range Vo + C1 100n Vi 2.5 V1 5 Safe with Rs -5.0V ≈ -100V– ESD protect region -2kV _ In-circuit max negative * Selected to limit input current to 10mA max. ESD Stress Models R1 1.5k L1 7.5u 2 + C1 100p d (i) R * di 1 * i 0 2 L dt LC dt VG1 ESD model R L C V Human Body Model HBM 1.5 kΩ 7500 nH 100 pF ≥ 2kV Machine Model MM 20 Ω 750 nH 200 pF 100 - 200V Charged Device Model CDM 20 Ω 5 nH 2-10pF 200V - 1kV Human Body model Human Body ESD Model modeled in TINA Spice DUT IC1 2kV IC L1 7.5u R1 1.5k SW1 VF1 t Rdut 10 C2 2p C1 100p 1.5 T + A 1.0 AM1 (Amps) Rdut is the “on” resistance of an ESD protection circuit 500.0m Rdut = 10 Ohms 0.0 15.0 10.0 VF1 (Volts) 5.0 0.0 0 50n 100n Time (s) 150n 200n AM1 Machine Model Machine ESD Model modeled in TINA Spice DUT IC1 200V IC L1 500n R1 10 SW1 VF1 t Rdut 10 C2 2p C1 200p + 4.0 T A Rdut = 10 Ohms 2.0 AM1 (Amps) 0.0 Rdut is the “on” resistance of an ESD protection circuit -2.0 40.0 20.0 VF1 (Volts) 0.0 -20.0 0 50n 100n Time (s) 150n 200n AM1 CDM - ESD by induction T 400 Cp: 2p[F] Cp: 4p[F] Cp: 6p[F] Voltage (V) 200 Charge Device Model modeled in TINA Spice 0 VG1 IC1 IC L1 5n R1 20 SW1 VF1 250V -200 0.0 Rdut 10 C1 10p 2.0n Time (s) 3.0n 4.0n 2.0n Time (s) 3.0n 4.0n T 5.0 2 - 10pF Cp: 6p[F] Cp 2p Cp: 4p[F] Cp: 2p[F] + A AM1 Current (A) 2.5 Rdut is the “on” resistance of an ESD protection circuit 1.0n 0.0 -2.5 -5.0 0.0 1.0n Common input/output ESD protection circuits Input steering diodes CMOS input/output protection Vdd / Vcc bus output pad C1 20f Pad/Pin D2 1N914 D1 1N914 R1 190 R3 74 C1 20f R1 1k T4 !NPN D3 1N914 Vcer input clamp Rb SCR R4 9.4 R4 10.2 Input Pad input pad C1 20f V- V- IC level SCR model is more complex D1 PMLL4448T1 Noname D2 PMLL4448T1 Noname Vee R4 9.4 OR R2 74 -Vdd / Vee bus Pad R4 9.4 R4 9.4 V+ R4 9.4 Absoption circuit R4 9.4 Pad R4 19.5 Ouput Pad input or output circuit Supply clamp circuits Bipolar BVcer Clamp NPN bipolar on high-speed process V+ Avalanche generating current - internal or external source IS1 1u T1 !NPN RB s et by des ign and process RB 500 V- NMOS Clamp V+ T2 Noname V+ ≈ T3 !NPN Rsub 500 RB 500 V- NMOS parasitic NPN trans istor V- ON → ← OFF NMOS parasitic bipolar transistor Gate Drain (collector) n Source (emitter) n IDS p IC Isub Rsub Sub (base) P-sub/epi A commonly applied ESD protection method for analog integrated circuits D3 1N4148 Rs 1k D1 1N4148 ultra low leakage diodes In+ + In- - Output protection D5 1N4148 V+ Input protection IOP1 V- D6 1N4148 D4 1N4148 Rs 1k D2 1N4148 Vo T1 !NPN Rb 2k Power supply absorption device INA168 ESD cell layouts Input pin ESD2 N-sinker – BL ESD1 NPN B-E Supply clamp NPN transistor / resistor Output pin ESD7 NPN B-E ESD8 N-sinker – BL The ESD protection paths V+ pin at GND D5 1N4148 D3 1N4148 Rs 1k + Vout at GND Vo Rs 1k ESD pulse source IOP1 D6 1N4148 In- D4 1N4148 VG1 D2 1N4148 + In+ D1 1N4148 V+ V- V- pin at GND T1 !NPN Rb 2k Input overdrive may activate ESD protection circuits VG2 unintended trans ients, noise impuls es , etc. V- U1 OPA364 Vi n+ VG1 - Vo TL1 VG2 R3 10k + V+ V+ 0.00 VG2 500.00m 0.00 3.25 VG1 intended linear range signal Vp = 2.25V, f = 100Hz V1 2.5 2.25 -2.25 1.00 + + + VG1 T Vin+ 500.00m -2.25 2.50 V2 2.5 Vo V- 0.00 -2.50 0.00 C1 100n 5.00m C2 100n VG1 + VG2 sum may activate ESD circuit on peaks 10.00m Time (s) 15.00m 20.00m ESD cell paths may be activated during an EOS event C2 1u + * L4 10n D5 1N4148 L2 50n + T1 can become a near short between supplies! Vout + Rs 1k D3 1N4148 Intended signal D1 1N4148 V2 5 - D6 1N4148 Input EOS source D4 1N4148 VG2 Rs 1k D2 1N4148 + VG1 IOP1 T1 !NPN RL 10k Rb 2k RF 10k RI 1k V1 5 * L1 50n L3 10n C1 1u - + *may no longer represent a nearzero impedance at high frequencies A supply clamp transistor failure during resulting from an input EOS/ESD event One channel of RGB amplifier application R1 500 R2 500 C2 10u V- - + TL1 GRN OUT + + GRN IN R4 75 V+ R3 75 OUT + C1 10u + OP1 !OPAMP VG1 R5 2k TERM T1 !NPN V+/V- wall-wart power supply without on/off switch Vcer clamp transistor EOS-related CMOS operational-amplifier field failures • • • TI quad CMOS operational amplifier failing unexpectedly in air conditioner application TI FA report indicated the operational amplifier die had carbonized material on die and pin 4 (V+) to pin 11 (V-) short EOS analysis of the customer application input and output ESD circuits did not reveal any likely candidates EOS-related CMOS operational-amplifier field failures 20 Vpk EOS on V+ line • A request for the Field Applications Engineers to observe and monitor the amplifier pins during the various operational cycles was made and provided • They found that a 20 Vpk pulse was appearing on the V+ line during operation of the air conditioner. The nominal supply voltage was +5 V • The EOS was causing either the supply-to-supply ESD clamp to break down, or voltage breakdown of the amplifier transistor structures • A higher voltage operational amplifier and a transient voltage suppressor on the V+ line were recommended Input current limiting by external series-R Where does the 10mA IOVERLOAD maximum originate? Parasitic circuit latch testing VS1 5 Compliance Range +/-7.5V I max 150mA VCCS1 + Pi n under test + A AM1 + + VG1 U1 OPA348 + - + Ouput floats during input pi n tests - I/O hi gh SW1 + I/O low Input pins connected together during output pin test VS2 0 Current injection latch test The continuous input overload current is set to < 1/10th the JEDEC maximum latch test current (t ≤ 10ms) Watch Vin during power up! Iin excessively high while supply ramps T 30.0m AM115.0m 0.0 3.50 VG1 1.75 0.00 5.00 VG2 2.50 0.00 3.50 VM1 1.75 0.00 0 10m 20m 30m Time (s) 40m 50m Instrumentation amplifier input protection V+ Vi n- Over-Vol tage Protection IOP1 + R3 60k R5 60k IOP3 R2 25k - RG 25k R1 25k EXT - R4 60k R6 60k Ref + Vbias 0 IOP2 Vbias V- A1 + IS1 10u Ib Comp 1n + A3 +i n IOP2 A3 -in + Vi n+ T1 !NPN Vd/2 1 C1 6p R1 25k RG 25k Vcm 0 + Over-Vol tage Protection + + Vi n+ Vo Vd/2 1 Over-Vol tage Protecti on Vi nT1 Noname T2 Noname D1 1N914 Ext A2 + Mirror of A1circuit Excessive differential input over-voltage Possible occurrences Bipolar input operational amplifier – – R1 500 T 10 V- U1 OPA227 90% - Vo + 8 + VG1 R2 1k V1 15 V+ R3 1k Input-output voltage difference 6 SR = 2.3V/us 4 Vo V2 15 V+ VC1 100n Voltage (V) + VG1 When operating an operational amplifier as a comparator During slewing C2 100n 2 10% 0 0.0 1.0u 2.0u 3.0u 4.0u Time (s) Plot for illustrative purposes only! 5.0u OPA277 input-to-input differential over-voltage protection modern bipolar op-amps have input clamps R1 500 V2 15 Iin Gain stages and bias circuits 20mA max T28 !NPN T41 !NPN T23 !NPN Vo VinRL 1k T44 !NPN + D3 1N914 D2 1N914 D1 1N914 D4 1N914 IS1 100u Pulse Vin+ Source VG1 VG1 = 2VD + (Iin R1) + Vo V1 15 If VO = 0V, then: Iin = (VG1 – 2VD) ∕ R1 Input overdrive of CMOS rail-to-rail IO chopper amplifiers Back-to-back clamp diodes are inherent and internal to the chopper switch structures • • • • • When Vin exceeds a Vcm maximum Vo is forced to an output rail level The op-amp is forced outside of its linear operating range The feedback loop collapses and an input differential voltage develops One clamp diode or the other becomes forward biased and the input bias current can increase tremendously This may limit the use of this type of operational amplifier as a comparator Overload Recovery Auto-zero CMOS Operational-amplifiers Positive input +50mV 0mV OPA335 Av = -50V/V 0V + R1 2k VG1 Negative output R2 100k ≥ -2.5V U1 OPA335 V- Stepped from 50mV to 0mV + + + - C1 100n V1 2.5 V2 2.5 C2 100n V- Vin ≥ Vs / Gain VM1 Negative input 0mV -50mV ≤ 2.5V Positive output 0V Output inversion during input overdrive U1 OPA234 +4.5V Vi n 5Vp-p + 2.0Vdc - VG1 + + + + VM1 - -0.5V C1 10n +4.5V VG1 R1 50 V1 5 VM1 0V Output inversion Supply pin over-voltage protection L1 100u LOAD Rs 5 C1 1u + VG1 5V Power supply T with an RLC filter Transient amplitude effectively reduced + VM1 - 10.0 Smoothing a transient • RL 1k 1us transient riding on 5V supply voltage VG1 VG1 7.5 5.0 5.5 VM1 • Ringing dependent on RLC values and load R • Amplifier PSRR becomes important VM1 5.0 4.5 0 20u 40u 60u Time (s) 80u 100u Supply pin over-voltage protection LOAD Rs 10 C1 10n + VG1 RL 1k 5V Power supply + VM1 Vz = 6.8V Z1 1N5342 T Transient voltage suppression (TVS) diode • 6.8V- 550V reverse standoff voltage •Unidirectional & bidirectional models •Ppk = 1.5kW (10 x 1000us) @ 25C 10.0 5V 1us transient riding on +5V supply line VG1 VG1 7.5 5.0 7.0 zener diode used in simulation no TVS model available VM1 VM1 5.8 •Cj ≥ 1nF @ 20V •Littlefuse no. 1.5KE6.8, etc. 4.5 0 20u 40u 60u Time (s) 80u 100u Supply pin over-voltage protection Features • Multilayer ceramic construction • Operating voltage range VM(DC) = 5.5 to 120V • Non-repetitive surge current (8/ 20us) • Non-repetitive energy (10/ 1000us) • response time <1ns for zinc oxide • Inherent bidirectional clamping • Wider temperature range and flatter response than solid-state TVS Externally connected input protection devices Transient voltage suppressors For CMOS, bipolar and SiGe Features: Available from 5.6 to 18V DC working voltage ≤ 18V AC working voltage ≤ 14V watch capacitance Turn-on-time <1ns Repetitive spike capability uA J A pF Externally connected input protection devices Externally connected input protection devices Schottky diodes provide enhanced input protection V1 5 SD1 BAS40 C1 100n U1 OPA374 + + SD2 BAS40 VG1 R1 5k + + - R2 5k VM1 - Features: • Forward voltage VF ≤ 380mV, IF = 1mA • Forward current IF = 200mA max (cont.) • Leakage current * IR ≤ 100nA, VR = 30V • Diode capacitance Ctot ≤ 5pF, VR = 0V * A small-signal silicon diode (IN4148) will likely turn on at lower voltage than the internal ESD silicon diode and may exhibit lower leakage current than a Schottky diode. Externally connected input protection devices An important point about added protection devices in the signal circuit • Protection components such as transient voltage suppressors (TVS), diodes and zener diodes all exhibit capacitance even when biased off • The capacitance will vary to some extent with the voltage applied across the protection device • Most often the capacitance does not have a linear capacitance to voltage relationship (voltage coefficient) • This non-linear capacitance to voltage relationship may increase distortion in the protected circuit • It will be most evident in a very low THD circuits, but may not degrade performance significantly Power Line Communications (PLC) EOS environment – IEC61000-4-5 Open-circuit surge pulse test 4kV, 1.2us tfront, 50us thalf-value PLC – EOS protection Actual protection scheme will vary with application and layout High voltage MOV and low-voltage TVS clamping Fast rectifier and Schottky clamps The internal output ESD cell is unlikely to withstand the open-circuit HV pulse - latching is probable In Summary • EOS and ESD events may activate ESD protection but result in different outcomes • Internal ESD circuits may sufficiently handle EOS • Be aware of unique EOS situations such as power up and input slewing • External EOS protection circuits will be required if device damage is likely to occur without it