* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download 2. The MOSFET

Survey

Document related concepts

Current source wikipedia , lookup

Power electronics wikipedia , lookup

Alternating current wikipedia , lookup

Voltage regulator wikipedia , lookup

Voltage optimisation wikipedia , lookup

Stray voltage wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Semiconductor device wikipedia , lookup

Mains electricity wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Two-port network wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Current mirror wikipedia , lookup

Transcript

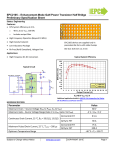

2. The MOSFET In the first chapter we adopted a simplified picture of the Metal-OxideSemiconductor Field Effect Transistor (MOSFET) as a switch – a switch that could be turned ON and OFF by means of an electrical control voltage. Furthermore, we tried to make feasible that such a simple model is sufficient for understanding how to design CMOS logical gates. However, the switch model is not detailed enough for evaluating circuit performance such as switching speed of a CMOS logic gate. Therefore, we shall look more into details of MOSFET models for integrated circuit design. This chapter will be far from complete when it comes to MOSFET modeling, but it will provide a useful platform for the beginner circuit designer. Since the MOSFET has two ports, the main port and the control port, a two-port representation as shown in Fig. 2.1 is useful. Here, the gate-tosource voltage VGS is the input control voltage not only used for turning the device ON or OFF, but also for controlling to what level the device is ON. Mathematically, both port currents IGS and IDS are nonlinear functions of the two port voltages, VGS and VDS, the output port voltage1. + IDS Gate VDS + VGS ‐ ‐ Source Drain + G VGS ‐ S IDS IGS The MOSFET as a two‐port D + VDS ‐ S Fig. 2.1.The MOSFET as a two-port. A first-order two-port representation of the MOSFET as a switch is shown in Fig. 2.2. The input voltage on the controlling gate appears across a capacitor 1 Mathematically this can be formulated as follows using an admittance matrix I GS y11 y12 VGS . I DS y21 y22 VDS 25 CG D + VDS ‐ RON S S OFF REGION + G VGS ‐ IDS OUTPUT VOLTAGE CG, the gate capacitor. The output voltage appears across a nonlinear resistor. In the ON state, it is denoted RON, while in the OFF state it is denoted ROFF. In theory ROFF is infinite. The input capacitor is a consequence of the MOSFET being a field-effect device. In Fig. 2.2, the MOSFET field of operation is divided into the OFF region and the ON region defined by a certain threshold voltage, VT. ON REGION RON ROFF CONTROL VOLTAGE Fig. 2.2. Simplified MOSFET two-port model and its regions of operation. A closer look at the output characteristic of the MOSFET reveals that RON is both voltage-controlled and nonlinear. The MOSFET output characteristic is plotted in Fig. 2.3 for two different gate voltages to illustrate this behavior. saturation region VDS OFF REGION IDSAT linear region OUTPUT VOLTAGE IDS SATURATION REGION LINEAR REGION CONTROL VOLTAGE Fig. 2.3. Nonlinear MOSFET behavior and the two regions of operation. 26 The graph reveals that the device behaves as resistor with resistance RON(VGS) for small drain voltages, but that the current through the device saturates for large drain voltages. Therefore the ON region of operation can be divided into two subregions, the linear region and the saturation region. The border line between these two regions of operation is given by the straight line VDS=VDSAT=VGS-VT. Piecewise linear (PWL) models approximating the real device behavior are often used, particularly for calculations by hand using pencil and paper. A piecewise linear MOSFET model uses a conductor GON to approximate the behavior in the linear region, and a constant-current source IDSAT to approximate the voltage-independent behavior in the saturation region. This model is illustrated in Fig. 2.4. In the context of a piecewise linear model, the more accurate nonlinear model can be seen as a “smoothing curve” between the linear region and the saturation region. While the nonlinear model saturates for VDS=VDSAT, the simplified piecewise linear model saturates for VDS=VDSAT/2. linear region IDSAT VDS OFF REGION saturation region OUTPUT VOLTAGE IDS SATURATION REGION IDS=IDSAT IDS=GON VDS LINEAR REGION CONTROL VOLTAGE Fig. 2.4. Piece-wise linear MOSFET model and its regions of operation. In the piecewise linear model, the drain current is given by the following simplified relationships G V I DS ON DS I DSAT VDS VDSAT / 2 VDS VDSAT / 2 (2.1) 27 In a piecewise linear model we use one two-port model to represent the MOSFET in the linear region, and another two-port model to represent the MOSFET in the saturation region. These two-port models are shown in Fig. 2.5. MOSFET saturation region, VDS>VDSAT/2 MOSFET linear region, VDS<VDSAT/2 drain gate + vGS CG GON - drain gate + vDS ‐ source + vGS ‐ CG + vDS ‐ IDSAT source Fig. 2.5. MOSFET two-port models for the linear and saturation regions. Example 3.1. Calculate the ON resistance RON of a fully ON MOSFET if it saturates at VDSAT=0.8 V and the saturation current is 640 A? Solution: The ON resistance is given by RON = 0.8/2/640 = 625 . According to the classical long-channel MOSFET model developed by William Shockley, the ON conductance and the saturation current is given by the following equations GON k VGS VT k 2 I DSAT VGS VT 2 , (2.2) where two new parameters k and VT have been introduced. Here, VT is the threshold voltage, i.e. the minimum gate voltage required to turn the MOSFET ON. The ON conductance is proportional to the gate overdrive voltage VGS-VT, often conveniently denoted VGT or VGST, while the saturation current obeys a square-law dependence. The parameter k contains both geometry and technology-dependent parameters according to the following model 28 k W W Cox k´, where "k prime"=Cox . L L (2.3) The geometry dependency is given by the MOSFET channel aspect ratio between the width, W, and the length, L. The aspect ratio can be defined by the circuit designer, while the technology parameter “k prime” is given by the manufacturer since it contains technology parameters such as the carrier mobility, and the oxide capacitance, Cox, per unit area. Example 3.2. Calculate the ON conductance GON of a fully ON MOSFET and the maximum current it can deliver or sink, given the following parameters: W/L=4, VDD=1,2 V, VT=0,3 V, Cox= 20 fF/m2, =100 cm2/Vs? Solution: The process parameter ‘k-prime’ is given by k’=Cox=200 A/V2. The device aspect ratio is W/L=4. The gate voltage overdrive for a fully ON device is given by VGST=VDD-VT=0.9 V. Hence, GON kVGST 4 200 0.9 720 A/V . k 2 2 I DSAT 2 VGST 4 100 0.9 324 A For VGS=VDD, the PWL breakpoint between the linear and saturation regions appears at VDS=324/720=0.45 V, which is half the gate voltage overdrive. The nonlinear saturation voltage is equal to the gate voltage overdrive, i.e. VDSAT=0.9 V. The complete long-channel MOSFET model derived by Shockley2 is given by I DS VDS k VGST 2 VDS k V 2 2 GST VDS VGST linear_region (2.4) VDS VGST saturation_region 2 W. Shockley, A Unipolar ‘Field‐Effect’ Transistor, Proc. IRE, 40, 1365‐1376, (1952) 29 2.1 Second-order effects For modern sub-micron short channel length MOSFETs there are a number of second-order effects that makes device behavior deviate from the ideal long-channel model. The three most important of these short-channel effects (SCE) are the mobility degradation, the velocity saturation, and the output conductance, an effect that is due to a combination of drain-induced barrierlowering (DIBL) and channel length modulation (CLM). 2.1.1 Mobility degradation The charge carrier mobility in a MOSFET is limited by an effect called scattering. The carriers are scattered by the silicon lattice, and by the silicon surface. The vertical electric field between the gate and the channel attracts the charge carriers to the surface thereby increasing the surface collision frequency and reducing the mobility. The higher the scattering rate the lower the mobility; it is like it is more difficult to walk fast on a crowded side-walk if you bump into the house wall. Chen et al. have found the following empirical models for the effective mobility of electrons and holes in a MOSFET channel eff ,n 540 1.85 V VTN 1 GS 0.54 tox and eff , p 185 V V 1 SG TP 0.34 tox , respectively, (2.5) where tox is the oxide thickness of the MOSFET gate capacitor. Example 3.3. Calculate the effective mobilities for 65 nm n-channel and pchannel MOSFETs for the two cases of VGS=0.5 and VGS=1.2 V. The threshold voltages are ±0.3 V. Assume tox=1.7 nm. Solution: eff ,n eff ,n 30 540 1.85 =300 cm 2 /Vs and eff , p 185 =80 cm 2 /Vs 0.8 1 0.34 1.7 1.85 =150 cm 2 /Vs and eff , p 185 = 50 cm2 /Vs 1.5 1 0.34 1.7 0.5 0.3 1 0.54 1.7 540 1.2 0.3 1 0.54 1.7 These examples clearly shows how the effective mobility is reduced to about half or even less when the gate voltage VGS is increased from the low bias voltage of 0.2 V used by the analog designer to the full-rail input voltage used by the digital designer in rail-to-rail logic designs. 2.1.2 Velocity saturation Like Ohm’s law, the square-law Shockley MOSFET model relies on a linear relationship between the charge carrier drift velocity and the electrical field along the channel. The slope of this relationship defines the mobility discussed in the previous section. However, beyond a certain critical field Ec, the velocity saturates at a maximum velocity vsat, approximately 107 cm/s. In a piecewise linear velocity model, E v eff vsat E Ec , E Ec (2.6) the critical field is given by EC=vsat/. The MOSFET saturation voltage in the case of velocity saturation can be derived by the following simplified reasoning. The current in a MOSFET channel is given by the mobile charge induced in the channel by the gate overdrive voltage across the MOSFET input capacitor, multiplied by the charge drift velocity. In the linear region of the piecewise linear MOSFET model, the drain current is given by the source charge multiplied by the carrier drift velocity, V I DS WCoxVGST eff DS . L (2.7) In the case of velocity saturation at the drain end of the channel, the saturation current is given by the drain charge multiplied by the carrier saturation velocity, I DSAT WCox VGS T VDSAT vsat . (2.8) In a piecewise linear model, the current in the linear region reaches the saturation level at the model breakpoint VDS=VDSAT/2. Equating the two expressions for the drain current at this breakpoint yields the following saturation voltage 31 VDSAT VGST VC , VGST VC (2.9) where VC=2LEC=2Lvsat/eff, and the following saturation current VC k k . I DS VGST VDSAT VGST 2 2 2 VGST VC (2.10) For negligible velocity saturation, i.e. for VB >> VGST, we can see that VDSAT approaches VGST, but for velocity saturation becoming a dominating phenomenon, i.e. for VB << VGST, VDSAT approaches VC. Example 3.4. Find the critical voltage VC for fully ON nMOS and pMOS transistors using the effective mobilities from example 3.3. Solution: Using the equation VC=2LEC=2Lvsat/ we obtain for low gate voltages, cm cm 2 50nm 107 2 50nm 107 s =0.33 V and V s =1.25 V VC n C p cm2 cm2 300 80 Vs Vs and for high gate voltages (VGST=0.9 V), cm cm 2 50nm 107 2 50nm 107 s =0.65 V and V s =2 V VC n C p cm2 cm2 150 50 Vs Vs These latter values for VGST=0.9 V correspond reasonably well with the values given by Weste & Harris in their example 2.4. The following square-law model will act as a smooth replacement for IDS=kVGSTVDS in the linear region V I DS kVGST VDS 1 DS 2VDSAT . (2.11) A typical output characteristic using the saturation voltages calculated in example 3.5 is shown in Fig. 2.6. From the graph it is obvious that the device is more of a linear device than a square-law device due to a combination of the velocity saturation and mobility roll-off effects. 32 Fig. 2.6. MOSFET output characteristics. Example 3.5. Find the nMOS and pMOS transistor saturation voltages for VGST=0.2 V and VGST=0.9 V using the critical voltages from example 3.4. V V Solution: Using the equation VDSAT GST C , we obtain VGST VC 0.2 0.33 0.2 1.25 VGST 0.2 V: VDSAT , n 0,125 V, and VDSAT , p 0,17 V 0.2 0.33 0.2 1.25 VGST 0.9 V: VDSAT , n 0.9 0.65 0.9 2 0,38 V, and VDSAT , p 0,62 V 0.9 0.65 0.9 2 We can see that for VGST=0.2 V the saturation voltage VDSAT is quite close to VGST (at least for the p-channel device, while for VGST=0.9 V it is not. It is also clear that values extracted for the parameter k at low gate voltages, for instance by using the method illustrated in Fig. 2.7, cannot be used for calculating the maximum current driving capability of the MOSFET using the long-channel square-law model. This is obvious from Fig. 2.8. Nevertheless, it can be concluded from the figures that the square-law Shockley model is quite useful for transconductance and voltage amplification estimates in analog designs where MOSFETs are biased in this low-bias region. 33 Fig. 2.7. MOSFET transfer characteristics. Fig. 2.8. MOSFET transfer characteristics. 2.1.3 Discussion and practical approach So, what is the main conclusion of this model discussion? Where has this discussion taken us? The analog designer, on the one hand, is often quite satisfied using the long channel square-law MOSFET model based on model parameters k and VT extracted at low values of VGS. The digital designer, on the other hand, is most interested in the maximum drain saturation current 34 ION that the MOSFET can deliver or sink for gate voltages equal to the supply voltage. In this region of operation, both mobility roll-off and velocity saturation are dominating effects in today’s short channel devices. Obviously, it is too complicated to handle both mobility roll-off and velocity saturation in first-order approximations. To our advantage is the fact that the mobility*VDSAT product varies quite slowly with VGS. This means that we can use the same low VGS values for model parameters k and VT as the analog designer in combination with an ‘effective’ critical voltage VC determined to yield the correct ION. It is a quite simple approach, the main disadvantage of which is that it will somewhat exaggerate the saturation region as shown in Fig. 2.9. Fig. 2.9. Comparison between MOSFET models. 2.1.4 DIBL and channel-length modulation (CLM) On top of the problem with these two second-order effects there is also the non-negligible problem of non-saturating currents in the saturation region. This short-channel effect is due to two physical phenomena: drain-induced 35 barrier-lowering (DIBL) and channel-length modulation (CLM). For hand calculations, the digital designer solves this problem by fitting his model to the average current for delay calculations determined at VDS=3VDD/4. This approach is illustrated in Fig. 2.10. For the analog designer, the problem is not that severe for bias calculations, but for small-signal analysis a non-zero output conductance, gDS, corresponding to the slope of the IDS vs. VDS curve must be added to the small-signal MOSFET model, as shown in Fig. 2.11. Fig. 2.10. Average model fitted to data for non-saturating drain currents. MOSFET saturation region, VDS>VDSAT drain gate + vGS, vgs CG IDSAT or gmvgs ‐ gds + vDS, vds ‐ source Fig. 2.11. MOSFET two-port model for non-saturating drain currents. 36 2.1.5 Subthreshold leakage As can be seen in Fig. 2.7, the device is not fully turned off below the threshold voltage, but there seems to be a subthreshold current flowing. This current is quite visible when the transfer characteristic is plotted in a semilogarithmic graph, as shown in Fig. 2.12. As indicated by this semilogarithmic graph, where the subthreshold current fits a straight line, the subthreshold turn-off behavior is exponential. Fig. 2.12. Semilogarithmic graph of the MOSFET transfer characteristic. The exponential behavior indicates to the device physicist that the subthreshold current is a diffusion current and not a drift current. The inverse of the slope of the straight line is called the subthreshold swing, S. Typical values for the subthreshold swing is around 100 mV per decade. Another performance parameter that becomes more and more important as technology and supply voltages scale is the ION/IOFF ratio3. On the one hand, the designer wants as high effective gate voltage overdrive, VGST=VDDVT, as possible. On the other hand, the threshold voltage should be as high as possible to ensure a low IOFF. For a typical subthreshold swing of 100 mV/decade, a 100 mV increase of the threshold voltage means a factor of ten reduction of the OFF leakage current. For a 65 nm device delivering an ON current of 1 mA, the OFF current is typically 50 nA. These numbers result in an ION/IOFF ratio of 20,000; a factor of ten less than shown in Fig. 2.12. 3 ION=IDS(VGS=VDS=VDD), IOFF=IDS(VGS=0, VDS=VDD). 37 2.2 MOSFET capacitances In this section we shall complete our simple MOSFET two-port model by adding the input and output capacitances. 2.2.1 Intrinsic gate capacitance Let us start by calculating the intrinsic gate capacitance. This is easily done knowing the MOSFET channel width W and length L, yielding CG WLC ox . (2.12) For simplicity, we placed this gate capacitance between the gate and source in the beginning of the chapter when we introduced the two-port model. These models are repeated in Fig. 2.13 for our convenience. MOSFET saturation region, VDS>VDSAT MOSFET linear region, VDS<VDSAT drain gate + vGS ‐ CG GON source drain gate + vDS ‐ + vGS ‐ CG IDSAT + vDS ‐ source Fig. 2.13. MOSFET two-port models for the linear and saturation regions. In reality, the situation is much more complicated since the distributed gateto-channel capacitance should be split between the source and the drain in a voltage-dependent way. In essence, the gate capacitance should be split equally between source and drain in the linear region, while the capacitance from gate to drain can be neglected in the saturation region. On the other hand, the capacitance to the source is reduced to 2/3CG in the saturation region due to the charge distribution in the channel, see Fig. 2.14. 2.2.2 Gate overlap and fringing field capacitances To make modeling even more complicated, we must also consider the parasitic capacitances due to the gate-to-source/drain overlap and the 38 MOSFET saturation region, VDS>VDSAT MOSFET linear region, VDS<VDSAT drain gate + vGS ‐ + vDS ‐ CG/2 CG/2 GON drain gate + vGS ‐ + vDS ‐ IDSAT 2CG/3 source source Fig. 2.14. More correct two-port models for the intrinsic gate capacitance. fringing field along the edges of the gate. These capacitances are illustrated in Fig. 2.15. CGSO Metal gate source STI CGDO W drain L STI Fig. 2.15. Side view of the gate overlap and fringing field capacitances. The gate overlap and fringing field parasitic capacitances are given by CGSO W C GSOL , CGDO W CGDOL , (2.13) where typically CGSOL=CGDOL= 0.2-0.4 fF/m. These parasitic capacitances should be added to the intrinsic gate capacitances. However, for hand calculations the existence of capacitances between the input and the output introduces unwanted complications. Therefore, in circuits where the output voltage is an amplified version of the input signal, vout=-Avin, the Miller theorem can be used to arrive at an equivalent circuit with capacitances only to ground. This is illustrated in Fig. 2.16. 39 In digital circuit applications, where the equivalent voltage amplification is equal to one, the gate to drain capacitance CGD results in an equivalent parasitic capacitance of 3CGDO at the input and an equivalent load of 2CGDO at the output. Since the intrinsic gate capacitance LCox per unit width as about 1 fF/m for the 65 nm node, the parasitic capacitance 3CGDOL per unit width is actually more than the missing third of the gate-to-source capacitance in the saturation region. Nevertheless, not to complicate matters more than necessary, let us agree on the simplified two-port model in Fig. 2.13. Of course, circuit simulators like SPICE contain more detailed capacitance models that also take the voltage dependence of the gate capacitance into account. MOSFET parasitic gate‐to‐drain capacitance drain gate + vin ‐ drain gate + CGDO vout=‐Avvin ‐ source MOSFET equivalent Miller capacitances + vin ‐ (1+A)CGDO + vout=‐Avin (1+1/A)CGDO ‐ source Fig. 2.16. The parasitic gate-to-drain capacitance and its equivalent Miller capacitances. Example 3.6. Calculate the gate capacitance per unit width of a 65 nm CMOS n-channel MOSFET device with an effective gate length of 50 nm given the following parameters: Cox=20fF/m2, CGSOL=CGDOL=0.2fF/m? Solution: The gate capacitance per unit width is given by CG’=WCox, yields CG’=1.0 fF/m. This is the gate capacitance per micron transistor width. The parasitic overlap and fringing field capacitances from the two edges of the MOSFET gate as seen from the input is equal to COVL=CGSOL+2CGDOL=0.6 fF/m, which is a non-negligible part of the total gate capacitance. Also, the parasitic input capacitance is about twice the missing third of the gate capacitance in the saturation region. 40 However, we will not change our MOSFET two-port model because of this since the capacitance values are rather rough estimates anyway as are the exact device geometries. 2.2.3 Source and drain parasitic junction capacitances In addition to the gate, the source and drain are also associated with capacitances. Like the gate fringing field and overlap capacitances, these capacitances are regarded as parasitic since they are not fundamental to MOSFET operation. However, they do impact circuit performance. The source and drain capacitances arise from the pn junctions between the source or drain and the body substrate. Hence, they are called CSB and CDB. They are illustrated in Fig. 2.17 and depend both on the junction bottom plate area and the junction perimeter. Hence, these capacitances are given by C SB WLS C j (W 2 LS )C jsw WC jswg . C DB WLD C j (W 2 LD )C jsw WC jswg MOSFET switch model (2.14) Channel width W D MOSFET symbol CDB GON LD channel length, L G CG S CSB LS Fig. 2.17. MOSFET switch model and layout. As indicated by the capacitance model, the source and drain junction capacitances consist of a bottom plate capacitance proportional to the source/drain area, WLS C j Cbottom _ plate WLD C j source , drain (2.15) 41 where Cj is the bottom plate junction capacitance per unit area and A=WLX is the bottom plate area. Also indicated by the capacitance model in (2.14) is the sidewall capacitance of the source/drain regions, W 2 LS C jsw WC jswg C sidewall W 2 LD C jsw WC jswg source , drain (2.16) where Cjsw is the sidewall capacitance due to the shallow trench isolation and Cjswg is the sidewall capacitance to the channel. In deep submicron processes below 0.35 m, where shallow trench isolation is used, the sidewall capacitance along the nonconductive trench tends to be much smaller than the sidewall capacitance facing the channel. A side view of the MOSFET and its parasitic junction capacitances is shown in Fig. 2.18. To further complicate modeling, the junction capacitances are voltage dependent as the decrease with increasing source/drain reverse bias. For the source it is not so much of a problem since it is usually grounded. However, for the drain it is more complicated since the drain voltage changes during charging and discharging of the MOSFET that occurs as a response to input gate voltage variations. LD LS Csidewall source Csidewall Metal gate drain W STI Cbottom Cbottom STI Fig. 2.18. Side view of the source and drain parasitic capacitances. Example 3.7. Calculate the source/drain capacitance of a 65 nm CMOS nchannel MOSFET device given the following parameters: W=1 m, LS=LD=0.125 m, Cj=1fF/m2, Cjswg= 0.36fF/m and Cjsw= 0.1 fF/m? 42 Solution: The source/drain bottom plate capacitance is C’bottom=0.125 fF/m channel width. The sidewall capacitance consists of a nonscalable part 2.LX.Cjsw= 0.025 fF, and a scalable part Cjswg+ Cjsw= 0.46fF/m. The total junction capacitance is then CSB=CDB=0.025+W.(0.125+0.46) fF, which for a one micron wide MOSFET accounts to a total capacitance of 0.61 fF. For a 100 nm wide MOSFET the junction capacitances reduce to 0.084 fF, i.e. 84 aF. The junction capacitances are voltage dependent according to the following model, C j (0) M 1 VSB / Vbi C j C j (0) 1 V / V M DB bi source , (2.16) drain where Vbi is the built-in potential of the junction. On top of this, modeling is even more complicated due to the fact that the capacitance parameters are different for n-channel and p-channel devices, and they are different for each of the bottom plate and sidewall capacitances. All this must be carefully considered when extracting model parameters for Spice simulations. However, for hand calculations we will use the zero-bias capacitance values. This is of course a rather conservative approach since we are then basing our estimates on capacitance values larger than the actual values, for instance during switching when the drain voltage is switching from one rail to the other. On the other hand, to some extent this conservative approach makes up for the output Miller capacitance from the gate overlap and fringing field. 2.3 Why do we need dynamic models? Digital designers need a dynamic MOSFET model for estimating the switching speed and propagation delay of the logic gates they are designing. The simplified piecewise linear current model we have presented in this chapter is good enough for preliminary and approximate hand calculations. It provides a rough estimation that usually less than a factor of two from the real value. In fact, accuracy can be quite good, particularly if the driving 43 capabilities and capacitances of the MOSFETs are calibrated to Spice simulations of some simple logic gates like two and three input NAND and NOR gates. For more accurate delay estimations circuit simulations must be performed using the Spice simulator where detailed MOSFET models are used (like the BSIM model developed at University of California at Berkeley with almost one hundred model parameters). A typical switching situation where we will have use of our dynamic MOSFET two-port model is shown in Fig. 2.19 where one MOSFET is seen charging and discharging the gate of another MOSFET. There will be more about switching of MOSFETs in chapter 4. VOUT M1 VIN M2 M1 two‐port model drain gate + VIN ‐ M2 two‐port model gate + CG IDSAT CDB driver VOUT ‐ CG load Fig. 2.19. Equivalent two-port model for one MOSFET charging/ discharging the gate capacitance of another MOSFET. 44