* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Lecture Notes Session 20

Time-to-digital converter wikipedia , lookup

Rotary encoder wikipedia , lookup

Multidimensional empirical mode decomposition wikipedia , lookup

Buck converter wikipedia , lookup

Schmitt trigger wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

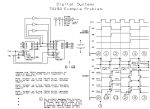

EE247 Lecture 20 • ADC Converters – ADC architectures (continued) – Comparator architectures • Latched comparators • Latched comparators incorporating preamplifier • Sample-data comparators – Offset cancellation – Comparator architecture examples – Flash ADC sources of error • Sparkle code • Meta-stability EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 1 Flash Converter • B-bit flash ADC: – DAC generates all possible 2B -1 levels – 2B-1 comparators compare VIN to DAC outputs – Comparator output: • If VDAC< VINÆ 0 • If VDAC > VINÆ1 VREF D A C VIN fs 2B-1ÆB Encoder Digital Output – Comparator outputs form thermometer code – Encoder converts thermometer to binary code EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 2 VIN Flash ADC Converter Example: 3-bit Conversion Thermo VIN VREF VREF me t code er fs 0 0 B-bits 1 1 0 Encoder 1 1 1 1 1 Time EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 3 Flash Converter VIN – Half cycleÆ VIN & VDAC comparison – Half cycleÆ 2B-1 to B encoding • High complexity: 2B-1 comparators fs R/2 R R .. .. . Encoder • Very fast: only 1 clock cycle per conversion VREF Digital Output R R B-bits • High capacitance @ input node EECS 247 Lecture 20: Data Converters R/2 Thermometer code © 2005 H.K. Page 4 Folding Converter MSB ADC VIN Digital Output LSB ADC Folding Circuit • Significantly fewer comparators than flash • Fast • Nonidealities in folder limit resolution to ~10-bits EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 5 fs T/H ADC fs + T/4 • Extremely fast: Limited by speed of T/H ADC fs + 2T/4 ADC • Accuracy limited by mismatch in individual ADCs (timing, offset, gain, …) EECS 247 Lecture 20: Data Converters fs + 3T/4 Digital Output VIN 4fs Serial / Parallel Conversion Time Interleaved Converter ADC © 2005 H.K. Page 6 Residue Type ADC Partial Digital Output VIN Error coarse ADC (1 ... 6 Bit) DAC T/H & Gain (optional) • Quantization error output (“residuum”) enables cascading for higher resolution • Great flexibility for stages: flash, oversampling ADC, … • Optional T/H enables parallelism (pipelining) • Fast: one clock per conversion (with T/H), latency EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 7 Pipelined ADC VIN Stage 1 B1 Bits Stage 2 B2 Bits Stage K Bk Bits Digital Correction Logic Digital output up to (B1 + B2 + ... + )Bk) Bits • • • • Approaches speed of flash, but much lower complexity One clock per conversion, but K clocks latency Efficient digital calibration possible Versatile: from 16Bits / 1MS/s to 14Bits / 100MS/s EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 8 Algorithmic ADC Start of conversion VIN Digital Output Shift Register & Correction Logic coarse ADC 2B DAC T/H (1 ... 6 Bit) Residue • Essentially same as pipeline, but a single stage is used for all partial conversions • K clocks per conversion EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 9 Oversampled ADC fs VIN fs/M Digital Decimation Filter H(z) Digital Output DAC • Hard to comprehend … “easy” to build • Input is oversampled (M times faster than output rate) • Reduces Anti-Aliasing filter requirements and capacitor size • Accuracy independent of component matching • Very high resolution achievable (> 20 Bits) EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 10 Resolution [Bit] 16 14 12 10 8 B+ 1) Flash, Pipeline~1 to 2 18 Su ce ss Appcro 2 nd ximivaeti Ov Or on~B ers der am 1ple Bit d~ 2 (0.4 Throughput Rate Comparison B S ~ al eri 2 6 4 2 0 0 10 1 10 2 10 3 10 4 10 5 10 Clock Cycles per Conversion EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 11 Speed-Resolution Map [www.v-corp.com] EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 12 High-Speed A/D Converters • Flash Converter – Comparator design considerations – Binary Encoder • Interpolation • Folding • Pipelined ADCs EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 13 Flash Converter VREF • Very fast: only 1 clock cycle per conversion VIN fs R/2 R • High input capacitance R .. .. . Encoder • High complexity: 2B-1 comparators Digital Output R R R/2 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 14 Flash Converter Example: 8-bits ADC VREF • 8-bitsÆ 255 comparators VIN fs R/2 R • VREF=1V Æ 1LSB=4mV .. .. . • DNL<1/2LSB Æ Comparator input referred offset < 2mV Encoder R Digital Output R R • 2mV =6σoffset R/2 Æ σoffset < 0.33mV EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 15 Flash ADC Converter Example: 8-bits ADC (continued) Æ 1σOffset < 0.33mV • Let us assume in the technology used: – Voffset-per-unit-sqrt(WxL)=5mV V0 ffset = 5mV = 0.33mV W ×L → W × L = 230 μ 2 2 → CGS = CoxW × L = 765 fF 3 → Total input capacitance: 255 × 0.765 = 195 pF ! Assuming: Cox = 5 fF / μ 2 – Issues: • Si area quite large • Large input capacitance • Since depending on input voltage different number of comparator input transistors would be on/off- input capacitance varies as input varies Æ Nonlinear input capacitance could give rise to signal distortion Ref: M. J. M. Pelgrom, A. C. J. Duinmaijer, and A. P. G. Welbers, "Matching properties of MOS transistors," IEEE Journal of Solid-State Circuits, vol. 24, pp. 1433 - 1439, October 1989. EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 16 Flash ADC Converter Example (continued) Trade-offs: – Allowing larger DNL of 1LSB instead of 0.5LSB: • Increases the maximum allowable input-referred offset voltage by a factor of 2 • Decreases the required device WxL by a factor of 4 • Reduces the input device area by a factor of 4 • Reduces the input capacitance by a factor of 4! – Reducing the ADC resolution by 1-bit • Increases the maximum allowable input-referred offset voltage by a factor of 2 • Decreases the required device WxL by a factor of 4 • Reduces the input device area by a factor of 4 • Reduce the input capacitance by a factor of 4 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 17 Flash Converter Assumption: DNL=0.5LSB Note: Depending on min acceptable yield, numbers associated with 2σ to 7σ offset voltage Maximum Comparator Voffset [mV] Comparator Maximum Offset versus ADC Resolution 102 VREF=2V 10 VREF=1V 1 10-1 4 EECS 247 Lecture 20: Data Converters 6 8 ADC Resolution 10 © 2005 H.K. Page 18 Voltage Comparators + Vin + - - Vout (Digital Output) Function: compare the instantaneous value of two analog signals Important features: • • • • • • • • Maximum clock rate fs Æ settling time, slew rate, small signal bandwidth ResolutionÆ gain, offset Overdrive recovery Input capacitance (and linearity of input capacitance!) Power dissipation Common-mode rejection Kickback noise … EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 19 Voltage Comparator Architectures Comparator architectures • High gain amplifier with differential analog input & single-ended large swing output – Output swing compatible with driving digital logic circuits – Open-loop amplificationÆ no frequency compensation required – Precise gain not required • Latched comparators; in response to a strobe, input stage disabled & digital output stored in a latch till next strobe – Two options for implementation : • Latch-only comparator • Low-gain amplifier + a high-sensitivity latch • Sample-data comparators – T/H input – Offset cancellation EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 20 CMOS Latched Comparators Comparator amplification need not be linear Æcan use a latch Æ regeneration Æ Amplification + positive feedback EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 21 CMOS Latched Comparators Latch can be modeled as a single-pole amp + positive feedback EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 22 CMOS Latched Comparator Delay g mV = V dV +C RL dt 1 ⎛ ⎜1 − g R m L ⎝ gm ⎛ 1 1− C ⎜⎝ g m RL gm C dV ⎞ ⎟V = dt ⎠ V2 1 ⎞ t2 ⎟ ∫t1 dt = ∫V 1 V dV ⎠ Latch Delay: C ⎛ 1 gm ⎜ 1 − 1 ⎜ g m RL ⎝ For g m RL >> 1 τ D = t2 − t1 = τD ≈ ⎞ ⎛ V2 ⎞ ⎟ ln ⎜ V ⎟ ⎟ ⎝ 1⎠ ⎠ C ⎛ V2 ⎞ ln g m ⎜⎝ V1 ⎟⎠ EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 23 Latch-Only Comparator • Problem with latch-only comparator topology: – High input-referred offset voltage (as high as 100mV!) • Solution: –Use preamplifier to amplify the signal and reduce overall input-referred offset EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 24 Comparator Preamplifier Gain-Speed Tradeoffs • Amplifier maximum Gain-Bandwidth product for a given technology, typically a function of maximum device ft f u =unity gain frequency, f 0 = −3dB frequency & τ 0 = settling time f0 = fu = Apreamp Magnitude For example: f0 = τ0 fu Apreamp = 1GHz = 100 MHz 10 Av fu=10-2000MHz 1 = = 1.6n sec 2π f 0 f0 fu Frequency Æ Tradeoff: • To reduce the effect of latch offset Æ high preamp gain desirable • Fast comparator Æ low preamp gain EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 25 Pre-Amplifier Tradeoffs fs Vi+ Vi- • Example: – – – – – Av Latch Do+ Do- Preamp Latch offset Preamp DC gain Preamp input-referred latch offset Input-referred preamplifier offset Overall input-referred offset 50 to 100mV 10X 5 to 10mV 2 to 10mV 5.5 to 14mV Æ Overall input-referred noise reduced by ~7 to 9X Æ ~extra 3-bit resolution! EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 26 CMOS Latched Comparator Including Preamplifier Delay Latch delay found previously: C ⎛ V2 ⎞ ln g m ⎜⎝ V1 ⎟⎠ Assuming gain of Av for the preamplifier: τD ≈ τD ≈ C ⎛ V0 ⎞ ln Av g m ⎜⎝ Vin ⎟⎠ EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 27 Latched Comparator Including Preamplifier Example VDD M5 M3 M4 M6 - Vo + CLK Preamplifier gain: M3 M3 g M 1 (VGS − Vth ) Av = mM 3 = gm (VGSM 1 − VthM 1 ) + Vin - M1 M2 M9 bias M8 M7 Comparator delay: τD ≈ C ⎛ V0 ⎞ ln ⎜ Av ⎟ g m ⎝ Vin ⎠ EECS 247 Lecture 20: Data Converters Preamp Latch © 2005 H.K. Page 28 Comparator Dynamic Behavior Comparator Reset Comparator Decision CLK TCLK τdelay vOUT EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 29 Comparator Resolution CLK VIN =10mV 1mV vOUT 0.1mV 10μV Δt = (gm/C).ln(Vin1/Vin2) EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 30 Comparator Voltage Transfer Function Non-Idealities Vout ε -0.5LSB 0.5LSB Vin VOffset VOffset Æ Comparator offset voltage ε Æ Meta-Stable region (output ambiguous) EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 31 Latched Comparator fs Vi+ Vi- Av Do+ Latch Do- Preamp • • • • • • • • Clock rate fs Resolution Overload recovery Input capacitance (and linearity!) Power dissipation Common-mode rejection Kickback noise … EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 32 Comparators Overdrive Recovery Linear model for a single-pole amplifier: UÆ amplification after time ta During reset amplifier settles exponentially to its zero input condition with τ0=RC Assume Vm Æ maximum input normalized to 1/2lsb (=1) EECS 247 Lecture 20: Data Converters Example: Worst case input/output waveforms Æ Limit output voltage swing by 1. Passive clamp 2. Active restore 3. Low gain/stage © 2005 H.K. Page 33 Comparators Overdrive Recovery Limiting Output Clamp Adds parasitic capacitance EECS 247 Lecture 20: Data Converters Active Restore After outputs are latchedÆ Activate φR & equalize output nodes © 2005 H.K. Page 34 CMOS Comparator Example •Flash ADC: 8bits, +-1/2LSB INL @ fs=15MHz (Vref=3.8V, LSB~15mV) •No offset cancellation Ref: A. Yukawa, “A CMOS 8-Bit High-Speed A/D Converter IC,” JSSC June 1985, pp. 775-9 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 35 Comparator with Auto-Zero Ref: I. Mehr and L. Singer, “A 500-Msample/s, 6-Bit Nyquist-Rate ADC for Disk-Drive Read-Channel Applications,” JSSC July 1999, pp. 912-20. EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 36 Auto-Zero Implementation Ref:I. Mehr and L. Singer, “A 55-mW, 10-bit, 40-Msample/s Nyquist-Rate CMOS ADC,” JSSC March 2000, pp. 318-25 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 37 Comparator Example •Variation on Yukawa latch used w/o preamp •No dc power when φ high •Good for low resolution ADCs •M11 & M12 added to vary comparator threshold •To 1st order, for W1=W2 & W11=W12 Vthlatch = W11/W1 x VR where VR=VR+ - V RRef: T. B. Cho and P. R. Gray, "A 10 b, 20 Msample/s, 35 mW pipeline A/D converter," IEEE Journal of Solid-State Circuits, vol. 30, pp. 166 - 172, March 1995 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 38 Comparator Example •Used in a pipelined ADC with digital correction Æno offset cancellation •Note differential reference •M7, M8 operate in triode region •Preamp gain ~10 •Input buffers suppress kick-back Ref: S. Lewis, et al., “A Pipelined 5-Msample/s 9-bit Analog-to-Digital Converter” IEEE JSSC ,NO. 6, Dec. 1987 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 39 Bipolar Comparator Example •Used in 8bit 400Ms/s & 6bit 2Gb/s flash ADC •Signal amplification during φ1 high, latch operates when φ1 low •Input buffers suppress kickback & input current •Separate ground and supply buses for front-end preamp Æ kick-back noise reduction Preamp Latched Comparator Ref: Y. Akazawa, et al., "A 400MSPS 8b flash AD conversion LSI," IEEE International Solid-State Circuits Conference, vol. XXX, pp. 98 - 99, February 1987 Ref: T. Wakimoto, et al, "Si bipolar 2GS/s 6b flash A/D conversion LSI," IEEE International Solid-State Circuits Conference, vol. XXXI, pp. 232 - 233, February 1988 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 40 Flash Converter Sources of Error VIN VREF fs R/2 • Comparator input: R R Encoder .. .. . Digital Output R R – Offset – Nonlinear input capacitance – Kickback noise (disturbs reference) – Signal dependent sampling time • Comparator output: R/2 – Sparkle codes (… 111101000 …) – Metastability EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 41 Typical Flash Output Encoder Binary Output (negative) VDD b3 b2 b1 b0 0 0 b3 b2 b1 b0 OutputÆ 0 1 1 1 0 1 1 • Thermometer code Æ 1-of-n decoding • Final encoding Æ NOR ROM 0 1 0 1 Thermometer to Binary encoder ROM EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 42 Sparkle Codes VDD Erroneous 0 (comparator offset?) b3 b2 b1 b0 0 Correct Output: 1000 1 1 0 0 Erroneous Output: 0000 1 1 0 1 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 43 Sparkle Tolerant Encoder 0 0 0 1 1 0 0 0 1 0 Protects against a single sparkle. Ref: C. Mangelsdorf et al, “A 400-MHz Flash Converter with Error Correction,” JSSC February 1990, pp. 997-1002 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 44 Meta-Stability Different gates interpret metastable output X differently 0 0 Correct output: 1000 Erroneous output: 0000 0 1 X Solutions: –Latches (high power) –Gray encoding 1 1 0 1 Ref: C. Portmann and T. Meng, “Power-Efficient Metastability Error Reduction in CMOS Flash A/D Converters,” JSSC August 1996, pp. 1132-40 EECS 247 Lecture 20: Data Converters © 2005 H.K. Page 45 Gray Encoding Thermometer Code Gray Binary T1 T2 T3 T4 T5 T6 T7 G3 G2 G1 B3 B2 B1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 1 1 0 0 0 0 0 0 1 1 0 1 0 1 1 1 0 0 0 0 0 1 0 0 1 1 1 1 1 1 0 0 0 1 1 0 1 0 0 1 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 1 1 0 1 0 1 1 1 0 1 1 1 1 1 1 1 1 0 0 1 1 1 • Each Ti affects only one Gi Æ Avoids disagreement of interpretation by multiple gates Protects also against sparkles Follow Gray encoder by (latch and) binary encoder • • EECS 247 Lecture 20: Data Converters G1 = T1T3 + T5 T7 G2 = T2 T6 G3 = T4 © 2005 H.K. Page 46